Fターム[5F038AC05]の内容

半導体集積回路 (75,215) | キャパシタ (4,915) | 構造 (2,824) | 電極領域又は電極部分 (2,206) | 多結晶電極、金属電極 (1,364)

Fターム[5F038AC05]に分類される特許

141 - 160 / 1,364

半導体装置

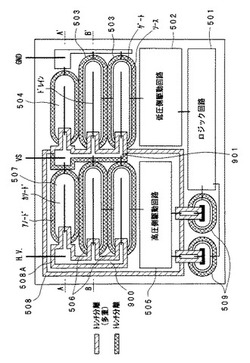

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

容量素子の製造方法

【課題】基板上に耐圧が異なる容量素子を共通の工程で形成する際に、基板上に残渣を残さないようにする。

【解決手段】基板10の上に半導体不純物がドープされた第1ポリシリコン層40を形成し、第1ポリシリコン層40の上にCVD法により第1酸化膜41を層状に堆積する(図2(a))。これにより、1回目の酸化で第1酸化膜41を第1ポリシリコン層40の粒界部に入り込ませないようにする。そして、第1酸化膜41を第1ボトム膜24にパターニングした後(図2(b))、第1ポリシリコン層40の上に第2酸化膜42を形成する(図2(c))。2回目の酸化は短時間で終わるので、第1ポリシリコン層40の増速酸化が進行する前に第2酸化膜42の形成が完了する。このため、第1ポリシリコン層40をエッチングする際に第2酸化膜42の一部がマスクとならないようにすることができる。

(もっと読む)

固体撮像装置、および、その製造方法、電子機器

【課題】撮像画像の画像品質、装置の小型化、装置の信頼性、製造効率などの各特性について向上させる。

【解決手段】複数の転送電極31が間を隔てて垂直方向yに並ぶように単一の導電材料層313を加工して形成する。また、第1キャパシタ電極C11および第2キャパシタ電極C21について、転送電極31へ加工される導電材料層313から形成する。

(もっと読む)

半導体装置

【課題】容量素子の配置による容量値の差を抑制すること。

【解決手段】第1の方向に延伸する第1配線12aと、前記第1配線と絶縁体を介し対向し設けられた第2配線14aと、を備える第1容量素子22と、前記第1配線と電気的に接続され前記第1方向に垂直な第2方向に延伸し設けられた第3配線16aと、前記第2配線と電気的に接続され前記第3配線と絶縁体を介し対向し設けられた第4配線18aと、を備える第2容量素子24と、を具備し、前記第1配線、前記第2配線、前記第3配線および前記第4配線は同じ配線層に設けられ、前記第1配線と前記第2配線とが対向する長さと、前記第3配線と前記第4配線とが対向する長さとは等しい半導体装置。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】直列に複数個接続されたそれぞれのMISFETQN1〜QN5のソース領域とドレイン領域の間に、ソース領域の電位を基準としてドレイン領域に正電圧を印加する場合と、ソース領域の電位を基準としてドレイン領域に負電圧を印加する場合のいずれの状態においても、ソース領域の電位とドレイン電極の電位が同電位の状態よりも容量が減少する電圧依存性を持つ歪補償用容量回路CAPC2が接続されている。

(もっと読む)

半導体装置及びその内部回路の制御方法

【課題】従来の半導体装置は、チップ面積を抑制しながら内部電源電圧の変動を抑制することができなかった。

【解決手段】本発明の半導体装置は、電源電圧の電圧値を他の電圧値に変換して内部電源電圧を生成する第1の電源回路PWR0、第2の電源回路PWR1と、第1の配線MT02を介して第1の電源回路PWR0から内部電源電圧VDL0の供給を受ける第1の内部回路MA0と、第2の配線MT12を介して第2の電源回路PWR1から内部電源電圧VDL1の供給を受ける第2の内部回路MA1と、第1の配線MT02と第2の配線MT12とを互いに接続するブロック間配線MT3と、第1の内部回路MA0と第2の内部回路MA1が同時に動作する期間の長さを制御する制御回路CNT0、CNT1と、を有する。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

半導体集積回路装置

【課題】設計工数をほとんど掛けないで、CMP対策及び短時間光アニール対策の両対策に最適化されたダミーパターンを有する半導体集積回路装置を提供すること。

【解決手段】基板上に、メモリマクロ領域10及び機能回路領域20を有する半導体集積回路装置1において、機能回路領域20間、及び、メモリマクロ領域10と機能回路領域20との間に配置されるとともにダミーパターン41を含むダミーパターン領域40を備え、ダミーパターン41は、前記メモリセルアレイ領域におけるメモリセルパターン11の拡散層12、13及びゲート電極14と同等のパターンであり、ダミーパターン領域40におけるダミー拡散層42、43及びダミーゲート電極44の面積率は、メモリセルアレイ領域における拡散層12、13及びゲート電極14の面積率と同等以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供する。比抵抗の増大なしに信頼性の高い配線を有する半導体装置を提供する。

【解決手段】半導体基板表面上に形成された電極を含み、前記電極が、配向性を有する導電体層からなり、前記電極に加え、

下式

M1xM21-x

M1:Au、Pt、Ir、Pd、Os、Re、Rh、Tu、Cu、Co、Fe、Ni、V、Cr

M2:Ta、Ti、Zr、Hf、W、Y、Mo、Nb

で表されるアモルファスまたは微結晶からなるバリア層を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置

【課題】MIMキャパシタの耐圧を高めることが可能な半導体装置を提供する。

【解決手段】半導体基板上に形成される下部電極層と、この下部電極層上に積層される誘電体層22と、この誘電体層上に積層される上部電極層23とで構成されるMIMキャパシタと、このMIMキャパシタの上部電極層に対して、接続角度が90度より大きくなるように線幅を広くして接続される第1の配線層パターン12と、前記MIMキャパシタの下部電極層に対して、接続角度が90度より大きくなるように線幅を広くして接続される第2の配線層パターン13a、13bと、を有する。

(もっと読む)

半導体装置及び製造方法

【課題】少ない層間接続プロセス工程数で、コンタクト部分の面積を小さくすることのできる半導体装置及び製造方法を提供する。

【解決手段】多層導体配線10は、スルーホール15は、導体13の一部は、ひさし部13Cとしてスルーホール15の内側に露出する。そして、スルーホール15のスルーホール用孔の内側に埋め込まれた埋め込み金属16とひさし部13Cとで、側面コンタクト構造を形成することができる。

(もっと読む)

半導体集積回路装置

【課題】可変容量範囲が広く、単位面積当たりの容量値が大きいMOS型バラクタ素子を備えた半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、P型基板PSubの表面にNチャネルトランジスタ1、Pチャネルトランジスタ2及びMOS型バラクタ素子3を設ける。そして、MOS型バラクタ素子3のゲート絶縁膜14を、Nチャネルトランジスタ1及びPチャネルトランジスタ2のゲート絶縁膜4よりも薄くする。また、MOS型バラクタ素子3のウエル端子Vbとゲート端子Vgとの間に印加するゲート電圧の最大値を、Nチャネルトランジスタ1及びPチャネルトランジスタ2に印加するゲート電圧の最大値よりも低くする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、製造コストの増加を抑制可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板部10、誘電体膜22、再配線24、上部電極25、絶縁膜26、及び外部接続端子28を有する。半導体基板部10は、回路が形成され、回路にそれぞれ接続される下部電極15、上部電極パッド16、接続パッド17、18を上面に有する。誘電体膜22は、下部電極15を被い、上部電極パッド16、接続パッド17、18の上面に達する開口部を有する。再配線24は、一部の接続パッド17、18に電気的に接続される。上部電極25は、誘電体膜22を介して下部電極15の上面に対向して配置され、上部電極パッド16に接続され、再配線24を含む。絶縁膜26は、誘電体膜22、再配線24、及び上部電極25を被う。外部接続端子28は、絶縁膜26を貫通し再配線24に接続され、絶縁膜26の上面から露出する。

(もっと読む)

半導体装置

【課題】線形性の悪化を抑制可能な抵抗回路を有する半導体装置を提供する。

【解決手段】アナログ信号が入力される入力端子と、ドレインがこの入力端子に接続され、ゲートが抵抗36の一端に接続されたトランジスタ31、ドレインがトランジスタ31のソースに接続され、ゲートが抵抗36の他端に接続され、ソースが接地されたトランジスタ33、トランジスタ31のドレインとゲートの間に接続されたコンデンサ35、並びに抵抗36の他端及びトランジスタ33のゲートと接続され、一定の電圧を供給する電圧供給回路38を有する抵抗回路17とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】高電圧仕様の受動素子と低電圧仕様の容量素子とを備える半導体装置の製造方法であって、低電圧仕様の容量素子の容量を確保できると共に、高電圧仕様の受動素子の当該高電圧仕様に対する耐圧を確保すると共に、製造時に高電圧仕様の受動素子の特性が変動することを防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板102上に絶縁膜116bを上部に有する下部電極110bと絶縁膜116aを上部に有する下部電極110aとを形成し、下部電極110b上の絶縁膜116bの膜厚を薄くし、半導体基板102上にゲート電極144を形成し、膜厚を薄くした第1の絶縁膜116b上に上部電極140を形成し、ゲート電極144および上部電極140を形成した後、全面に絶縁膜を形成し、絶縁膜を異方性エッチングしてゲート電極144の側面にサイドウォール148を形成する。

(もっと読む)

半導体装置

【課題】MEMSキャパシタとその制御用集積回路を反りの抑えられた1枚の基板上に有する半導体装置を提供する。

【解決手段】貫通孔を含む貫通孔領域を有する基板と、前記基板の上方のMEMSキャパシタと、前記MEMSキャパシタの下方の前記MEMSキャパシタの制御用集積回路とを有する半導体装置を提供する。前記制御用集積回路は、前記基板上のトランジスタを含む。前記MEMSキャパシタの真下の前記基板上の領域と前記貫通孔領域とは、少なくとも一部において重なる。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

141 - 160 / 1,364

[ Back to top ]