Fターム[5F038BH20]の内容

Fターム[5F038BH20]に分類される特許

1 - 20 / 65

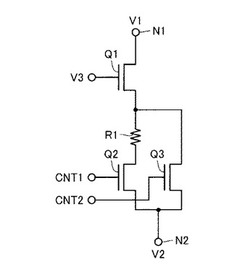

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

配線構造

【課題】クラックからの水分侵入に起因する金属配線端面の腐食防止、あるいは金属配線端面の腐食が生じている場合でも該腐食が液晶表示装置を駆動する液晶表示部分を構成するゲート線等の金属配線にまで到達することを防止する技術を提供する。

【解決手段】基板の上に、複数の金属配線が同一平面上に形成され、金属配線の上に絶縁膜が形成された積層構造を有し、切り出し加工により切断端面が露出している第1の金属配線を有する配線構造であって、

第1の金属配線の線幅をX(μm)、

第1の金属配線の長さをY(μm)としたとき、

(1)若しくは(2)、および/または下記(3)の要件を満足することを特徴とする配線構造。

(1)X≦20μm

(2)X>20μmのときは、Y≧10X−160、

(3)第1の金属配線の切断端面から、第1の金属配線に隣接する第2の金属配線までの間において、第1の金属配線は絶縁膜の存在しない領域Zを有する。

(もっと読む)

半導体集積回路

【課題】同一のデータを保持する3個以上のフリップフロップ回路と多数決論理回路を備えた半導体集積回路において、放射線の照射等により隣接する複数のフリップフロップ回路が同時に影響を受けてもソフトエラーの発生しにくい半導体集積回路を提供する。

【解決手段】保持するデータが、第1の論理値から第2の論理値へ遷移しやすく第2の論理値から第1の論理値には遷移しにくい特性を有する第1のフリップフロップ回路と、第2の論理値から第1の論理値へ遷移しやすく第1の論理値から第2の論理値には遷移しにくい特性を有する第2のフリップフロップ回路と、を第1のフリップフリップ回路同士及び第2のフリップフロップ回路同士が隣接して配置されないように、第1のフリップフロップ回路と第2のフリップフロップ回路が交互に配置されているレイアウトパターンを有する。

(もっと読む)

剥離テスト装置及び剥離テスト方法

【課題】剥離が発生した段階を知ることのできるテスト方法の提供。

【解決手段】前記複数の剥離補強ブロック2−1,2,3,4の各々は、複数の配線層に形成された配線群と、前記複数の配線層間で前記配線群を電気的に接続する、導体ホールとを備える。前記テスト回路1は、前記複数の剥離補強ブロックに対応して設けられた、複数のデータ保持回路と、前記複数の剥離補強ブロックの各々の一端に、テスト信号を供給する、テスト信号供給端と、前記複数のデータ保持回路に接続された、不揮発性の記憶回路とを備える。前記複数のデータ保持回路の各々は、対応する前記各剥離補強ブロックの他端から前記テスト信号に応じて出力される信号をテスト結果データとして保持する。前記不揮発性の記憶回路は、前記各データ保持回路に保持された前記テスト結果データを、前記各データ保持回路と対応付けて記憶するように、前記各データ保持回路と接続されている。

(もっと読む)

抵抗素子及びその製造方法

【課題】 従来のポリシリコン層を抵抗層とする抵抗素子は、抵抗素子のシート抵抗を例えば10MΩ/□以上に高くしたい場合、所望のシート抵抗が得られない問題があった。この原因は、製造工程中にポリシリコン層上の絶縁膜が帯電することが考えられ、このため設計値より2桁以上も低い値となってしまっていた。また、同一ウエハ内であっても抵抗素子毎に抵抗層のばらつきが大きくなる問題があった。

【解決手段】 ポリシリコン層を抵抗層とする抵抗素子において、抵抗層を被覆する絶縁膜の上に、保護層を設ける。保護層は金属層であり、抵抗素子の配線層や、電極等の金属層と同一金属層で形成できる。保護層は、ポリシリコン層の曲折部が露出するパターンに設ける。また、保護層に固定電位を印加する。固定電位に応じて、異なるシート抵抗が得られる。

(もっと読む)

半導体チップ用受動層、半導体装置

【課題】チップ一体型パッケージ、半導体装置を提供する。

【解決手段】半導体基板12上に積層した絶縁層14と、前記絶縁層14に横倒しに埋め

込んだ態様で形成され、前記半導体基板12に形成された回路または外部回路と電気的に

接続するソレノイド型のインダクタ28と、前記絶縁層14において前記インダクタ28

の両端の開口部28aを塞ぐ位置に埋め込んだ態様で形成した一対の金属部材(金属膜3

4、金属板35)と、を有することを特徴とする。

(もっと読む)

SOI構造シングルイベント耐性のNAND素子、及びNOR素子

【課題】高いシングルイベント耐性を有するNAND素子、NOR素子を提供する。

【解決手段】チャネルが並列に接続された第1のpチャネルMOSトランジスタ及び第2のpチャネルMOSトランジスタと、チャネルが直列に接続された第1のnチャネルMOSトランジスタ及び第2のnチャネルMOSトランジスタと、が第1の電圧源側に接続されたノードから第2の電圧源側に接続されたノードに向かって直列にSOI構造の基板上で接続され、それらのトランジスタのそれぞれに対して、それとゲート同士が相互に接続された同じ導電型のチャネルのMOSトランジスタがチャネルが直列に更に接続された二重化構造を有する。

(もっと読む)

半導体集積回路

【課題】論理ゲートを構成するトランジスタの特性劣化を抑制する。

【解決手段】半導体集積回路70には、マルチプレクサ1、信号発生回路2、制御回路3、m個のインバータINV1乃至m列、n個の2入力NOR回路NOR1乃至n、縦続接続されるn個の2シフトレジスタSR1乃至nが設けられる。制御回路3は、クロック信号が供給される通常動作ときにディセーブル状態の制御信号Sctを生成し、クロック信号が供給されない通常動作以外のときにイネーブル状態の制御信号Sctを生成する。マルチプレクサ1は、クロック信号Sclkと信号発生器2から出力される低周波信号Ssgが入力され、制御信号Sctがディセーブル状態の時インバータINV1乃至m列にクロック信号Sclkを供給し、制御信号Sctがイネーブル状態の時インバータINV1乃至m列に低周波信号Ssgを供給する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、実動作に用いられる信号遅延パスにおける経年劣化の検出を可能とすること。

【解決手段】半導体集積回路装置は、複数の信号遅延パスと、当該複数の信号遅延パスの間の遅延量の大小関係を計測してメモリに格納するとともに、当該複数の信号遅延パスについて計測された遅延量の大小関係と当該メモリに格納された遅延量の大小関係とが一致するか否かを判定し、両者が一致しない場合には、当該複数の信号遅延パスのいずれかにおいて遅延故障が生じた旨を出力する遅延故障検出回路と、を有している。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な高い動作電圧を有するN型およびP型トランジスタ、ならびに適切な低い動作電圧を有するN型およびP型トランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板2上に形成されたHVNトランジスタ10と、HVPトランジスタ20と、LVNトランジスタ30と、LVPトランジスタ40と、抵抗素子50を有する。LVNトランジスタ30は、絶縁体層31a、La2O3層31bおよび高誘電率絶縁体層31cからなるゲート絶縁膜31と、金属層32aおよび半導体層32bからなるゲート電極32を有する。LVPトランジスタ40は、絶縁体層41a、Al2O3層41bおよび高誘電率絶縁体層41cからなるゲート絶縁膜41と、金属層42aおよび半導体層42bからなるゲート電極41を有する。抵抗素子50は、絶縁体材料からなる第1の層51と、半導体材料からなる第2の層52を有する。

(もっと読む)

コンタクトホール側壁の抵抗値測定方法

【課題】コンタクトホール側壁に付着した有機膜の抵抗値を簡単且つ的確に測定する。

【解決手段】基板20上に形成された下部電極であるポリSi膜22aと、このポリSi膜22a上にBPSG膜23を介して形成された中間電極であるポリSi膜24aと、このポリSi膜24a上にBPSG膜25を介して選択的に形成されたホトレジスト膜からなるホールパターン26aと、このホールパターン26aをマスクにしてプラズマエッチングにより形成され、ポリSi膜24a,22aを貫通するコンタクトホール27と、このコンタクトホール27の形成時に、コンタクトホール側壁に付着する有機膜28と、を有する半導体装置を用意する。そして、ポリSi膜22a,24a上に有機膜・レジスト膜26bが被着された状態で、ポリSi膜22a,24a上から、プローブ針31により複数回コンタクトを実施し、有機膜28の抵抗値を測定する。

(もっと読む)

半導体チップ

【課題】 加工処理を行なうための加工位置を精度よく特定することができる半導体チップを提供する。

【解決手段】 複数の半導体回路素子が形成され、それら半導体回路素子上に層間絶縁膜と配線層とが交互に積層されてなる半導体チップ10において、この半導体チップ10を構成する最上層の配線層であるダミーメタル13に、半導体チップ10上のX座標の位置を表わすX座標用コードパターン13_1およびY座標の位置を表わすY座標用コードパターン13_2を付加した。

(もっと読む)

半導体装置

【課題】貫通電流の防止機能を含む半導体装置を半導体基板上に1チップ化する場合に、従来の半導体製造工程を活用することができるようにした半導体装置の提供。

【解決手段】この発明は、ローサイドスイッチを構成するトランジスタQN2のゲート・ソース端子間にダイオード接続されるトランジスタQN5と、ローサイドスイッチを構成するトランジスタQN4のゲート・ソース端子間にダイオード接続されるトランジスタQN6と、を備えている。そして、トランジスタQN5のしきい値電圧がトランジスタQN2のしきい値電圧よりも相対的に低くなっている。また、トランジスタQN6のしきい値電圧がトランジスタQN4のしきい値電圧よりも相対的に低くなっている。

(もっと読む)

1 - 20 / 65

[ Back to top ]