Fターム[5F038EZ08]の内容

Fターム[5F038EZ08]の下位に属するFターム

CAD、DA (704)

シミュレーション評価 (439)

Fターム[5F038EZ08]に分類される特許

21 - 40 / 453

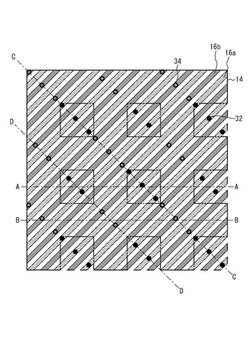

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

スキャンフリップフロップ回路、スキャンテスト回路及びその制御方法

【課題】ホールドフリーの小規模なテスト回路であり、且つ実動作周波数でのテスト可能なスキャンフリップフロップを提供する。

【解決手段】PosタイプF/F100は、クロックの立ち上りエッジ同期し、データ又はスキャンテストデータが選択的に入力されるマスタラッチ(Lowレベルラッチ)110と、マスタラッチ110からのデータが入力されるスレーブラッチ(Hiレベルラッチ)111とを有する。そして、スキャンシフト時には、マスタラッチ110は、スキャンシフトデータ入力SINをスキャンシフトクロックSCLK1のLow期間で取り込むと共にスレーブラッチ111へ出力する。スレーブラッチ111はSCLK1とはエッジ位置が異なるスキャンシフトクロックSCLK2のHi期間でマスターラッチ110の出力を取り込むと共にQに出力する。

(もっと読む)

半導体集積回路のスキャンテスト回路の設計方法、スキャンテスト回路、およびスキャンテスト方法

【課題】半導体集積回路にスキャンパスを組み込んでスキャンテストを行う際に、シングルサイクルパスとマルチサイクルパスが混在している論理回路において、シングルサイクルパスの実動作速度によるテストを可能にすること。

【解決手段】実動作モードでタイミング解析を行い、マルチサイクルパスを抽出する。次に、シングルサイクルパスとマルチサイクルパスの分岐点と、シングルサイクルパスとマルチサイクルパスの合流点を抽出する。そして、上記分岐点から出力側のマルチサイクルパス側の経路上と、上記合流点から入力側のマルチサイクルパス側の経路上に、出力固定回路を挿入する。但し、出力固定回路は、マルチサイクルテスト時には、入力と同じ信号を出力し、シングルサイクルテスト時には、任意の固定値を出力する回路である。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置及びデータ取込方法

【課題】電源ノイズによるデジタル信号の取込エラーを低減すること。

【解決手段】パルス制御信号に応じてスイッチング動作を行なうスイッチング回路120と、デジタル信号を取り込むデジタル信号保持回路111と、を備え、デジタル信号保持回路111は、スイッチング動作による電源ノイズの発生期間におけるデジタル信号の取り込みを回避するためのマスク信号をパルス制御信号から生成するマスク信号生成回路114を含み、電源ノイズの発生期間にはデジタル信号を取り込まず、電源ノイズの非発生期間に前記デジタル信号を取り込む半導体装置。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の品質及び製造歩留まりを向上させる。

【解決手段】半導体装置の製造方法は、SOQウェハ等の貼り合せウェハに複数の半導体チップ部を形成する工程と、絶縁膜を含む下部層(611,621)とメタル配線(メタル層)を含む上部層(612,622)とを有する配線層(61,62)を形成するプロセスを複数回行うことによって、複数の半導体チップ部上に多層配線構造(6)を形成する工程とを有し、ダミーチップ部上に複数重ねられた配線層(61,62)は、製品チップ部上における配線層と同じ形状(パターン)を持つ第1の配線層(61又は62)と、第1の配線層と異なる形状を持つ第2の配線層(62又は61)とを含み、ダミーチップ部上に複数重ねられた配線層のいずれかにおける下部層(611又は621)は、貫通メタル配線を持たない絶縁膜である。

(もっと読む)

半導体回路

【課題】レイアウトの複雑化や面積増大を伴わずにオフリーク電流の抑制と高速化を両立した半導体回路の実現。

【解決手段】通常動作モードと、少なくとも一部の回路に供給する信号を固定して、少なくとも一部の回路の状態を固定する低消費電力モードと、を備え、少なくとも一部の回路20において、低消費電力モード時にオン状態になるトランジスタPT1,PT3,NT2,NT4の閾値電圧が、低消費電力モード時にオフ状態になるトランジスタPT2,PT4,NT1,NT3の閾値電圧より小さい。

(もっと読む)

配線層の形成方法及び半導体装置の製造方法

【課題】配線層の表面の平坦度を高めることができ且つ配線間隔が広い領域において磁界を変動させる構成を無くした配線層の形成方法及び半導体装置の製造方法を提供する。

【解決手段】配線層の形成方法は、下側部材上に配線パターン102を形成する工程と、その上に絶縁材料層103,106を形成する工程と、配線パターンの間に形成された絶縁材料層の一部を、絶縁膜ブロック111として残すと共に、絶縁膜ブロック111の高さを、絶縁膜ブロック以外の絶縁材料層の高さより高くなるように、絶縁材料層をエッチング処理する工程と、絶縁膜ブロックを含む絶縁材料層を研磨して、表面が平坦化された層間膜を形成する工程とを有する。半導体装置の製造方法は、半導体基板と配線層とを有し、上記配線層の形成方法を用いて配線層の少なくとも1つを製造する。

(もっと読む)

集積回路内における、インターフェースデバイスの面積効率の良い配列

【課題】過度にシステムの中にスキューを増加させずに、増加した数の入力/出力デバイスを有するシステムを提供する。

【解決手段】論理回路を備えるコアと、処理コアからおよび処理コアへ信号を伝送するための、複数のインターフェースデバイスであって、2つのタイプのインターフェースデバイスを備える、複数のインターフェースデバイスと、コアに電力を送達するための、電力インターフェースデバイスである、1つのタイプと、コアと集積回路の外部のデバイスとの間で、データ信号を伝送するための信号インターフェースデバイスである、第2のタイプと、を備え、複数のインターフェースデバイスは、コアの外縁に向かう外側列、およびコアの中心により近い外側列の内側にある内側列の、2列に配設され、内側列は、2つのタイプのインターフェースデバイスのうちの一方を備え、外側列は、2つのタイプのインターフェースデバイスのうちの他方を備える、集積回路が開示される。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

配線構造、半導体装置及び不良箇所特定方法

【課題】不良箇所の特定の容易化を実現し得る配線構造、半導体装置及び不良箇所特定方法を提供することにある。

【解決手段】基板10上に形成された第1の配線14と、第1の配線上に形成され、第1の領域において第1の配線と重なり合う第2の配線20とを有し、第1の配線は、第1の領域外に突出する第1のタブ部16を有している。

(もっと読む)

半導体装置、および半導体装置の検査方法

【課題】高抵抗回路の面積の狭小化を図り、集積率の高い半導体装置への高抵抗回路の形成を容易とする。

【解決手段】配線層2に形成された下層配線20および下層配線22と、配線層2上に形成された層間絶縁膜12と、層間絶縁膜12に形成され、下層配線20と接続するビア30と、層間絶縁膜12に形成され、下層配線22と接続するビア32と、層間絶縁膜12上に形成され、ビア30とビア32とを接続する上層配線24と、を備え、ビア30およびビア32の抵抗値は、上層配線24の抵抗値よりも大きい。

(もっと読む)

21 - 40 / 453

[ Back to top ]