Fターム[5F038EZ08]の内容

Fターム[5F038EZ08]の下位に属するFターム

CAD、DA (704)

シミュレーション評価 (439)

Fターム[5F038EZ08]に分類される特許

41 - 60 / 453

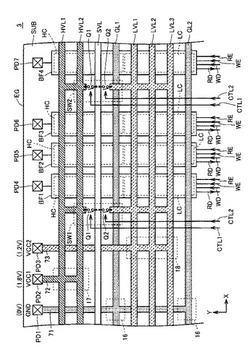

半導体装置

【課題】複数の電圧レベルの電源電圧が供給される入出力バッファ回路に対して、従来よりも少ない電源配線スペースで十分な電源供給を可能にする。

【解決手段】半導体装置3において、入出力バッファ回路BFは電圧レベルの変換を行なう。第1の電源配線HVLは、入出力バッファ回路BFの第1の回路部分HCと接続され、第1の回路部分HCに第1の電源電圧VCC1を供給する。第2の電源配線LVLは、入出力バッファ回路BFの第2の回路部分LCと接続され、第2の回路部分LCに第2の電源電圧VCC2を供給する。複数のスイッチ部SWは、第3の電源配線SVLに沿った複数箇所にそれぞれ設けられる。複数のスイッチ部SWの各々は、内部回路10から出力された制御信号に応じて、第1および第2の電源配線HVL,LVLのうち選択された一方の電源配線と第3の電源配線SVLとを接続する。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

半導体装置

【課題】並列駆動構成のI/Oバッファから出力される信号を安定化し、信頼性を向上する。

【解決手段】I/Oセル2は、1つの出力信号を正転信号と反転信号からなる相補信号として出力する相補型I/Oセルからなり、2つのI/Oセル2が並列接続された構成からなる。2つのI/Oセル2の出力部となるインバータ6の出力部は、配線17によってそれぞれ接続されており、2つのI/Oセル2の出力部となるインバータ7の出力部は、配線18によってそれぞれ接続されている。配線17は、I/Oセル2の下辺側に2つのI/Oセル2を横断するように形成され。配線18は、該配線17の上方に形成されており、2つのI/Oセル2を横断するように形成されている。また、配線17の配線長と配線18の配線長は、略同等となるようにレイアウトされている。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

半導体集積回路

【課題】セル内のメタル配線幅を、設計上許容すべき最大駆動容量Cmax未満の配線幅に設定して、セル内の容量を削減し、セル相互間距離が非常に近い回路などにおいて伝播遅延を所定時間以下に設計することができるようにする。

【解決手段】配線幅以外は全て同一のレイアウトパターンを備えた2種類のスタンダードセル101、151が用意される。一方のスタンダードセル101は、セル内部のメタル配線108、110の配線幅Ws1、Wd1は太く、他方のスタンダードセル151では、セル内部のメタル配線158、160の配線幅Ws2、Wd2は、前記一方のスタンダードセル101の配線幅Ws1、Wd1よりも細く設定される(Ws2<Ws1、Wd2<Wd1)。配線幅の細いセルライブラリ151は、駆動負荷の小さい回路に限定して適用される。

(もっと読む)

半導体装置の配線構造及びそれを備えた半導体装置

【課題】信号配線が電源配線と長距離に亘って並走することを回避して、信号配線の寄生容量を低減してノイズの影響を低減する半導体装置の配線構造及びそれを備えた半導体装置を提供すること。

【解決手段】第1方向X1に延びる複数の第1配線1Vから構成される第1配線層110と、第1配線層110の上に配設され、第1方向X1に交差する第2方向X2に延びる複数の第2配線2Vから構成される第2配線層120とを備え、第1配線層110および第2配線層120は、第1方向X1および第2方向X2により規定される平面内に設定された配線領域R内に配設され、第1配線1Vは、配線領域Rの第1方向X1における一端から他端までの全長よりも短い長さでそれぞれ形成され、第2配線2Vは、配線領域Rの第2方向X2における一端から他端までの全長よりも短い長さでそれぞれ形成されている半導体装置100の配線構造。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

ドライバー集積回路チップの電源連結構造

【課題】本発明は、ドライバー集積回路チップの電源連結構造に関し、より詳細には、ドライバー集積回路チップ内部のルーティングパターンをLOGと並列で配置して、チップの両端に配置された電源を連結することで配線を簡素化してライン抵抗を減少させることができるドライバー集積回路チップの電源連結構造を提供する。

【解決手段】本発明によるドライバー集積回路チップの電源連結構造によると、ドライバー集積回路チップの入出力端子の配線数を減少させて配線を簡素化して、これによりチップサイズを減らして及び製造費用を減少させることができる効果があり、チップ内部のルーティングパターンとLOGを並列で連結することでライン抵抗が減少されて、信号の遅延を減らすことができる長所がある。

(もっと読む)

半導体集積回路およびそのパターンレイアウト方法

【課題】CMP処理においてダミーパターンに機械的ストレスが作用しても、ダミーパターンが折れ曲がったり、ダミーパターンの一部が欠落したりすることを抑制できる半導体集積回路およびそのパターンレイアウト方法を提供する。

【解決手段】半導体集積回路は、所定の機能領域と、空き領域SP1に形成されたダミーパターンDMP1とを備える。空き領域SP1は、所定の機能領域同士の間に位置する。ダミーパターンDMP1は、枠状に形成されるとともに、ダミーパターンDMP1の外縁EDを規定する第1メタル部MT1と、第1メタル部MT1の内周側に位置し、第1メタル部MT1に連続するように形成された第2メタル部MT2と、第1メタル部MT1の内周側において第2メタル部MT2が形成されていない領域に位置する複数の非形成領域NTと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜が剥離しにくい半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法において、複数のデバイス領域がスクライブライン領域によって区画された半導体ウェーハ上に、層間絶縁膜内に配線及びビアが設けられた多層配線膜を形成する工程と、前記スクライブライン領域内に設定されたダイシング領域の一部に配置された前記多層配線膜及び前記半導体ウェーハを除去することにより、前記多層配線膜及び前記半導体ウェーハを前記デバイス領域毎に切り分ける工程と、を設ける。そして、前記多層配線膜を形成する工程において、前記スクライブライン領域における前記ダイシング領域を除く領域には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成し、前記ダイシング領域における前記層間絶縁膜の少なくとも上部には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成しない。

(もっと読む)

半導体装置

【課題】電源電圧の電圧降下を抑制しつつ、信号配線リソースを大きく確保可能な電源配線構造を実現する。

【解決手段】第1配線層に、電源電位配線101a〜101dおよび基板電位配線102a〜102dが形成されており、配線層全体の真ん中より下層側の配線層に、電源ストラップ配線103a,103b,104a,104bが形成されている。上方ビア部114は、下方ビア部112よりも、電源ストラップ配線103a,103b,104a,104bが延びる方向における配置密度が低くなっている。

(もっと読む)

定電圧回路、コンパレータおよびそれらを用いた電圧監視回路

【課題】高いPSRRを有する定電圧回路を提供する。

【解決手段】電流源10は、基準電流Irefを生成する。第1トランジスタM1は、その一端が電流源10と接続され、かつそのゲートソース間が接続されたデプレッション型のMOSFETである。第2トランジスタM2は、その一端が第1トランジスタM1の他端と接続され、その他端が固定電圧端子と接続され、かつそのゲートドレイン間が接続されたエンハンスメント型のMOSFETである。第3MOSFETは、その一端が電流源10と接続され、その他端が固定電圧端子と接続され、かつそのゲートが第1トランジスタM1と第2トランジスタM2の接続点N1と接続されたエンハンスメント型のPチャンネルMOSFETである。定電圧回路100は、第3トランジスタM3のゲート電圧およびそのソース電圧の少なくとも一方に応じた電圧を出力する。

(もっと読む)

昇圧回路及び昇圧回路を用いたRFIDタグ

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

半導体集積回路の診断テストパターン数最適化プログラム

【課題】

組込み自己試験法によるテスト機構を備えた半導体集積回路において、診断テストパターン数を増加させずに故障検出率を向上させることができるプログラムを提供する。

【解決手段】

診断テストパターンとして発生した擬似乱数の各々で新たに検出される故障数が0又は、所定の基準値以下であるかを判定するステップと、テストグループに割り当てられた診断テストパターン発生回数の最後で発生した擬似乱数で新たに検出される故障数が任意の基準値以上であるかを判定するステップとから、パス数比でテストグループに割り当てられた診断テストパターン数を、故障の検出のし易さ(難易度)に応じて再配分することで診断テストパターン数を最適化し、故障検出率を向上させる。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

電子回路

【課題】電源の立ち上がりを検出するための電源検出器の数を大幅に増加させることなく、電子回路の電源シーケンスフリー化を実現する。

【解決手段】3種類以上の電源電圧が供給されて動作される電子回路(1、1A、1B)は、所定の電源電圧を動作電源として動作する第1の検出回路(101)により、他の電源電圧が一つでも立ち上がっていない状態であるか否かを示す第1の検出信号(104_1)を生成する。また、前記電子回路は、前記他の電源電圧の一つの電源電圧を動作電源として動作し、前記他の電源電圧毎に設けられた第2の検出回路(102)により、前記所定の電源電圧が立ち上がったか否かを示す第2の検出信号(106_A〜106_F)を生成する。そして、前記電子回路は、前記第1の検出信号及び第2の検出信号に基づいて、前記他の電源電圧毎にその他の電源電圧の立ち上がりを保証するための制御信号(104_2〜104_7)を生成する。

(もっと読む)

半導体装置

【課題】 セルサイズが小さく、かつ配線接続の自由度が向上できるスタンダードセルを用いた半導体装置を提供する。

【解決手段】 半導体装置はメモリ回路と周辺回路を備え、周辺回路を分割した回路ブロックのそれぞれを、同じ高さを有した矩形で、それぞれが基本論理回路として機能するように構成された複数のスタンダードセルを、同じ高さになるように配置したセルブロックとして構成し、スタンダードセルへの入力信号配線が、メモリセルトランジスタと容量下部電極を接続する容量コンタクトパッド配線を用いて配線される。

(もっと読む)

半導体集積回路装置

【課題】ダミービアが配置された半導体集積回路装置において、ダミービアに接続されたダミー配線の存在に起因する、設計容易性の低下や製造コストの増大といった問題を抑える。

【解決手段】半導体集積回路装置は、基板1と、基板1上に形成された3層以上の配線層2a〜2cとを有する。配線層2a,2bの間にダミービア11が形成されており、配線層2bにダミービア11と接続されたダミー配線12が形成されている。ダミー配線12は、スタックビア構造20の配線層2bに形成された中間配線24よりも、面積が小さい。

(もっと読む)

モジュール設計方法及び装置

【課題】チップ設計におけるチップの再設計時間を最小に抑える。

【解決手段】カスタム設計チップを、可変でスケーラブルなモジュールマルチプロセッサ設計で、設計を含むモジュールの再設計を行わずに提供する方法である。この設計では、PUモジュール、第1の複数のアシストプロセッシングモジュール、及び、各々が複数のアシストプロセッシングモジュールのうち異なる1つに関連付けられている第1の複数のDMAコントロールモジュールが含まれる。複数のモジュールのうち1つ以上のモジュールを含む、第1のマルチプロセッサ設計を生成し、この第1の設計から、削減する、及び/又は、追加するモジュールの数を予め選択する。更に、予め選択されたモジュールが選択された数削減及び/又は追加された、第2のマルチプロセッサ設計を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが簡便な多層配線構造を有する半導体装置を提供する。

【解決手段】第1配線層と、第1配線層上の第1層間絶縁膜と、第1配線層と交差し、第1層間絶縁膜上に設けられた第2配線層と、第2配線層上の第2層間絶縁膜と、第1配線層と第2配線層とを電気的に接続するビア導体とを有し、第2配線層は、第1配線層との交差位置に当該第2配線層を分離するスペースを有し、前記ビア導体は、分離された第2配線層間を電気的に接続するように前記分離スペースを経由し、第2層間絶縁膜および第1層間絶縁膜を貫通して第1配線層に達する、半導体装置。

(もっと読む)

41 - 60 / 453

[ Back to top ]