Fターム[5F045AB18]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 3−5族 (4,971) | 4元混晶 (505)

Fターム[5F045AB18]に分類される特許

21 - 40 / 505

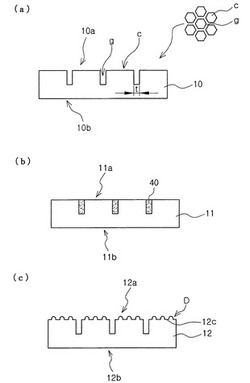

半導体発光素子の製造方法

【課題】簡単な工程で光抽出効率を向上させた半導体発光素子の製造方法を提供する。

【解決手段】本発明の半導体発光素子の製造方法は、互いに対向する第1及び第2の主面を有する基板を設ける段階と、基板の第1の主面に柱状を有する複数の凸部を形成する段階と、凸部が形成された第1の主面上に第1の導電型半導体層、活性層、及び第2の導電型半導体層を含む発光積層体を形成する段階と、発光積層体のうちの凸部の周囲の溝部に対応する領域に形成された部分を除去して複数の発光構造物を形成する段階と、基板上に形成された複数の発光構造物から個別素子が得られるように溝部に沿って基板を分離する段階と、を有する。

(もっと読む)

半導体エピ薄膜の成長方法及びこれを用いた半導体発光素子の製造方法

【課題】反応ガスを供給するノズルが詰まる現象を緩和して工程効率及び生産性を向上させた半導体エピ薄膜の成長方法及びこれを用いた半導体発光素子の製造方法を提供する。

【解決手段】本発明の半導体エピ薄膜の成長方法は、ウェハーホルダーに積載された複数のウェハーを反応チャンバの内部に配置する段階と、ウェハーの積載方向に沿って延長されて備えられたガス供給部を通じて塩素系有機金属化合物を含む反応ガスをウェハーに噴射し、各ウェハーの表面に半導体エピ薄膜を成長させる段階と、を有する。

(もっと読む)

光集積素子の製造方法

【課題】バットジョイント構造を構成する第1及び第2の半導体積層部上に成長する半導体層に生じる結晶欠陥を低減する。

【解決手段】エッチングマスク30を用いて第1の半導体積層部20にエッチングを施す工程と、Alを含む光吸収層42、及び光吸収層42上に設けられるInPクラッド層44を有する第2の半導体積層部40を、エッチングマスク30を用いて選択的に成長させる第1の再成長工程と、エッチングマスク30を除去するマスク除去工程と、第1及び第2の半導体積層部20,40上に第3の半導体積層部を成長させる第2の再成長工程とを行う。第1の再成長工程において、InPに対してエッチング選択性を有するInP系化合物半導体を含むキャップ層46を第2の半導体積層部40上に更に成長させる。マスク除去工程の前に、エッチングマスク30上に生じたInP系堆積物Deを除去する。

(もっと読む)

半導体光素子の製造方法

【課題】過剰なエッチングを抑制するとともに半導体表面の突起物を除去する半導体光素子の製造方法を提供する。

【解決手段】半導体光素子の製造方法は、エッチストップ層13及び複数の半導体層を含み、半導体光素子のための半導体積層10を半導体基板11の主面11aにエピタキシャル成長させる半導体積層成長工程と、半導体積層10の最表面から突出する突起物の先端部が露出するように、最表面にマスク層を形成するマスク層形成工程と、マスク層を用いて、ウェットエッチングにより突起物をエッチングするウェットエッチング工程と、ウェットエッチングの後に、ドライエッチングにより突起物を除去するドライエッチング工程と、突起物を除去した後に、最表面からマスク層を除去するマスク層除去工程と、マスク層を除去した後に、半導体積層10に半導体光素子のための加工を行う加工工程と、を備えている。

(もっと読む)

窒化物半導体装置

【課題】リーク電流を低減でき、かつ、良好な電流コラプス特性が得られる窒化物半導体装置を提供する。

【解決手段】Si基板1上に順に積層されたチャネルGaN層5およびそのチャネルGaN層5とヘテロ界面を形成するバリアAlGaN層6を含む窒化物半導体層を備える。上記バリアAlGaN層6は、炭素濃度を5×1017/cm3以上とする。また、チャネルGaN層5は、炭素濃度を6×1016/cm3未満とし、かつ、膜厚を500nm以上とする。

(もっと読む)

半導体発光素子の製造方法

【課題】本発明は、半導体発光素子の製造方法に関する。

【解決手段】本発明の実施例による半導体発光素子の製造方法は、半導体成長用基板上に第1導電性半導体層、活性層及び第2導電性半導体層を順に成長させて発光部を形成する段階と、上記第2導電性半導体層上に上記発光部と結合されるように支持部を形成する段階と、上記発光部から上記半導体成長用基板を分離する段階と、上記分離された半導体成長用基板の表面に残存する半導体層が除去されるように上記半導体成長用基板にエッチングガスを適用する段階とを含む。

(もっと読む)

化合物半導体結晶の製造方法

【課題】複雑な作製工程を必要とせずに、均一に高品質な結晶が形成できるようにする。

【解決手段】まず、III−V族化合物半導体の単結晶からなる基板101の主表面におけるテラスの幅を、主表面の(100)面からの傾斜角度により制御する。この制御では、後述する第3工程で形成する第2半導体層103の第2原子間隔と、基板101の主表面における第1原子間隔と、自然数Nとを用いて表されるN×第1原子間隔≒(N−1)×第2原子間隔の関係が成立する条件で、テラスの幅がN×第1原子間隔となる状態に基板101の主表面を傾斜させる。なお、第2原子間隔は、第1原子間隔と同じ方向の、第2半導体層103を構成する原子の間隔である。

(もっと読む)

気相成長方法及び発光素子用基板の製造方法

【課題】 HVPE成長装置内の基板以外の部材への原料ガスによるGaPの析出数を制御することができるハイドライド気相成長方法を提供することを目的とする。

【解決手段】 気相成長装置内で基板上に、III−V族化合物半導体層をハイドライド気相成長法によってエピタキシャル成長させる気相成長方法であって、前記III−V族化合物半導体層のエピタキシャル成長途中に、少なくとも1回該エピタキシャル成長を中断して前記気相成長装置内のガスエッチングを行うことを特徴とする気相成長方法。

(もっと読む)

III族窒化物積層体の製造方法

【課題】Al含有率が高いIII族窒化物半導体上にP型GaN層が形成された積層体において、その表面が極めて平滑であり、電極特性が良好な積層体の製造方法を提供する。

【解決手段】AlXGaYInZN(X、YおよびZが、X+Y+Z=1.0,Y≧0,Z≧0,0.5≦X≦1.0である)層と、不純物原子がドープされたGaN層と有するIII族窒化物積層体を製造する方法であって、P型GaN層16が、層厚みをT[nm]とし、P型GaN層の層厚み方向における成長速度をGR[nm/分]とし、P型GaN層を形成するために用いられるGa原料の流量をFGa[μmol/分]とし、不純物原子原料の流量をFi[μmol/分]としたときに、GRが0.15以上2.0以下、(Fi/FGa)×ln(T)が0.1を超え0.4以下となるように成長させる。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、結晶基板の表面層の均一歪みが1.9×10-3以下であり、結晶基板の表面層の不均一歪みが130arcsec以下であり、均一歪みと不均一歪みとは、それらの一方が小さくなるほど他方が小さくなる関係を有し、結晶基板の主表面1sの面方位が、結晶基板の(0001)面または(000−1)面1cから<10−10>方向に10°以上80°以下で傾斜している。

(もっと読む)

有機金属気相成長装置および成長方法、半導体装置およびその製造方法

【課題】P型、N型(I型)結晶を別々に形成する2チャンバ方式により、Mgのドーピングに伴う遅延効果およびメモリ効果を抑制し、エピタキシャル成長時間を短縮したMOCVD装置およびその成長方法、上記のMOCVD装置を適用して形成した半導体装置およびその製造方法を提供する。

【解決手段】水冷機構を備えるコールドウォール構造を備え、ガスの流れはウェハ8の表面に対して水平方向であり、P型層成長とN型(I型)層成長ではそれぞれ別のN型(I型)層成長用チャンバ14・P型層成長用チャンバ16で成長するように構成され、ウェハ8を保持するサセプタも別々のN型層成長用サセプタ3・P型層成長用サセプタ5を使用するMOCVD装置およびその成長方法、上記のMOCVD装置を適用して形成した半導体装置およびその製造方法。

(もっと読む)

窒化物半導体レーザ素子、エピタキシャル基板、及び窒化物半導体レーザ素子を作製する方法

【課題】長波長のレーザ発振においてしきい値電流を低減できるクラッド構造を有する窒化物半導体レーザ素子を提供する。

【解決手段】n型クラッド層21、活性層25及びp型クラッド層23は主面17aの法線軸NXの方向に配置される。この主面17aは、六方晶系窒化物半導体のc軸の方向に延在する基準軸Cxに直交する面を基準に63度以上80度未満の範囲の角度ALPHAで六方晶系窒化物半導体のm軸の方向に傾斜している。活性層25はn型クラッド層21とp型クラッド層23との間に設けられる。

活性層25は波長480nm以上600nm以下の範囲にピーク波長を有する光を発生するように設けられる。n型クラッド層21及びp型クラッド層23の屈折率はGaNの屈折率よりも小さい。n型クラッド層21の厚さDnは2μm以上であり、p型クラッド層23の厚さDpは500nm以上である。

(もっと読む)

半導体素子及びその製造方法

【課題】転位密度を低減させるバッファ層を有する半導体素子を提供する。

【解決手段】基板と、基板の上方に形成されたバッファ領域と、バッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、バッファ領域は、第1の格子定数を有する第1半導体層と、第1の格子定数と異なる第2の格子定数を有する第2半導体層と、第1の格子定数と第2の格子定数との間の第3の格子定数を有する第3半導体層とが順に積層した複合層を少なくとも一層有する半導体素子。

(もっと読む)

膜成長装置および発光ダイオード

【課題】

結晶膜のCVD装置において、成長させる基板数を多くしたい。特に有機金属原料から成長させるGaNなどのバンドギャップの大きい化合物半導体の結晶成長CVD装置において、その要求が強い。

【解決手段】

中心に排気シリンダーを備えたサセプタを積層させ、当該サセプタに基板を載せて、加熱したサセプタの間にCVDの原料ガスを通す。ガスの消費効率を向上させるとともに積層させたサセプタに枚数に比例して一度に成長させる基板の枚数が増える。

(もっと読む)

成長基板及び発光素子

【課題】歪みを減少し、品質を向上させることができる成長基板及び発光素子を提供すること。

【解決手段】本発明の一実施例による発光素子は、シリコン基板と、前記シリコン基板上に形成され、前記シリコン基板の一部を露出する第1バッファ層と、前記第1バッファ層及び前記露出されたシリコン基板を覆い、前記シリコン基板と共晶反応する物質からなる第2バッファ層と、前記第2バッファ層上に形成される第3バッファ層と、前記第3バッファ層上に形成される発光構造物とを備え、前記第2バッファ層はボイドを含む。

(もっと読む)

III族窒化物半導体発光素子及びその製造方法

【課題】窒化ガリウム等からなるクラッド層等の下地層上に、窒化ガリウムより格子定数が大きい窒化ガリウム・インジウムからなる発光層を設けるのに際し、発光層中へのインジウムの取り込みを促進させた窒化物半導体発光素子を提供する。

【解決手段】n形窒化アルミニウム・ガリウム・インジウム層と、接して配置され且つn形窒化アルミニウム・ガリウム・インジウム層よりも大きな格子定数の結晶を含む窒化ガリウム・インジウム層からなる発光層と、発光層上に設けられたp形窒化アルミニウム・ガリウム・インジウム層とを備え、インジウムより原子半径が小さい元素からなるドナー不純物の原子濃度を、n形窒化アルミニウム・ガリウム・インジウム層の内部よりもn形窒化アルミニウム・ガリウム・インジウム層と発光層との界面において低く、且つ、上記界面よりも発光層とp形窒化アルミニウム・ガリウム・インジウム層との界面において高くする。

(もっと読む)

半導体素子及びその製造方法

【課題】厚膜化が可能で、反りが小さく、かつリーク電流が小さい半導体素子を提供する。

【解決手段】基板と、基板の上方に形成された第1のバッファ領域と、第1のバッファ領域上に形成された第2のバッファ領域と、第2のバッファ領域上に形成された活性層と、活性層上に形成された少なくとも2つの電極とを備え、第1のバッファ領域は、第1半導体層と、第2半導体層とが順に積層した複合層を少なくとも一層有し、第2のバッファ領域は、第3半導体層と、第4半導体層と、第5半導体層とが順に積層した複合層を少なくとも一層有し、第4半導体層の格子定数は、第3半導体層と第5半導体層の間の格子定数を有する半導体素子。

(もっと読む)

材料ガス供給ノズル、気相成長装置および半導体膜の製造方法

【課題】温度むらを生じることなく材料ガスの冷却を行うことができる冷却機構を備えた材料ガス供給用ノズル、該ノズルを備えた気相成長装置および該気相成長装置を用いた半導体膜の製造方法を提供する。

【解決手段】

材料ガス流通層は、材料ガスの吹き出し口と、吹き出し口に連通するガス流通通路とを有する。冷却媒体循環層は、ガス流通通路を覆う冷却媒体の循環通路を有する。材料ガス流通層は、吹き出し口側の端部において材料ガス流の上流側に凹んだ第1の凹部を有し、吹き出し口は、第1の凹部の端面に沿って設けられている。冷却媒体循環層は、第1の凹部と外縁が重なる第2の凹部と、第2の凹部を挟む両側の第2の凹部の周辺部にガス流通通路よりも外側に張り出した拡張部と、を有する。冷却媒体の循環通路は、第2の凹部の材料ガス流の上流側端部よりも下流側であって拡張部内に冷却媒体の循環の折り返し点を有する。

(もっと読む)

発光ダイオード

【課題】格子欠陥が発生することを防止した発光ダイオードを提供する。

【解決手段】発光ダイオード10は、基板100と、第一半導体層120と、第二半導体層140と、活性層130と、第一電極150と、第二電極160と、を含む。第一半導体層、活性層、及び第二半導体層は、基板から離れる方向に沿って、基板に順次的に積層され、第一電極は、第一半導体層に電気的に接続され、第二電極は、第二半導体層に電気的に接続され、第一半導体層の基板と隣接する表面は、複数の空隙を含むパターン化されたカーボンナノチューブ層102である。第一半導体層のパターン化された表面が基板に接続することによって複数のキャビティが形成される。

(もっと読む)

発光ダイオード

【課題】格子欠陥が発生することを防止した光取り出し効率の高い発光ダイオードを提供する。

【解決手段】発光ダイオードは、第一半導体層120と、第二半導体層140と、活性層130と、第一電極150及び第二電極160と、を含む。第一半導体層、活性層及び第二半導体層が、第一電極から離れる方向に沿って、基板に順に積層して設置され、第一半導体層が、第一電極に接続され、第二電極が、第二半導体層に電気的に接続され、第一半導体層の第一電極と隣接する表面が、複数の溝を含むパターン化表面122であり、第一半導体層のパターン化表面が、第一電極に接続される。

(もっと読む)

21 - 40 / 505

[ Back to top ]