Fターム[5F045AE23]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜時の圧力 (3,707) | 減圧(圧力が明示されていない) (3,333) | 7.6≦P<76Torr(0.01≦P<0.1気圧 10.13≦P<101.3hPa) (552)

Fターム[5F045AE23]に分類される特許

21 - 40 / 552

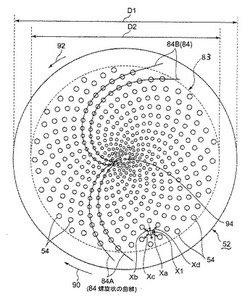

シャワーヘッド装置及び成膜装置

【課題】膜厚の面内均一性を高くすることが可能なシャワーヘッド装置を提供する。

【解決手段】薄膜が形成される被処理体Wを収容する処理容器4内へガスを導入するシャワーヘッド装置46において、内部にガスを拡散させるガス拡散室48が形成されたシャワーヘッド本体50と、シャワーヘッド本体のガス噴射板52に設けられた複数のガス噴射孔54とを有し、複数のガス噴射孔は、ガス噴射板の中心部を中心として仮想的に形成される複数の螺旋状の曲線84に沿うように配置されている。これにより、ガスを平面方向へ均一に分散させて、膜厚の面内均一性を高くする。

(もっと読む)

サセプタ、半導体製造装置及び半導体製造方法

【課題】成膜時の温度制御が可能となり、ウェーハ上に成膜された膜厚のバラツキを極めて少なくし、生産性を高めた半導体製造装置および半導体製造方法を提供する。

【解決手段】サセプタ11は、ウェーハwの径より小さく、表面に凸部12b(温度制御板となる)を有するインナーサセプタ12と、中心部に開口部を有し、インナーサセプタを開口部が遮蔽されるように載置するための第1の段部と、この第1の段部の上段に設けられ、ウェーハを載置するための第2の段部を有するアウターサセプタ13を備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

III族窒化物半導体単結晶の製造方法

【課題】非極性面及び半極性面を主面とした結晶成長において、多結晶が発生することにより生じる、結晶の厚膜成長阻害を防ぐことを課題とする。

【解決手段】III族窒化物結晶からなり非極性面又は半極性面を主面とする下地基板上に、III族窒化物半導体結晶を成長させるIII族窒化物半導体結晶の製造方法において、前記主面からc軸方向に±90°傾斜した面をK面と定義したとき、該K面に対して特定の角度の面を有する側面を持った下地基板を用いることで多結晶発生の問題を解決する。

(もっと読む)

半導体素子、HEMT素子、および半導体素子の製造方法

【課題】逆方向漏れ電流が抑制されてなるとともに二次元電子ガスの移動度が高い半導体素子を提供する。

【解決手段】下地基板1の上にIII族窒化物層群を(0001)結晶面が基板面に対し略平行となるよう積層形成したエピタキシャル基板10と、ショットキー性電極9と、を備える半導体素子20において、エピタキシャル基板10が、Inx1Aly1Gaz1N(x1+y1+z1=1、z1>0)なる組成の第1のIII族窒化物からなるチャネル層3と、Inx2Aly2N(x2+y2=1、x2>0、y2>0)なる組成の第2のIII族窒化物からなる障壁層5と、GaNからなり障壁層5に隣接する中間層6aと、AlNからなり中間層に隣接するキャップ6b層と、を備え、ショットキー性電極9がキャップ層6bに接合されてなるようにする。

(もっと読む)

半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム

【課題】シリコン系ガスとアミン系ガスとを使用してSiC等のSiC系の膜を低温で成膜できる半導体装置の製造方法、基板処理方法、基板処理装置およびプログラムを提供する。

【解決手段】基板200を処理室201内に収容する工程と、加熱された処理室201内へシリコン系ガスとアミン系ガスとを供給して基板200上にシリコンおよび炭素を含む膜を形成する工程と、を有し、シリコンおよび炭素を含む膜を形成する工程は、処理室201内へシリコン系ガスとアミン系ガスとを供給して、シリコン系ガスとアミン系ガスとを処理室201内に封じ込める工程と、シリコン系ガスとアミン系ガスとを処理室201内に封じ込めた状態を維持する工程と、処理室201内を排気する工程と、を有する。

(もっと読む)

プラズマCVD装置を用いた半導体装置の製造方法

【課題】プラズマCVD装置を用いた半導体装置の製造方法に関し、製膜室のクリーニング後に、仮製膜を行った際に堆積する膜の剥離を防ぎ、半導体薄膜中に堆積膜が混入することを防ぐ方法を提供する。

【解決手段】プラズマCVD装置を用いた半導体装置の製造方法においては、仮製膜の際に結晶質シリコン薄膜を用いている。仮製膜の際に、結晶質シリコン薄膜を用いることで、堆積膜が半導体薄膜の膜中に取り込まれることを防ぐことが可能となった。

(もっと読む)

熱処理装置

【課題】被処理体が大型化した場合であっても、蓋体の肉厚を過度に大きくすることなく、蓋体の重量増加を抑える。

【解決手段】熱処理装置1は被処理体Wを収容して熱処理するための処理容器3と、処理容器3の周囲を覆う断熱材16と、断熱材16内周面に設けられたヒータ5とを有する熱処理炉2と、処理容器3の炉口3aを閉塞する蓋体10と、蓋体10上に保温筒11を介して支持され被処理体Wを多段に保持する保持具12とを備えている。蓋体10はステンレス等の耐食性金属製となっており、下方へ向って突出する湾曲板からなる。

(もっと読む)

半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

(もっと読む)

エピタキシャルウエハ及び半導体素子

【課題】エピタキシャル成長層の結晶品質を向上させることができ、厚膜のエピタキシャル成長層を形成する場合においてもキャリア移動度の低下が生じず、素子抵抗の低い炭化珪素エピタキシャルウエハおよび炭化珪素半導体素子を提供する。

【解決手段】炭化珪素半導体素子は、ドーピングにより格子定数が減少するドーパントを濃度Aでドーピングした基板と、ドーパントを基板よりも小さい濃度Bでドーピングしたエピタキシャル成長層と、基板とエピタキシャル層との間に、ドーパントをドーピングした2層以上積層した多層構造で形成されたバッファ層とを有し、多層構造の各層のドーパントのドーピング濃度Cが、バッファ層の厚さをd、エピタキシャル成長層からの各層までの平均距離をx、所定の割合をPとして、[B+(A−B)×x/d]×(1−P)≦C≦[B+(A−B)×x/d]×(1+P)とした。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】高温処理においても、サセプタ変形を抑制することができる基板処理技術を提供する。

【解決手段】基板が載置された載置体と、前記載置体が複数支持された載置体支持具と、前記載置体支持具が収容される反応管と、前記反応管の外側に設けられ、前記反応管内に収容された基板を加熱する加熱部とを備え、前記載置体の、前記基板と接触する面と前記載置体支持具と接触する面が、同じ粗さに表面加工されるように基板処理装置を構成する。

(もっと読む)

基板処理装置および基板処理方法

【課題】一度に処理する基板の枚数を増大させ、GaNのエピタキシャル膜の生産性を向上させることができる膜の形成方法及び基板処理装置を提供する。

【解決手段】エピタキシャル膜を有する基板を処理する基板処理装置において、前記基板処理装置は、前記基板を処理する処理室201と、前記処理室内に少なくとも前記エピタキシャル膜を形成する原料ガスとクリーニングガスを供給するガス供給源240と、前記処理室内の少なくとも温度と圧力を制御する制御部280と、前記制御部は、前記処理室内が予め定められた温度および圧力になると前記処理室内をクリーニングガスを供給するように前記ガス供給源を制御する、ことを特徴とした基板処理装置。

(もっと読む)

半導体発光装置に成長させたフォトニック結晶

【課題】フォトニック結晶構造を含む半導体発光装置を提供する。

【解決手段】n型領域とp型領域の間に配置された発光領域を含むIII族窒化物構造のような半導体構造内にフォトニック結晶を成長させる。フォトニック結晶は、半導体材料の複数の領域とすることができ、これらの領域は、この半導体材料とは屈折率が異なる材料によって分離されている。例えば、フォトニック結晶は、構造内に成長して空隙又はマスク材料の領域によって分離された半導体材料のポストとすることができる。フォトニック結晶を既に成長した半導体層内にエッチングするのではなくフォトニック結晶を成長させることは、効率を低下させることがあるエッチングが原因の損傷を回避し、電気接点がその上に形成される、割り込まれていない平坦な表面を提供する。

(もっと読む)

熱処理炉及び熱処理装置

【課題】断熱材の断熱性能を向上させるとともに断熱材の厚みの増加を抑える。

【解決手段】熱処理炉2は被処理体Wを収容して熱処理するための処理容器3と、該処理容器3の周囲を覆う断熱材16と、断熱材16の内周面に設けられ被処理体Wを加熱するヒータ5とを備えている。断熱材16は通常の断熱材料からなる内側断熱材16aと、圧縮された微粉シリカ材からなる外側断熱材16bとを有し、外側断熱材16bの外面は飛散防止材16cにより覆われている。

(もっと読む)

シリコン絶縁膜の形成方法

【課題】熱CVD法やALD法等によってシリコン絶縁膜を形成する際に、成膜温度を増加させることなく薄膜成長速度を増加させて生産性の向上が可能なシリコン絶縁膜の形成方法を提供する。

【解決手段】シリコン源としてアミノシラン化合物を用いるシリコン絶縁膜の形成方法であって、前記アミノシラン化合物は、分子内の全てのSi−NR1R2(R1及びR2は、水素(H)又は炭素数1〜4の直鎖状又は分岐状アルキル基)結合が、H3Si−NR1R2構造としたときの正規化双極子モーメントが1.37以上を有するとともに、分子内にアミノ基を3個有するトリスアミノ構造又は分子内にアミノ基を4個有するテトラキスアミノ構造を有することを特徴とするシリコン絶縁膜の形成方法を提供する。

(もっと読む)

半導体装置の製造方法および成膜装置

【課題】半導体装置の特性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】HDP−CVD装置(1)の処理室内に半導体基板(100)を搬入し、半導体基板上に化学気相成長法により第1膜(例えば、酸化シリコン膜)を形成する。その後、リモートプラズマ装置(20)内から、Alを含有する材料よりなる配管であって、その内壁にコーティング材料層を有する配管(10)を通して、処理室内にラジカル化されたガス(例えば、フッ素ラジカル)を導入することにより処理室の内壁に付着した第1膜(例えば、酸化シリコン膜)を除去(クリーニング)する。かかる方法によれば、コーティング材料層により、発塵を低減し、クリーニング効率を向上することができる。

(もっと読む)

熱処理炉及び熱処理装置

【課題】ウエハを均一に加熱することができ、かつヒータエレメントの寿命を伸ばすこと。

【解決手段】熱処理炉2は被処理体Wを収容して熱処理するための処理容器3と、該処理容器3の周囲を覆う断熱材16と、断熱材16内周面16aに設けられ被処理体Wを加熱するヒータ5とを備えている。上記ヒータ5は、円筒状の断熱材16の内周面16aに沿ってスパイラル状に配置されたヒータエレメント18を有している。ヒータエレメント18は帯状のものを波形に曲げ加工してなり、外側に突出する谷部18aと内側へ突出する山部18bとを有するコルゲート型のヒータエレメントからなる。谷部18aは谷部支持ピン部材20aにより支持され、山部18bは山部支持ピン部材20bにより支持されている。

(もっと読む)

化合物半導体結晶の製造方法

【課題】複雑な作製工程を必要とせずに、均一に高品質な結晶が形成できるようにする。

【解決手段】まず、III−V族化合物半導体の単結晶からなる基板101の主表面におけるテラスの幅を、主表面の(100)面からの傾斜角度により制御する。この制御では、後述する第3工程で形成する第2半導体層103の第2原子間隔と、基板101の主表面における第1原子間隔と、自然数Nとを用いて表されるN×第1原子間隔≒(N−1)×第2原子間隔の関係が成立する条件で、テラスの幅がN×第1原子間隔となる状態に基板101の主表面を傾斜させる。なお、第2原子間隔は、第1原子間隔と同じ方向の、第2半導体層103を構成する原子の間隔である。

(もっと読む)

アモルファスカーボン膜の形成方法および形成装置

【課題】カバレッジ性能、及び、表面ラフネスの良好なアモルファスカーボン膜の形成方法および形成装置を提供する。

【解決手段】制御部100は、昇温用ヒータ16を制御して、複数枚の半導体ウエハWが収容された反応管2内を800℃〜950℃に加熱する。次に、制御部100は、MFC制御部を制御して、加熱された反応管2内にアンモニアガスを供給する。続いて、制御部100は、昇温用ヒータ16を制御して、反応管2内を所定の温度に加熱し、MFC制御部を制御して、加熱された反応管2内に処理ガス導入管17からエチレンを供給する。これにより、半導体ウエハWにアモルファスカーボン膜が形成される。

(もっと読む)

半導体エピタキシャル基板、およびその製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

21 - 40 / 552

[ Back to top ]