Fターム[5F045CA05]の内容

気相成長(金属層を除く) (114,827) | 半導体素子等への用途 (4,120) | MISトランジスタ(TFTを除く) (459)

Fターム[5F045CA05]に分類される特許

1 - 20 / 459

半導体装置およびその製造方法

シリコン膜の形成方法及び半導体装置の製造方法

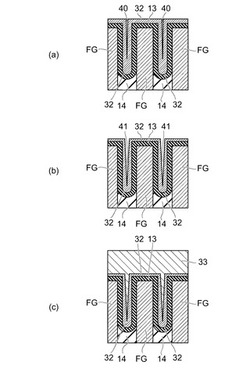

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置、半導体装置の製造方法および薄膜

【課題】導電性または半導体性を示す、新規な環状シロキサン重合体を含む半導体装置を提供する。

【解決手段】この半導体装置は、中心金属に遷移金属を有する構造単位(A)と、隣り合う構造単位(A)の間に位置し、環状シロキサン骨格を含む構造単位(B)と、を含むプラズマ重合体からなる電荷輸送層を備えている。なお、中心金属に遷移金属を有する有機金属化合物と、環状シロキサン化合物と、を反応炉でプラズマ重合させることにより、当該電荷輸送層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】堆積速度が速く、好ましくは約700℃以下のような低いプロセス温度を維持し、置換型炭素濃度が高い、SiとCを含有する選択エピタキシャル層を得る方法を提供する。

【解決手段】基板上にSiとCを含有するエピタキシャル層を形成する方法であって、単結晶表面と、アモルファス表面、多結晶表面及びこれらの組み合わせより選ばれる少なくとも一つの第二表面とを含む基板をプロセスチャンバ内に配置するステップと、プロセスチャンバ内の圧力を少なくとも300トールに維持しつつ、該基板をシリコン源と、炭素源と、リン源にさらして、該基板の少なくとも一部にリンがドープされたSi:Cエピタキシャル膜を形成するステップと、700℃以下のプロセスチャンバ内の温度の下で、HClを含むエッチングガスに該基板をさらすことにより該基板を更に処理するステップと、を含む。

(もっと読む)

窒化物半導体素子及び製造方法

【課題】耐圧が高く、かつ、リーク電流が効果的に低減された窒化物半導体素子及びその製造方法を提供する。

【解決手段】ベース基板210と、ベース基板の上方に形成されたバッファ層280と、バッファ層280上に形成された活性層290と、活性層の上方に形成された少なくとも2つの電極292および294とを備え、バッファ層280は格子定数の異なる複数の窒化物半導体層を含む複合層を1層以上有し、複合層の少なくとも1層は、複数の窒化物半導体層のうち格子定数が最も大きい窒化物半導体層のキャリア領域に予め定められた濃度の炭素原子及び予め定められた濃度の酸素原子が意図的にドープされている窒化物半導体素子。

(もっと読む)

不純物濃度を選択的に減少させたIII−V族デバイス構造

【課題】HEMT及びその他の高速スイッチングデバイスにおいて、意図しない不純物のドープはを防ぎ高性能なデバイスを提供する。

【解決手段】半導体構造は、基板、基板上方の遷移体、及び遷移体上方に底面を有するIII−V族中間体を備える。半導体構造はさらに、III−V族中間体の頂面上方にIII−V族デバイス層を備える。III−V族中間体213は、前記底面211において高く、前記頂面213において低くなる形で連続的に減少された不純物濃度を有する。

(もっと読む)

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

エピタキシャル成長装置

【課題】リフレクタからの熱線を調節してシリコン単結晶基板を面内均一に加熱し、膜厚が均一なエピタキシャル層を成長させることができる装置を提供することを目的とする。

【解決手段】サセプタの上下に各々配置され、放射状に円形に並べられた複数の棒状の単体ヒータを有するヒータと、上のヒータの上側及び前記下のヒータの下側に各々配置された上下のドーナツ状リフレクタとを備え、上下のドーナツ状リフレクタの少なくとも一つは、ヒータの熱放射を収束させる収束反射板部と熱放射を分散させる分散反射板部とを有し、収束反射板部は棒状の単体ヒータに沿って形成された円筒凹面を有し、かつ該円筒凹面はドーナツ状リフレクタの径方向で異なった曲率半径の断面の部分を有するものであるエピタキシャル成長装置。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】(0001)面に対して4°以下のオフ角θ1で傾斜したSi面が主面4とされたSiC基板2と、SiC基板2の主面4に形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、SiC基板2の主面4のオフ方向Dを、[11−20]軸方向および[01−10]軸方向に対して15°+/−10°の角度θ2で傾斜した方向にする。

(もっと読む)

基板処理方法および基板処理装置

【課題】シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くする。

【解決手段】基板処理装置1では、酸化膜除去部4にて基板9の一の主面上のシリコン酸化膜が除去された後、シリル化処理部6にてシリル化材料を付与して、当該主面に対してシリル化処理が施される。これにより、シリコン酸化膜の除去後、シリコンゲルマニウム膜の形成までのQタイムを長くするとともに、シリコンゲルマニウム膜の形成におけるプリベイクの温度を低くすることができる。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

マイクロ波プラズマ処理装置

【課題】 イオン分布を制御してイオンを含むマイクロプラズマにより面内均一性の高いプラズマ処理を実現することができるマイクロ波プラズマ処理装置を提供すること。

【解決手段】 誘電体からなるマイクロ波透過板28で天壁が構成されたチャンバー1内に、被処理体Wを載置する載置台2を設け、マイクロ波透過板28を透過したマイクロ波によってプラズマを形成し、該プラズマにより載置台2に載置された被処理体Wにプラズマ処理を施すマイクロ波プラズマ処理装置において、マイクロ波透過板28は、載置台2と対向して設けられ、そのマイクロ波透過面の少なくとも載置台2に載置された被処理体Wの周縁部における被処理体Wのエッジまでの領域に対応する部分に凹凸状部42を有し、被処理体Wの中央部に対応する部分は平坦部43となっている。

(もっと読む)

半導体装置

【課題】オフ電流を低減した優れた特性を有する薄膜トランジスタを作製する。

【解決手段】p型の逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜側から、微結晶半導体領域、非晶質半導体領域、及び不純物半導体領域が積層される半導体膜と、一対の配線とが接する領域が、ゲート絶縁膜を介してゲート電極と重畳し、一対の配線の仕事関数と、微結晶半導体領域を構成する微結晶半導体の電子親和力の差である電子のショットキーバリアφBnは0.65eV以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】大きなチャネル移動度を有する半導体装置及びその製造方法を提供する。

【解決手段】基板は、ポリタイプ4Hの六方晶の単結晶構造を有する半導体からなる表面SRを有する。基板の表面SRは、面方位(0−33−8)を有する第1の面S1と、第1の面S1につながりかつ第1の面S1の面方位と異なる面方位を有する第2の面S2とが交互に設けられることによって構成されている。ゲート絶縁膜は基板の表面SR上に設けられている。ゲート電極はゲート絶縁膜上に設けられている。

(もっと読む)

半導体装置の製造方法および成膜装置

【課題】半導体装置の特性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】HDP−CVD装置(1)の処理室内に半導体基板(100)を搬入し、半導体基板上に化学気相成長法により第1膜(例えば、酸化シリコン膜)を形成する。その後、リモートプラズマ装置(20)内から、Alを含有する材料よりなる配管であって、その内壁にコーティング材料層を有する配管(10)を通して、処理室内にラジカル化されたガス(例えば、フッ素ラジカル)を導入することにより処理室の内壁に付着した第1膜(例えば、酸化シリコン膜)を除去(クリーニング)する。かかる方法によれば、コーティング材料層により、発塵を低減し、クリーニング効率を向上することができる。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

振幅変調された高周波エネルギーを使用してゲート誘電体をプラズマ窒化するための方法及び装置

【課題】二酸化シリコン層及びシリコン基板を窒素イオンで過剰にダメージを生じさせることのないプラズマ窒化プロセスのための方法及び装置を提供する。

【解決手段】窒化ゲート誘電体層を形成するための方法及び装置。この方法は、電子温度スパイクを減少するために、滑らかに変化する変調のRF電源により処理チャンバー内に窒素含有プラズマを発生することを含む。電源が滑らかに変化する変調のものであるときには、方形波変調のものに比して、電界効果トランジスタのチャンネル移動度及びゲート漏洩電流の結果が改善される。

(もっと読む)

エピタキシャルウエハおよびその製造方法、半導体装置およびその製造方法

【課題】本発明は、結晶欠陥が少なく、キャリア時定数が十分大きい高品質なエピタキシャルウエハの製造方法と、当該エピタキシャルウエハを用いた半導体装置の製造方法の提供を目的とする。

【解決手段】本発明のエピタキシャルウエハの製造方法は、(a)3×1018cm-3以下の不純物濃度を有するSiC基板12上に、1×1014cm-3以上1016cm-3台以下の不純物濃度を有するエピタキシャル層13をエピタキシャル成長により形成する工程と、(b)前記工程(a)により得られた構造のSiC基板12の側から、エピタキシャル層13のうち所定の厚みを残して、SiC基板12の全部とエピタキシャル層13の一部とを連続的に除去する工程とを備える。

(もっと読む)

有機金属気相成長装置および成長方法、半導体装置およびその製造方法

【課題】P型、N型(I型)結晶を別々に形成する2チャンバ方式により、Mgのドーピングに伴う遅延効果およびメモリ効果を抑制し、エピタキシャル成長時間を短縮したMOCVD装置およびその成長方法、上記のMOCVD装置を適用して形成した半導体装置およびその製造方法を提供する。

【解決手段】水冷機構を備えるコールドウォール構造を備え、ガスの流れはウェハ8の表面に対して水平方向であり、P型層成長とN型(I型)層成長ではそれぞれ別のN型(I型)層成長用チャンバ14・P型層成長用チャンバ16で成長するように構成され、ウェハ8を保持するサセプタも別々のN型層成長用サセプタ3・P型層成長用サセプタ5を使用するMOCVD装置およびその成長方法、上記のMOCVD装置を適用して形成した半導体装置およびその製造方法。

(もっと読む)

1 - 20 / 459

[ Back to top ]