Fターム[5F045DA62]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の物性 (649)

Fターム[5F045DA62]の下位に属するFターム

バンドギャップ (149)

屈折率 (18)

光導電率・暗導電率 (7)

抵抗値 (59)

結晶欠陥密度・エッチピット密度・表面の面粗さ (221)

水素含有量・結合水素量 (37)

応力(圧縮、引張り)に特徴 (93)

密度 (4)

Fターム[5F045DA62]に分類される特許

41 - 60 / 61

SiCGe結晶薄膜の製造方法

【課題】複雑な処理を必要とせずに高濃度のGeを含有するSiCGe結晶を成長する方法を提供する。

【解決手段】基板上のSiGe結晶薄膜を炭化することによりSiCGe結晶薄膜を製造する。

(もっと読む)

原子層堆積法

本発明は、トランジスタに使用するための酸化亜鉛系薄膜半導体を製造する方法に関し、基板上に薄膜材料を堆積することを含み、第1、第2および第3ガス材料を含む複数のガス材料を提供することを含み、該第1又は第2ガス材料の一方が該基体の表面にある場合に、該第1又は第2ガス材料のもう一方が反応して該基体上に材料の層を堆積するように、該第1ガス材料は亜鉛含有揮発性材料であり、該第2ガス材料はそれと反応し、そして第3のガス材料は、該第1又は第2ガス材料との反応することに関して不活性である。  (もっと読む)

(もっと読む)

堆積膜形成方法及び光起電力素子の形成方法

【課題】 プラズマCVD法により移動する基板上に微結晶シリコンを含む堆積膜を形成する方法において、プラズマ状態の変化を少なくし、長時間安定なプラズマ状態を維持することを目的とする。

【解決手段】 プラズマCVD法により移動する基板上に微結晶シリコンを含む堆積膜を形成する方法であって、該基板上に静止状態で300nm以上の膜厚の堆積膜を形成した際に、該堆積膜中の結晶質に起因するラマン散乱強度がアモルファスに起因するラマン散乱強度の3倍以上である微結晶シリコン領域の面積が、全体の面積の50%以上となる条件で堆積膜を形成することを特徴とする。

(もっと読む)

プラズマCVD法によるシリコン系薄膜の形成方法

【課題】高周波励起のプラズマCVD法によるシリコン系薄膜の形成方法において、比較的低温下で安価に、生産性よく結晶化度の高い多結晶シリコン系薄膜を形成する。

【解決手段】成膜時のガス圧を0.0095Pa〜64Paの範囲から、成膜室内へ導入する成膜原料ガスの導入流量Msに対する希釈ガスの導入流量Mdの比(Md/Ms)を0〜1200の範囲から、高周波電力密度を0.0024W/cm3 〜11W/cm3 の範囲からそれぞれ選択、決定するとともに、成膜時のプラズマポテンシャルを25V以下、プラズマ中電子密度を1×1010個/cm3 以上に維持して膜形成し、且つ、それら圧力等の組み合わせをレーザラマン散乱分光法による膜中シリコンの結晶性評価においてアモルファスシリコン成分に起因するIaに対する結晶化シリコン成分に起因するIcの比(Ic/Ia=結晶化度)が8以上となる組み合わせとして多結晶シリコン系薄膜を形成する。

(もっと読む)

冷媒用マイクロチャネル含有III族窒化物半導体基板の製造方法

【課題】不所望の発熱を生じるIII族窒化物半導体デバイスを効率的に冷却し得る冷媒用マイクロチャネル含有III族窒化物半導体基板を提供する。

【解決手段】冷媒用マイクロチャネル含有III族窒化物半導体基板の製造方法は、III族窒化物半導体の基礎基板(1)の主面に概略直交する複数の貫通孔(2)を形成する工程と、その貫通孔に概略平行な一対の2平面に沿って、またはさらにその一対の2平面に交差する他の一対の2平面に沿って基礎基板を切り出すことによって、貫通孔の少なくとも一つを含む切片からなるIII族窒化物半導体基板(3)を得る工程とを含み、それによって、そのIII族窒化物半導体基板に含まれる貫通孔が冷媒を通過させるためのマイクロチャネルとして利用され得る。

(もっと読む)

エピタキシャルシリコンウェーハおよびその製造方法

【課題】{110}ウェーハにおいて、100nm以下のLPD測定可能とし、表面ラフネスの劣化を防止し、表面状態を判断可能とし、ウェーハの品質評価を可能とする。

【解決手段】シリコン単結晶の{110}面を傾けた面を主面とするシリコンウェーハにエピタキシャル層を成長させたエピタキシャルシリコンウェーハであって、

エピタキシャル層を成長させるシリコンウェーハは、前記{110}面を傾ける傾角度方位が、該{110}面に対して平行な<100>方位から<110>方向に対して0〜45°の範囲に設定されてなる。

(もっと読む)

キャリアライフタイムが改善された基板を製造する方法

本発明は、得られる基板が0.5マイクロ秒〜1000マイクロ秒のキャリアライフタイムを有するように、シリコンカーバイド材料を基板上に堆積させる方法であって、a.クロロシランガスと、炭素含有ガスと、水素ガスとを含む混合ガスを、基板を含有する反応チャンバ内に導入すること、及びb.1000℃より高いが2000℃より低い温度に基板を加熱することを含むが、但し、反応チャンバ内の圧力は0.1torr〜760torrの範囲に維持されるものとする、シリコンカーバイド材料を基板上に堆積させる方法に関する。本発明はまた、得られる基板が0.5マイクロ秒〜1000マイクロ秒のキャリアライフタイムを有するように、シリコンカーバイド材料を基板上に堆積させる方法であって、a.非塩素化ケイ素含有ガスと、塩化水素と、炭素含有ガスと、水素ガスとを含む混合ガスを、基板を含有する反応チャンバ内に導入すること、及びb.1000℃より高いが2000℃より低い温度に基板を加熱することを含むが、但し、反応チャンバ内の圧力は0.1torr〜760torrの範囲に維持されるものとする、シリコンカーバイド材料を基板上に堆積させる方法に関する。 (もっと読む)

受光素子アレイ、その製造方法、および光計測システム

【課題】 アレイ内における素子の大きさが均一で、しかもその形状が整っており、素子間で、受信光波長選択性を有し、しかも高濃度のNを含む半導体結晶を得ることにより、感度が良好な受光素子アレイ、その製造方法、および光計測システムを提供する。

【解決手段】 第1導電型または半絶縁性の半導体基板1上に、一次元または二次元に配列された複数の開口部を有するマスク層2を形成する工程と、前記開口部に受光層3bを含む複数の半導体層3a、3b、3cを選択成長させる工程とを含む。

(もっと読む)

成膜制御方法及び装置

【課題】 従来、光通信用の半導体レーザーは発振波長が微小(0.1nm〜0.2nm)に異なる物が求められているが、現在、制御機器の分解能不足、加熱機構の再現性の悪さ等により、半導体レーザー製造装置で製造条件を調整して発振波長に微小な差を付ける事が解決困難であった。そこで課題は、光通信用の半導体レーザーで発振波長が微小(0.1nm〜0.2nm)に異なる物を作り分ける方法及び装置を供する事にある。

【解決手段】 従来の半導体レーザー製造装置での製造条件にサセプターを傾けると言う条件を加えて上記課題を解決する。

(もっと読む)

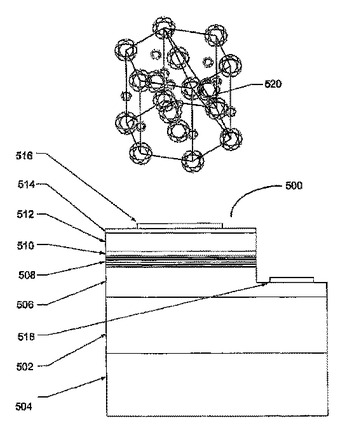

単結晶基板上にエピタキシャル成長したグラフェン層を含むデバイス

電子デバイスは、物質の主表面に単結晶領域を含む物質を含む。単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有し、グラフェンの少なくとも1つのエピタキシャル層がこの単結晶領域に配置される。現在好ましい実施形態では、単結晶領域は多層の六方晶BNを含む。このような電子デバイスの作製方法は、物質の主表面に単結晶領域を含む物質を提供し、単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有するステップ(a)と、この領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップ(b)を含む。現在好ましい実施形態では、ステップ(a)は、グラファイトの単結晶基板を提供するステップ(a1)と、基板に多層の単結晶六方晶BNをエピタキシャル形成するステップ(a2)とをさらに含む。六方晶BN層はグラフェンと実質的に格子整合した表面領域を有し、ステップ(b)は六方晶BN層の表面領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップを含む。FETへの応用が説明されている。  (もっと読む)

(もっと読む)

(Al,In,Ga,B)Nの伝導性制御方法

(Al,In,Ga,B)N半導体結晶におけるp型伝導性の制御方法が開示される。例えば、<011>方向にミスカットされた{100}MgAl2O4スピネル基板上に蒸着された{1011}GaN膜を含む。成長する半極性窒化薄膜にMg原子を意図的に内包し、使用可能な電子状態を半導体結晶のバンド構造に導入することによって、p型伝導性をもたらしてもよい。好適な電子状態の同様の内包をもたらすZnまたはCなどのその他の不純物原子を使用してもよい。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】装置の信頼性を向上させる。

【解決手段】エピタキシャル成膜層112において半導体基板11の主面である(100)面よりも、キャリア移動度として正孔移動度が大きいファセット面である(111)面を含む領域が、チャネル領域21cになるように、p型MOSトランジスタ21を形成する。

(もっと読む)

窒化ガリウム結晶基板、半導体デバイス、半導体デバイスの製造方法および窒化ガリウム結晶基板の識別方法

【課題】半導体デバイスの作製時にGaN結晶基板におけるクラックおよび割れの発生を低減することができるGaN結晶基板、それを含む半導体デバイス、その半導体デバイスの製造方法ならびにそのGaN結晶基板の識別方法を提供する。

【解決手段】面積が10cm2以上の表面を有するGaN結晶基板であって、GaN結晶基板の表面の周縁から5mm内側までの領域を除いた領域内におけるE2Hフォノンモードに対応するラマンシフトの最大値と最小値との差が0.5cm-1以下であるGaN結晶基板、それを含む半導体デバイス、その半導体デバイスの製造方法ならびにそのGaN結晶基板の識別方法である。

(もっと読む)

SiCエピタキシャルウエーハおよびそれを用いた半導体デバイス

【課題】優れた性能を有するSiC単結晶とそのエピタキシャル成長方法を提供する。かかるSiCエピタキシャル単結晶を用いて作製された、ウエーハと半導体デバイスを提供する。

【解決手段】SiC基板の面を、(0001)面から5.74度±1度以内または2.86度±0.7度以内のオフ角に設定して、前記SiCの基板上にSiCの結晶をエピタキシャル成長させる工程を有しているSiCエピタキシャルウエーハの製造方法。前記オフ角が、(0001)面から5.74度±0.5度以内または2.86度±0.5度以内であるSiCエピタキシャルウエーハの製造方法。前記オフ角が、(0001)面から5.74度±0.3度以内または2.86度±0.3度以内であるSiCエピタキシャルウエーハの製造方法。SiC基板が、SiC基板上に改良レーリー法により堆積されたSiC結晶から作製されたものであるSiCエピタキシャルウエーハの製造方法。

(もっと読む)

GaN系化合物半導体層の形成方法、及び、GaN系半導体発光素子の製造方法

【課題】結晶欠陥密度が低く、しかも、ピエゾ自発分極が生じ難いGaN系化合物半導体層の形成方法を提供する。

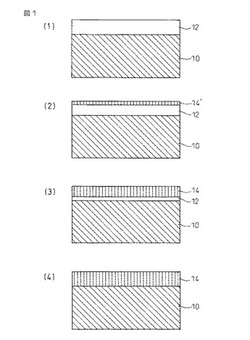

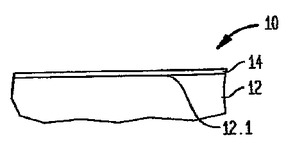

【解決手段】GaN系化合物半導体層の形成方法は、(A)サファイア基板10のR面上に、GaN系化合物半導体から成り、離間したシード層11を複数形成した後、(B)頂面が、A面であり、且つ、サファイア基板10のR面に対して略平行な状態にあるGaN系化合物半導体層12,14を、各シード層11から横方向エピタキシャル成長させ、次いで、(C)GaN系化合物半導体層12,14の頂面14Aを研磨して、サファイア基板10のR面に対して傾斜した状態とする工程を具備する。

(もっと読む)

半極性(Ga,Al,In,B)N薄膜、ヘテロ構造およびデバイスの成長と作製のための方法及び装置

特定のデバイス応用に対する所望の材料特性を同定するステップと、前記所望の材料特性に基づいて半極性成長方位を選択するステップと、選択された半極性成長方位の成長のための適当な基板を選択するステップと、前記基板上に平坦な半極性(Ga,Al,In,B)Nテンプレートまたは核形成層を成長するステップと、および前記平坦な半極性(Ga,Al,In,B)Nテンプレートまたは核形成層上に半極性(Ga,Al,In,B)N薄膜、ヘテロ構造あるいはデバイスを成長するステップとを備えた半極性(Ga,Al,In,B)N薄膜、ヘテロ構造、およびデバイスの成長と作製の方法が提供される。前記の方法を用いることにより基板表面に平行な、大きな面積をもつ半極性(Ga,Al,In,B)N薄膜、ヘテロ構造、およびデバイスが実現できる。  (もっと読む)

(もっと読む)

半導体発光素子の製造方法

【課題】 Nを含む混晶半導体に適した低い成長温度においても、Alを含んだ層の成長表面に製造装置内や原料ボンベ内のO(酸素)が取り込まれて素子の劣化の起源となる非発光再結合センターを低減させ、発光効率が高く、寿命の長い半導体発光素子の製造方法を提供する。

【解決手段】 Alを含んだ層を有し、V族としてNと他のV族を含む混晶半導体材料からなる活性層または井戸層を有し、前記Alを含んだ層の成長温度より活性層または井戸層の成長温度が低い半導体発光素子の製造方法であって、

前記Alを含んだ層を成長する工程と、活性層または井戸層を成長する工程との間に、活性層または井戸層と直接接する半導体層としてAlを含まない半導体層を成長する工程を有する。

(もっと読む)

結晶窒化ガリウムベースの化合物の成長方法及び窒化ガリウムベース化合物を含む半導体デバイス

【課題】基板との格子不整合を補償出来かつ紫外線放射の吸収を減少するような改良された特性を現わす、結晶GaNベース材料を成長する方法を提供すること。

【解決手段】結晶GaNベース材料を形成する方法において、第1の核生成層が、第1の温度で基板上に形成され、それに続いて、第1の温度とは異なる第2の温度で第2の核生成層を形成する。第1と第2の核生成層は、AlxInyGa(1-x-y)Nよりなる。引き続いて、結晶GaNベース化合物の層が、第2の核生成層上にエピタキシ成長される。

(もっと読む)

窒化ガリウム系化合物半導体およびその製造方法

【課題】 従来のSi半導体製造プロセスを利用して、大口径の基板として得ることができ、製造効率およびコスト面においても優位である窒化ガリウム系化合物半導体およびその製造方法を提供する。

【解決手段】 Si単結晶基板1表面にβ−SiC層を気相成長により積層させて、厚さ0.1μm以上5μm以下のβ−SiC層2からなる中間層を形成し、前記中間層の上に、窒化ガリウム系化合物層3を気相成長させることにより、窒化ガリウム系化合物半導体を製造する。

(もっと読む)

シリコンゲルマニウムエッチング停止層システム

【課題】水性異方性エッチング剤に対して有用な、シリコン基板上のSiGeエッチング停止構造物を提供する。

【解決手段】SiGeエッチング停止構造物が、Si1−xGexまでの段階が設けられた弛緩されたバッファ層と、Si1−yGeyの弛緩された均質なエッチング停止層とを有しており、x≦0.17、y≧0.3が好ましい。バッファ層は、基板/バッファとの界面における純粋シリコンからゲルマニウム組成にかけて、その厚みに対して一次的に変化する構成を有し、さらに、バッファ/エッチング停止界面に化学的不純物質を有する。界面のバッファサイドからエッチング停止物質にかけて、エッチング停止層がエッチング剤に対して非常に抵抗力があるように、ゲルマニウムおよび濃度において計画的な飛躍を行う。

(もっと読む)

41 - 60 / 61

[ Back to top ]