Fターム[5F048AC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | MOS+MOS (7,604) | パワーMOSを含む (667)

Fターム[5F048AC06]に分類される特許

81 - 100 / 667

半導体チップ、半導体装置、及び半導体チップの製造方法

【課題】2次電池パックの保護回路を更に小型化すること。

【解決手段】本発明に係る半導体チップは、双方向スイッチを構成する2個のパワートランジスタと、抵抗素子とを備える。2個のパワートランジスタのドレイン同士は接続されている。抵抗素子の一端は、2個のパワートランジスタのうち一方のソース電極と電気的に接続され、その他端は、第1外部パッドと電気的に接続されている。それら2個のパワートランジスタと抵抗素子とは、同一の半導体チップ上に形成されている。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供することにある。

【解決手段】半導体基板10内に形成された第1導電型の第1の不純物領域32、46と、半導体基板内に形成され、第1の不純物領域に隣接する第2導電型の第2の不純物領域34、48と、第2の不純物領域内に形成された第1導電型のソース領域30a、44aと、第1の不純物領域内に形成された第1導電型のドレイン領域30b、44bと、ソース領域とドレイン領域との間における第1の不純物領域内に、第2の不純物領域から離間して埋め込まれた、二酸化シリコンより比誘電率が高い絶縁層14と、ソース領域とドレイン領域との間における第1の不純物領域上、第2の不純物領域上及び絶縁層上に、ゲート絶縁膜22を介して形成されたゲート電極24a、24bとを有している。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲート電極を備えるトレンチゲート構成のパワーMISFETにおいて、MISFETの性能向上を図りながら、ゲート絶縁膜の静電破壊を防止することができる技術を提供する。

【解決手段】ダミーゲート電極9aを備えるトレンチゲート構成のパワーMISFETと保護ダイオードとを同一の半導体基板1上に形成する。そして、保護ダイオードをソース電極24とゲート配線25の間に設ける。このような半導体装置の製造方法において、ダミーゲート電極9a用のポリシリコン膜と保護ダイオード用のポリシリコン膜を同時に形成する。また、パワーMISFETのソース領域と保護ダイオードのn+型半導体領域15を同一工程で形成する。

(もっと読む)

半導体装置

【課題】接続配線に起因する耐圧低下を防止できる半導体装置の耐圧特性をさらに向上させることができる半導体装置の提供。

【解決手段】半導体層の第1素子領域に配置されており、第1主電極と第2主電極を有する第1種類の第1半導体素子と、半導体層の第2素子領域に配置されており、第3主電極と第4主電極を有する第2種類の第2半導体素子とを備え、第1素子領域と第2素子領域は、電流が流れる方向に対して直交する方向に隣接し、かつ、第1素子領域と第2素子領域を含む素子領域全体で一巡する形に形成され、半導体層を平面視したときに、第1素子領域の曲率は、第2素子領域の曲率よりも小さい。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置

【課題】トレンチゲートをゲート電極で完全に埋め込むトレンチゲート型MOSFETにおいて、パフォーマンスに優れた半導体回路装置を提供する。

【解決手段】第1の導電型のウェル層4内に形成された第2の導電型のウェル層5が、ゲート電極材料9で埋設された格子状のトレンチ溝7で囲まれたトレンチゲート型MOSFETであって、トレンチ溝7の側面と第2の導電型のウェル層5との間に形成される第1の絶縁膜8は、トレンチ溝7の側面と前記第1の導電型のウェル層4との間に形成される第2の絶縁膜14よりも薄くしてある。

(もっと読む)

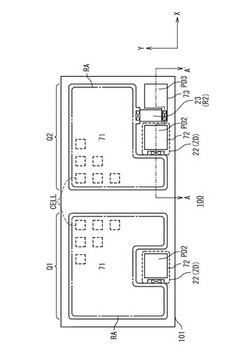

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタ部のオン抵抗を下げ、かつショットキーバリアダイオード部のリーク電流を抑制する。

【解決手段】半導体装置は、第1の半導体層と、第2の半導体層と、第3の半導体層と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第1のトレンチ内に、第1の絶縁膜を介して設けられた埋め込み電極と、埋め込み電極の上に、第2の絶縁膜を介して設けられた制御電極と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第2のトレンチの下端に接続され、第1の半導体層内に選択的に設けられた第4の半導体層と、第1の半導体層に接続された第1の主電極と、第2のトレンチ内に設けられた第2の主電極と、を備える。第2のトレンチの側壁において、第2の主電極と、第1の半導体層と、によるショットキー接合が形成されている。

(もっと読む)

横型ダイオードを有する半導体装置

【課題】ホール注入を抑制して逆回復耐量の向上を図りつつ、アバランシェ耐量の向上を図ることができる横型ダイオードを有する半導体装置を提供する。

【解決手段】アノード電極11がp-型低不純物濃度領域7に対してショットキー接触もしくはオーミック接触させられ、かつ、p+型高不純物濃度領域8にオーミック接触させられるようにする。また、p-型低不純物濃度領域7およびp+型高不純物濃度領域8よりもカソード電極10から離れる側にp+型アノード拡張領域9を備える。このように、アノード電極11がp-型低不純物濃度領域7に対して電気的に接続されるようにすれば、電子注入が少なくなることで、同じ量の電流を流してもホール注入を少なくでき、逆回復電荷Qrrを低減して逆回復耐量を向上することが可能となる。また、p+型アノード拡張領域9を備えことで、アバランシェ耐量を向上させることも可能となる。

(もっと読む)

半導体装置

【課題】IGBT素子領域からダイオード素子領域へのホールの注入を抑制することができ、さらに耐圧を確保できる構造を備えた半導体装置を提供する。

【解決手段】ダイオードセル20において、IGBTセル10のトレンチ38よりも深く、チャネル層37よりも面密度が小さいアノードとしてのP型のリサーフ領域52が形成され、このリサーフ領域52の表層部にP+型の第2コンタクト領域55が形成されている。これにより、チャネル層37によってドリフト層33に形成される空乏層とリサーフ領域52によってドリフト層33に形成される空乏層とがIGBTセル10とダイオードセル20との境界付近で滑らかに接続されるので、当該境界付近における電界集中を緩和することができ、半導体装置の耐圧を確保することができる。

(もっと読む)

半導体装置

【課題】2つのトランジスタを混載した半導体装置において、ダミー配線を介して配線間で短絡が発生するのを防止し、信頼性の高い混載デバイスを実現可能にする。

【解決手段】本発明の半導体装置は、微細CMOS4Aと、微細CMOS4Aに接続される微細配線15とを有する微細CMOS領域と、微細CMOS4Aよりも耐圧が高い高耐圧デバイス4Bと、高耐圧デバイス4Bに接続され、平面視において微細配線15よりも配線幅が広いドレイン配線115及びソース配線116と、を有する高耐圧デバイス領域と、を具備し、高耐圧デバイス領域には、電気的に孤立したダミー配線14が少なくともドレイン配線115及びソース配線116に隣接して配置されない。

(もっと読む)

81 - 100 / 667

[ Back to top ]