Fターム[5F048AC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | MOS+MOS (7,604) | パワーMOSを含む (667)

Fターム[5F048AC06]に分類される特許

121 - 140 / 667

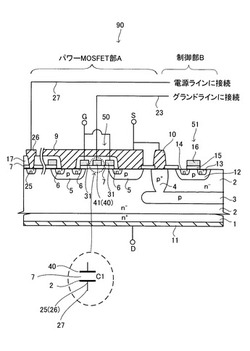

半導体装置

【課題】絶縁ゲート型電界効果トランジスタのスイッチング速度低下を防止し、省スペース化を実現する半導体装置を提供する。

【解決手段】本発明に係る半導体装置90は、絶縁ゲート型電界効果トランジスタとコンデンサが同一チップ上に形成されたものであって、表層において、n−型エピタキシャル層2を挟持するp型ボディ領域5内にそれぞれ配設されたn+型ソース領域6の当該n−型エピタキシャル層2に最近接する端部間に亘る領域上に配設された絶縁層7と、絶縁層7を介してn−型エピタキシャル層2と対向されるコンデンサ上部電極40と、絶縁層7上でコンデンサ上部電極40の両サイドに絶縁分離されるように、かつチャネル形成可能な位置に配設されたゲート電極31を備える。コンデンサC1は、コンデンサ上部電極40を上部電極とし、これと絶縁層7を介して対向配置されるn−型エピタキシャル層2を下部電極とする。

(もっと読む)

半導体デバイスおよび方法

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】第1の主電極と、第1の主電極の上に設けられた第1導電型のベース層と、第1導電型のベース層の上に設けられ、交互に配列された第1導電型のバリア層および第2導電型の拡散層と、第1導電型のバリア層の上に設けられた第2導電型のベース層と、第2導電型のベース層および第1導電型のバリア層と、第2導電型の拡散層との間に絶縁膜を介して設けられたトレンチ状の第1および第2の導電体層と、第2導電型のベース層に接続された第2の主電極と、を備え、第1導電型のバリア層および第2導電型の拡散層の底面は、第1および第2の導電体層の下端よりも第1の主電極側に位置し、第1導電型のバリア層と第2導電型の拡散層とは、第1および第2の導電体層の先端近傍で超接合を形成していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、従来の製造方法と比較し、同一ウエハまたは製品上において複数のデバイス耐圧帯と良好なオン抵抗をもったLDMOSを備えた半導体装置およびその製造方法を提供することを目的とするものである。

【解決手段】 第1電界緩和用酸化膜24と第2電界緩和用酸化膜25と素子分離用LOCOS酸化膜17の膜厚を別々に最適化することにより、同一ウエハにおいて複数のデバイス耐圧と良好なオン抵抗を実現する。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】半導体装置の耐圧を向上させ、より高速のスイッチング動作を可能にする。

【解決手段】第1導電型の半導体層の第1主面側に選択的に設けられた第2導電型のベース領域と、ベース領域内に選択的に設けられた第1導電型の拡散領域と、拡散領域に接触しベース領域を貫通して半導体層にまで到達するトレンチ内に絶縁膜を介して設けられた制御電極と、半導体層の第1主面側から第2主面側の方向に延伸し、ベース領域とは離間して設けられた、少なくとも1つの第2導電型の第1の半導体領域と、隣り合うトレンチ間に、トレンチとは離間して設けられた第2導電型の第2の半導体領域と、拡散領域、半導体層、第1の半導体領域および第2の半導体領域に電気的に接続された第1の主電極と、半導体層の第2主面側に電気的に接続された第2の主電極と、を備え、第2の半導体領域は、ベース領域を貫通して半導体層にまで到達している。

(もっと読む)

ESD保護回路及び半導体装置

【課題】信号電圧が電源電圧を正負両方向に越えるようなチップ端子に対し適切に動作するESD保護回路を提供する。

【解決手段】ESD保護回路は、端子に一端のP側が接続されグラウンドに他端のN側が接続されるPNPN接合と、グラウンドにP側が接続されるPN接合のN側にソース及びゲートが接続され、前記の端子にドレインが接続されるPMOSトランジスタとを含む。

(もっと読む)

トレンチゲート型半導体装置

【課題】飽和電流までの電流を正確に検出できるトレンチゲート型半導体装置を提供する。

【解決手段】本発明のトレンチゲート型半導体装置は、主IGBT領域とセンスIGBT領域とにそれぞれチャネルを形成したアクティブセルと、チャネルを形成していないフローティングセルとを交互に配置し、主IGBT領域とセンスIGBT領域のアクティブセルの幅とフローティングセルの幅との比を所定の値に設定して主IGBT領域とセンスIGBT領域とが同様な飽和電流特性になるように制御した。

(もっと読む)

半導体装置

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】半導体チップCP1には、スイッチ用のパワーMOSFETQ1,Q2と、パワーMOSFETQ1の発熱を検知するためのダイオードDD1と、パワーMOSFETQ2の発熱を検知するためのダイオードDD2と、複数のパッド電極PDとが形成されている。パワーMOSFETQ1およびダイオードDD1は、辺SD1側の第1MOSFET領域RG1に配置され、パワーMOSFETQ2およびダイオードDD2は、辺SD2側の第2MOSFET領域RG2に配置されている。ダイオードDD1は辺SD1に沿って配置され、ダイオードDD2は辺SD2に沿って配置され、ダイオードDD1,DD2間にソース用のパッド電極PDS1,PDS2以外の全てのパッド電極PDを辺SD3に沿って配置している。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離領域が低濃度拡散領域におけるゲート電極近傍の部分より浅い場合に半導体装置の平面寸法の大型化を抑制しつつ素子分離をより確実に行う。

【解決手段】半導体装置100は、第1導電型の不純物領域(N型ウェル領域51)と、第2導電型の低濃度拡散領域(P型オフセット拡散領域3)を有する複数のMOSトランジスタ(高圧PチャネルMOSトランジスタ11)と、素子分離領域6を有する。低濃度拡散領域は、素子分離領域6に接する第1部分3aは素子分離領域6と同じ深さであるか又はそれよりも浅く、第1部分3aよりもゲート電極1側の第2部分3bは素子分離領域6よりも深い。更に、第1導電型であり、不純物領域よりも不純物濃度が高く、素子分離領域6の底面と、素子分離領域6に隣接する低濃度拡散領域の各々とに接しているチャネルストッパー領域(N型チャネルストッパー領域9)を有する。

(もっと読む)

絶縁ゲート型半導体装置

【課題】低オン電圧と低スイッチング損失とを両立することができる絶縁ゲート型半導体装置を提供する。

【解決手段】間引き型のIGBT素子において、ダミーセルのP型のフロート層18にN型のホールストッパー層19を設ける。また、このホールストッパー層19により分割された第1の層18aをエミッタ電極21に接地する。これにより、コレクタ電極24からフロート層18を介してゲート電極17に到達する経路に形成される帰還容量の中に溜まる電荷はほとんど無くなるため、スイッチング損失を低減できる。さらに、P型のフロート層18に設けられたN型のホールストッパー層19が電位の壁となるので、半導体基板10からフロート層18を介してエミッタ電極21にホールが抜けてしまうことを抑制することができる。このため、半導体基板10の抵抗が下がり、IGBT素子のオン電圧を下げることができる。

(もっと読む)

半導体素子の保護回路

【課題】横方向二重拡散MOSトランジスタ(LDMOS)の特性を悪化させることがなく、回路素子サイズの増大や各素子の製造時のばらつきの影響を抑えることができる、半導体素子の保護回路を提供する。

【解決手段】LDMOS110のバックゲートの出力をトリガーとして用い、LDMOSのドレインに接続される出力端子120に印加されるESDサージを、直列に接続された高耐圧MOS140及び低耐圧MOS142を経て接地端子122に流す。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

半導体装置

【課題】パワーMOSFETを備える半導体装置のコストの低減を図る。

【解決手段】半導体装置1では、P型の半導体基板2上に、N型の半導体層3が積層されている。そして、半導体装置1は、LDMOS領域5に、ボディ領域8、ドレインバッファ領域9、ソース領域11およびゲート電極14などからなるLDMOSFETを備えている。すなわち、半導体装置1は、LDMOSFETを備えながら、厚膜SOI基板ではなく、N型の半導体層3が直上に設けられたP型の半導体基板2を採用している。そして、フィールド絶縁膜13上に7つのフィールドプレート15が設けられ、そのフィールドプレート15の間隔がボディ領域8側(ソース領域11側)ほど小さくされている。

(もっと読む)

トレンチ型絶縁ゲート半導体装置及びその製造方法

【課題】トレンチ型絶縁ゲート半導体素子と多結晶シリコンダイオードを同一チップ上に形成して性能を高める。

【解決手段】本発明では、半導体基板上の半導体層の主面に形成されたトレンチ型絶縁ゲート半導体素子のトレンチ溝の外側には、トレンチ溝に連なる多結晶シリコン層を形成する。また、トレンチ溝の外側には、前記トレンチ溝に連なる多結晶シリコン層とは別の多結晶シリコン層が形成され、この多結晶シリコン層には多結晶シリコンダイオードが形成され、そして、この多結晶シリコンダイオードが形成された多結晶シリコン層の膜厚が、前記トレンチ溝に連なる多結晶シリコン層の膜厚よりも薄くなるように形成することを特徴とする。

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

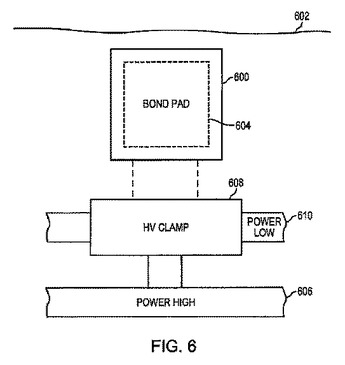

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

パワー・スイッチの構造および方法

【課題】低RDSonおよび低電流制限の両方を提供する一方で、ホット・スポットおよび熱暴走の効果を低減する回路を提供する。

【解決手段】本発明の一実施例において、パワー・スイッチング・デバイス(33)は、第1MOSFETデバイス(41)および第2MOSFETデバイス(42)を含む。第1ゲート電極(48,87)を含む分割ゲート構造(84)は、第1MOSFETデバイス(41)を制御する。第2ゲート電極(49,92)は、第2MOSFETデバイス(42)を制御する。電流制限デバイス(38)は、第1ゲート電極(48,97)に結合され、電流制限モード中に第1MOSFETデバイスをオンにする。比較器デバイス(36)は、第2ゲート電極(49,92)に結合され、パワー・スイッチング・デバイス(33)が電流制限モードでなくなったときに、第2MOSFETデバイス(42)をオンにする。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

半導体装置、二次電池保護装置および半導体装置の製造方法

【目的】特性が改善された半導体装置および充放電制御装置を提供することにある。また、低コストであり生産性が向上された半導体装置の製造方法を提供することである。

【解決手段】トレンチ3の両側壁に形成する2つのMOSFETにおいて、1つのMOSFETの第1pベースピックアップ領域41の配置間隔を別のMOSFETの第2pベースピックアップ領域51の配置間隔に比べて広くする。

前記第1pベースピックアップ領域41および第2pベースピックアップ領域51を形成する際のレジストマスク63をトレンチ3に隣接する第1pベース領域4および第2pベース領域を覆うように形成して、不純物のイオン注入を行う。

(もっと読む)

121 - 140 / 667

[ Back to top ]