Fターム[5F048BB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378)

Fターム[5F048BB01]の下位に属するFターム

分割ゲート(複数ゲート) (414)

ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB01]に分類される特許

21 - 40 / 1,325

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

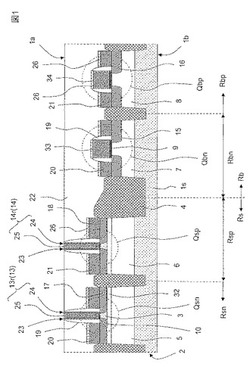

半導体装置

【課題】 ゲート長方向に対し水平に複数本のトレンチを形成することにより単位面積当たりのゲート幅を増大させる高駆動能力横型MOSにおいて、素子面積を増加させずに更に駆動能力を向上させる。

【解決手段】 半導体基板表面から一定の深さに設けられた高抵抗第一導電型半導体のウェル領域と、前記ウェル領域の表面から途中の深さまで達する複数本のトレンチと、前記トレンチが形成する凹凸部の表面に設けられたゲート絶縁膜と、前記トレンチ内部に埋め込まれたゲート電極と前記トレンチ両端付近を除く前記凹凸部領域において前記トレンチ内部に埋め込まれたゲート電極と接触して基板表面に設けられたゲート電極膜と、前記ゲート電極膜と接触して前記トレンチ両端付近のトレンチ内部に半導体基板表面より深い位置に表面が位置するように埋め込まれたゲート電極膜と、前記ゲート電極膜と接触していない半導体面から前記ウェル領域の深さより浅く設けられた2つの低抵抗第二導電型半導体層であるソース領域とドレイン領域を有する半導体装置とした。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用ボトムコンタクト型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。多階調マスクを用いたフォトリソグラフィ工程を用いることで、作製工程を簡略化できる。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

21 - 40 / 1,325

[ Back to top ]