Fターム[5F048BB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378)

Fターム[5F048BB01]の下位に属するFターム

分割ゲート(複数ゲート) (414)

ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB01]に分類される特許

161 - 180 / 1,325

半導体装置

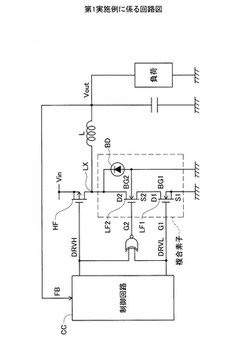

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

(もっと読む)

多結晶シリコン半導体素子及びその製造方法

【課題】多結晶シリコン半導体素子及びその製造方法を提供する。

【解決手段】ゲート共通化ラインに存在するシリコン物質層による寄生キャパシタンスを減少させるために、製造工程中にゲート以外の他の部分の不要なシリコン物質を除去する。シリコン物質層は、ゲートの下部のみに局地的に存在し、したがって、寄生キャパシタンスの減少によって信号遅延が抑制されて良好な電気的特性を有する薄膜トランジスタの多結晶シリコン半導体素子が得られる。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にhigh−k膜を使用したMIS構造の半導体装置において、互いに異なる仕事関数を有する複数の同一導電型トランジスタを設けることを可能にする。

【解決手段】同じ導電型の第1のMISトランジスタ及び第2のMISトランジスタが同じ半導体基板50上に設けられている。第1のMISトランジスタにおけるゲート絶縁膜52aの界面層2Aの厚さは、第2のMISトランジスタにおけるゲート絶縁膜52bの界面層2bの厚さよりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく、高耐圧トランジスタへのイオン注入を的確に実行することを可能にする。

【解決手段】

第1素子形成領域(AA1)のうち、第1トランジスタ(Tr1)のゲート電極が形成されるべき第1領域(R1’)の直上に位置するマスク材(M1)の第1部分(H1’)を除去する一方、第1部分(H1’)以外の第1素子形成領域(AA1)にはマスク材(M1)を残存させる。一方、第2素子形成領域(AA2)のうち、第2トランジスタ(Tr2)のゲート電極が形成されるべき第2領域(R1)の直上に位置するマスク材の少なくとも第2部分(H1)と、第2トランジスタ(Tr1)のソース/ドレイン拡散領域が形成されるべき第3領域(R2、R3)の直上に位置するマスク材の少なくとも第3部分(H2,H3)とを除去してマスク材の開口を形成する。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体装置およびその製造方法

【課題】動作マージンの向上に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体基板上に、互いのゲート電極が接続されて配置される第1トランジスタ(P2)と、前記第1トランジスタと異なる導電型を有する第2トランジスタ(N4)とを具備し、前記第1トランジスタのゲート電極は、第1不純物と前記第1不純物の拡散を抑制する第2不純物とを含有し、前記第1不純物の濃度ピーク(PE1)は、前記第2不純物の濃度ピーク(PE2)よりも浅い位置に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタ部のオン抵抗を下げ、かつショットキーバリアダイオード部のリーク電流を抑制する。

【解決手段】半導体装置は、第1の半導体層と、第2の半導体層と、第3の半導体層と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第1のトレンチ内に、第1の絶縁膜を介して設けられた埋め込み電極と、埋め込み電極の上に、第2の絶縁膜を介して設けられた制御電極と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第2のトレンチの下端に接続され、第1の半導体層内に選択的に設けられた第4の半導体層と、第1の半導体層に接続された第1の主電極と、第2のトレンチ内に設けられた第2の主電極と、を備える。第2のトレンチの側壁において、第2の主電極と、第1の半導体層と、によるショットキー接合が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】高い比精度が要求される複数のトランジスタの特性ばらつきを低減する。

【解決手段】本発明の半導体装置は、半導体基板上に配置されたトランジスタTr1と、半導体基板上で見たキャリアのドリフト方向がトランジスタTr1のキャリアのドリフト方向と同じ方向となる向きに配置されたトランジスタTr2と、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51b同士を接続する拡散層51cと、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51bまたはその拡散層同士を接続する拡散層51cの表面に接続され、拡散層51a,51bに給電するためのコンタクトプラグ61と、を備える。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置及びその製造方法

【課題】生産性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、シリコン基板101と、同一のシリコン基板101上に設けられたN型トランジスタ200およびP型トランジスタ202と、を備え、N型トランジスタ200およびP型トランジスタ202は、Hfを含む高誘電率ゲート絶縁膜108と、高誘電率ゲート絶縁膜108上に設けられたTiN膜110と、を有しており、N型トランジスタ200は、シリコン基板101と高誘電率ゲート絶縁膜108との間に、La添加SiO2膜109aを有しており、P型トランジスタ202は、高誘電率ゲート絶縁膜108とTiN膜110の間に、N型トランジスタ200と同じ仕事関数調整用元素を含有するLa添加SiO2膜109bを有する。

(もっと読む)

半導体集積回路及び半導体集積回路装置

【課題】従来技術と比較して占有面積が小さく、かつ基板電流が流れる経路の抵抗を低く抑え、寄生バイポーラトランジスタの動作を抑制することができる半導体集積回路及び半導体集積回路装置を提供する。

【解決手段】p型半導体基板10に形成されたドレイン領域D1、ソース領域S1、及びp型活性領域Bと、ドレイン領域D1とソース領域S1との間に形成されたゲート電極TG1と、ドレイン電極TD1と、ソース電極TS1と、基板電極TB1とを備えたNMOSトランジスタMN1と、ソース領域S1とp型活性領域Bとの間に形成されたドレイン領域D2及びソース領域S2と、p型活性領域Bと、ドレイン領域D2とソース領域S2との間に形成されたゲート電極TG2と、ドレイン電極TD2と、ソース電極TS2と、基板電極TB2とを備えたNMOSトランジスタMN2とを備え、NMOSトランジスタMN2は、基板電極TB1とソース電極TS1との間に接続される。

(もっと読む)

半導体装置の製造方法

【課題】 側壁部及び上部の平面部を持つ立体凹凸部分を形成した三次元デバイスとしての半導体装置において側壁部及び上部の平面部へ均一に高濃度の不純物を低エネルギードーピングできる方法を提供する。

【解決手段】 シリコン基板1の表面上に加工によりシリコンFin部11を形成した後、該シリコンFin部の側壁及び上部の平面部へドナーもしくはアクセプターとなる不純物原子を含む不純物薄膜を、堆積膜として上部の平面部には厚く、側壁には薄く堆積する工程と、前記シリコンFin部における前記堆積膜の斜め上方から斜め方向のイオン注入と反対側の斜め上方から斜め方向のイオン注入を行なうとともに、該イオン注入によって、前記不純物原子を堆積膜内部からシリコン基板の前記シリコンFin部の側壁内部及び上部の平面部内にリコイルして導入させる工程と、を含む。

(もっと読む)

161 - 180 / 1,325

[ Back to top ]