Fターム[5F048BB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378)

Fターム[5F048BB01]の下位に属するFターム

分割ゲート(複数ゲート) (414)

ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB01]に分類される特許

121 - 140 / 1,325

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

埋め込みドープ層を有する完全空乏型SOIデバイス

【課題】完全空乏型SOIデバイスの製造に適したセミコンダクタオンインシュレータ(SeOI)ウェーハおよびそれを用いたデバイスを提供すること。

【解決手段】本発明は、第1の基板の表面領域にドープ層、ドープ層上に埋め込み酸化物層、埋め込み酸化物層上に半導体層を形成してSeOIウェーハを得る。SeOIウェーハの第2の領域の埋め込み酸化物層および半導体層を維持しながらSeOIウェーハの第1の領域から埋め込み酸化物層および半導体層を除去し、第2の領域に上部トランジスタを形成する。第1の領域にリセスチャネルアレイトランジスタを形成し、第2の領域にpチャネルトランジスタおよび/またはnチャネルトランジスタを形成する。ドープ層内またはこの近傍にバックゲートを形成し、第1の領域にリセスチャネルアレイトランジスタを形成し、ドープ層内またはその近傍にソース領域およびドレイン領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

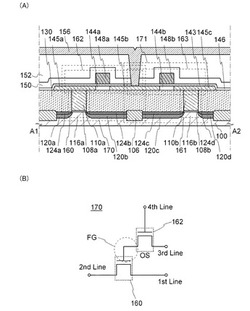

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数やコストを増加させることなく、信頼性の高い高耐圧pチャネル型トランジスタが形成された半導体装置を提供する。

【解決手段】主表面を有し、かつ内部にp型領域を有する半導体基板SUBと、p型領域PSR上であって主表面に配置された、ドレイン電極DRを取り出すための第1のp型不純物領域PRを有するp型ウェル領域PLDと、主表面に沿う方向に関してp型ウェル領域PLDと接するように配置された、ソース電極SOを取り出すための第2のp型不純物領域PRを有するn型ウェル領域NWRと、主表面に沿う方向に関して、第1のp型不純物領域PRと第2のp型不純物領域PRとの間に配置されたゲート電極GEと、n型ウェル領域NWRの上に配置された、主表面に沿って延びるp型埋め込みチャネルPPRとを含んでいる。上記n型ウェル領域NWRとp型ウェル領域PLDとの境界部は、ゲート電極GEの、第1のp型不純物領域PRに近い側の端部よりも、第1のp型不純物領域PRに近い位置に配置される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置

【課題】低消費電力で高速シリアル伝送が可能な半導体装置を提供する。

【解決手段】実施形態によれば、インタフェース部と、駆動回路部と、スイッチ部と、電源回路部と、を備えた半導体装置が提供される。前記インタフェース部は、フローティング状態のバックゲートを有しSOI基板上に設けられた第1のMOSFETを含み、入力したシリアルデータの端子切替信号をパラレルデータに変換する。前記電源回路部は、ソースに接続されたバックゲートを有し前記SOI基板上に設けられた第2のMOSFETを含み、前記インタフェース部に供給される電源の電位よりも高いオン電位を生成する。前記駆動回路部は、ソースに接続されたバックゲートを有し前記SOI基板上に設けられた第3のMOSFETを含み、前記パラレルデータに応じて、前記オン電位をハイレベルとする制御信号を出力する。前記スイッチ部は、前記SOI基板上に設けられ、前記制御信号を入力して端子間の接続を切り替える。

(もっと読む)

半導体装置の製造方法

【課題】基板に対して斜め方向からイオン注入を行う工程を含む半導体装置の製造方法においてゲート電極サイズの縮小化とリーク電流特性の改善を両立することができる製造方法を提供する。

【解決手段】

半導体基板の表面にゲート電極を形成する。ゲート電極のゲート長方向と交差するゲート幅方向における両端面を被覆するレジストマスクを形成する。半導体基板にゲート長方向成分およびゲート幅方向成分を有する注入方向で不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極とオーバーラップした低濃度不純物層を形成する。ゲート電極の側面を覆うサイドウォールを形成する。ゲート電極およびサイドウォールをマスクとして不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極から離間した高濃度不純物層を形成する。

(もっと読む)

半導体装置

【課題】チップ面積を大きくすることなく、チップの空いている外周部分を利用しながら、直列抵抗が小さく、かつ、充分に保護機能を果たすことができる保護ダイオードを有する半導体装置を提供する。

【解決手段】半導体層4に複数個のトランジスタセルTが配列されて形成されている。その複数個のトランジスタセルTより外周側(チップ端部側)の絶縁膜6上にポリシリコン膜によるリング状のp形層1bとn形層1aとが交互に設けられることにより、保護ダイオード1が形成されている。保護ダイオード1は、その一番外側の層にAlなどの金属膜がリング状に接続され、そのング状に設けられている金属膜はソース配線3と金属膜14によりコンタクトされ、一番内側の層にリング状に接続された金属膜がゲート配線2と接続されると共にトランジスタセルTの外周側の一部セルのゲートと接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

121 - 140 / 1,325

[ Back to top ]