Fターム[5F048BC03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 非対称構造 (1,107)

Fターム[5F048BC03]に分類される特許

61 - 80 / 1,107

半導体装置及びその製造方法

【課題】 シリコンビームを使用しかつダブルゲートを有する半導体装置のおけるプロセスばらつきによる抵抗値ばらつきを防止する。

【解決手段】 端部に凹部を有する基板1と、基板1の凹部に一部が埋め込まれた一対のゲート電極4と、基板1の表面であって一対のゲート電極4の間に形成された拡散層7を有し、ゲート電極4と拡散層7の間の電位を変化させることにより、拡散層7の抵抗値を変化させる。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

ブートストラップ回路、インバータ回路、走査回路、表示装置、及び、電子機器

【課題】ブートストラップゲインの上昇を可能にしたブートストラップ回路、当該ブートストラップ回路を用いたインバータ回路、当該インバータ回路を用いた走査回路、当該走査回路を用いた表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】トランジスタと、当該トランジスタの一方のゲート電極とソース/ドレイン領域との間に接続された容量とを有し、当該一方のソース/ドレイン領域の電位の変動に応じてゲート電極の電位が変動するブートストラップ動作を行うブートストラップ回路において、トランジスタについて、ゲート電極の中心を通る線に関してソース領域とドレイン領域とを非対称な構造にする。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

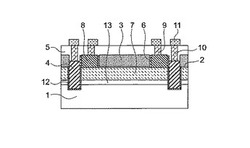

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置およびその製造方法

【課題】高速・低損失であり、かつソフトなスイッチング特性を有するブロードバッファ構造の半導体装置を、FZバルクウェハーを用いて安価に、かつ制御性および歩留まりよく作製すること。

【解決手段】N-型第1半導体層となるN-型FZウェハー10中に酸素を導入した後、FZウェハー10の表面にP型第2半導体層2およびアノード電極4を形成する。アノード電極4の側からFZウェハー10にプロトンを照射して、FZウェハー10中に結晶欠陥12を導入する。熱処理を行って、FZウェハー10中の結晶欠陥12を回復させることにより、第1半導体層内の一部のネットドーピング濃度をFZウェハー10の当初のネットドーピング濃度よりも高くし、所望のブロードバッファ構造を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

半導体装置及び半導体素子

【課題】本発明は、スイッチング損失を低減できる半導体装置及び半導体素子を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、第1ゲートを有し該第1ゲートからの信号でオンオフが制御される第1素子部と、第2ゲートを有し該第2ゲートからの信号でオンオフが制御される第2素子部と、を有する半導体素子と、該第1ゲート及び該第2ゲートに接続され、該半導体素子をターンオンするときは該第1素子部と該第2素子部を同時にターンオンし、該半導体素子をターンオフするときは該第2素子部を該第1素子部よりも遅延してターンオフするように該第1ゲートと該第2ゲートに信号を伝送する信号伝送手段と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出

来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有

する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われ

る回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる

電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置と

する。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低減し、かつ高耐圧で駆動することが可能な半導体装置を提供する。

【解決手段】当該高耐圧トランジスタは、第1の不純物層PEPと、第1の不純物層PEPの内部に形成される第2の不純物層HVNWと、第2の不純物層HVNWを挟むように、第1の不純物層PEPの内部に形成される1対の第3の不純物層OFBおよび第4の不純物層PWと、第3の不純物層OFBから、第2の不純物層HVNWの配置される方向へ、主表面に沿って突出するように、第1の不純物層PEPの最上面から第1の不純物層PEPの内部に形成される第5の不純物層OFB2と、第2の不純物層HVNWの最上面の上方に形成される導電層GEとを備える。第4の不純物層PWにおける不純物濃度は、第3および第5の不純物層OFB,OFB2における不純物濃度よりも高く、第5の不純物層OFB2における不純物濃度は、第3の不純物層OFBにおける不純物濃度よりも高い。

(もっと読む)

III−V族トランジスタとIV族横型トランジスタを含む積層複合デバイス

【課題】内部に横型トランジスタが形成されたシリコン又はIV族アクティブダイの上面に、III−V族アクティブダイが積層された積層複合デバイスを製作する。

【解決手段】積層複合デバイスはIV族横型トランジスタ120と、IV族横型トランジスタの上に積層されたIII−V族トランジスタ110とを備える。IV族横型トランジスタのドレインがIII−V族トランジスタのソースと接触され、IV族横型トランジスタのソースがIII−V族トランジスタのゲート116に結合されて前記複合デバイスパッケージの上面の複合ソース102を与え、III−V族トランジスタのドレインが複合デバイスパッケージの上面の複合ドレイン104を与える。IV族横型トランジスタのゲート126が積層複合デバイスの上面の複合ゲート106を与え、IV族横型トランジスタの基板が積層複合デバイスの底面にある。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETの素子領域の外側の周辺領域において、ドレイン‐ソース間にpn接合ダイオードを形成し、逆起電力による電流の経路を確保してアバランシェ破壊を防止している。しかし、チップサイズの小型化や素子領域の面積の拡大を目的として周辺領域の面積を縮小した場合、pn接合ダイオードの配置領域が縮小し、電流経路が少なくなるためアバランシェ破壊に弱くなる問題があった。

【解決手段】 ゲート引き出し配線8で区画される周辺ゲート領域25において、p+型不純物領域24とソース電極17を接続する第2コンタクト部10の単位面積当たりの合計面積を、素子領域20のソース領域15とソース電極17とを接続する第1コンタクト部9の単位面積当たりの合計面積より大きくする。周辺領域の面積を縮小した場合であっても逆起電力による電流の経路を確保できアバランシェ耐量の劣化を防げる。

(もっと読む)

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、ノイズの発生が抑制された半導体装置を提供する。

【解決手段】実施形態の半導体装置は、ドレイン層と、ドレイン層の表面から内部にかけてトレンチ状に設けられたドリフト領域と、ドリフト領域の表面から内部にかけてトレンチ状に設けられたベース領域と、ベース領域の表面から内部にかけてトレンチ状に設けられたソース領域と、ドレイン層の裏面に対して略平行な方向に、ソース領域の一部からソース領域の一部に隣接するベース領域を貫通してドリフト領域の一部にまで到達する第1トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、ドレイン層の表面から内部にかけて設けられた少なくとも1つの第2トレンチ内に第1絶縁膜を介して設けられた第1抵抗体層と、ドレイン電極と、ソース電極と、を備える。第1抵抗体層は、ソース電極に電気的に接続されている。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

61 - 80 / 1,107

[ Back to top ]