Fターム[5F048BH05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | PN接合分離 (956) | ガードリング(ガードバンド) (263)

Fターム[5F048BH05]の下位に属するFターム

ガードリングが複数形成されたもの (50)

Fターム[5F048BH05]に分類される特許

21 - 40 / 213

半導体素子

【課題】ゲート閾値の変動を抑制または防止できる半導体素子を提供する。

【解決手段】半導体素子1は、n型エピタキシャル層8と、n型エピタキシャル層8の表層部に形成されたボディ領域12と、ボディ領域12の表層部に形成されたn型ソース領域16と、n型エピタキシャル層8上に形成されたゲート絶縁膜19と、ゲート絶縁膜19上に形成されたゲート電極20およびゲート保護ダイオード30とを含む。ゲート保護ダイオード30は、第1のp型領域31とn型領域32と第2のp型領域33とを含む。第1のp型領域31とn型領域32によって第1のダイオード30Aが構成されている。n型領域32と第2のp型領域33によって第2のダイオード30Bが構成されている。第1のp型領域31はゲート電極20に接続されている。第2のp型領域33はソース電極27を介してソース電極27に接続されている。

(もっと読む)

半導体装置

【課題】電界効果型トランジスタ部のオン抵抗を下げ、かつショットキーバリアダイオード部のリーク電流を抑制する。

【解決手段】半導体装置は、第1の半導体層と、第2の半導体層と、第3の半導体層と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第1のトレンチ内に、第1の絶縁膜を介して設けられた埋め込み電極と、埋め込み電極の上に、第2の絶縁膜を介して設けられた制御電極と、第3の半導体層の表面から、第2の半導体層を貫通し、第1の半導体層に至る第2のトレンチの下端に接続され、第1の半導体層内に選択的に設けられた第4の半導体層と、第1の半導体層に接続された第1の主電極と、第2のトレンチ内に設けられた第2の主電極と、を備える。第2のトレンチの側壁において、第2の主電極と、第1の半導体層と、によるショットキー接合が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

半導体装置およびこれを用いた半導体リレー

【課題】高電圧印加時にリーク電流が流れるのを低減する。

【解決手段】第1導電型のSiC(シリコンカーバイド)基板1表面に形成したエピタキシャル成長層2内に、少なくとも一つのトランジスタセルを備え、このトランジスタセルは、エピタキシャル成長層2内に形成された第2導電型のウェル領域3と、このウェル領域3内に形成された第1導電型の領域からなるソース領域4と、ゲート絶縁膜6を介して形成されたゲート電極7と、前記ソース領域4にコンタクトするように形成されたソース電極5と、SiC基板1の第2の面側に形成されたドレイン電極9とを具備しており、このトランジスタセルのうちの最外セルの外側に、隣接してこのウェル領域を囲み、ゲート電極7およびソース電極5のいずれに対しても絶縁されたp型耐圧保持領域3pを具備している。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

半導体装置

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】半導体チップCP1には、スイッチ用のパワーMOSFETQ1,Q2と、パワーMOSFETQ1の発熱を検知するためのダイオードDD1と、パワーMOSFETQ2の発熱を検知するためのダイオードDD2と、複数のパッド電極PDとが形成されている。パワーMOSFETQ1およびダイオードDD1は、辺SD1側の第1MOSFET領域RG1に配置され、パワーMOSFETQ2およびダイオードDD2は、辺SD2側の第2MOSFET領域RG2に配置されている。ダイオードDD1は辺SD1に沿って配置され、ダイオードDD2は辺SD2に沿って配置され、ダイオードDD1,DD2間にソース用のパッド電極PDS1,PDS2以外の全てのパッド電極PDを辺SD3に沿って配置している。

(もっと読む)

絶縁ゲート型半導体装置

【課題】低オン電圧と低スイッチング損失とを両立することができる絶縁ゲート型半導体装置を提供する。

【解決手段】間引き型のIGBT素子において、ダミーセルのP型のフロート層18にN型のホールストッパー層19を設ける。また、このホールストッパー層19により分割された第1の層18aをエミッタ電極21に接地する。これにより、コレクタ電極24からフロート層18を介してゲート電極17に到達する経路に形成される帰還容量の中に溜まる電荷はほとんど無くなるため、スイッチング損失を低減できる。さらに、P型のフロート層18に設けられたN型のホールストッパー層19が電位の壁となるので、半導体基板10からフロート層18を介してエミッタ電極21にホールが抜けてしまうことを抑制することができる。このため、半導体基板10の抵抗が下がり、IGBT素子のオン電圧を下げることができる。

(もっと読む)

ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置

【課題】ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置を提供する。

【解決手段】本発明による半導体デバイスは、第1導電型の半導体基板と、半導体基板に既定の深さを有して形成された2以上の第2導電型の第1ウェル領域と、第2導電型の第1ウェル領域の内に既定の深さを有して形成された少なくとも一つの第1導電型の第2ウェル領域と、第1ウェル領域の間に位置し、第1ウェル領域と既定の間隔だけ離隔して既定の深さを有して形成された第2導電型のガードリング領域と、を含み、ガードリング領域は、システムグラウンド電圧に連結される。

(もっと読む)

半導体装置

【課題】パワーMOSFETを備える半導体装置のコストの低減を図る。

【解決手段】半導体装置1では、P型の半導体基板2上に、N型の半導体層3が積層されている。そして、半導体装置1は、LDMOS領域5に、ボディ領域8、ドレインバッファ領域9、ソース領域11およびゲート電極14などからなるLDMOSFETを備えている。すなわち、半導体装置1は、LDMOSFETを備えながら、厚膜SOI基板ではなく、N型の半導体層3が直上に設けられたP型の半導体基板2を採用している。そして、フィールド絶縁膜13上に7つのフィールドプレート15が設けられ、そのフィールドプレート15の間隔がボディ領域8側(ソース領域11側)ほど小さくされている。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことを容易に可能にする。

【解決手段】ESD保護素子101の高濃度不純物領域121SH,120DH,122SHを、ゲート電極111G,112Gの下方に形成しない。高濃度不純物領域121SH,120DH,122SHを、半導体基板100の面(xy面)にて、少なくとも低濃度不純物領域121SL,121DL,122DL,122SLを介してゲート電極111G,112Gの側部に位置するように形成する。また、高濃度不純物領域121SH,120DH,122SHを、低濃度不純物領域121SL,121DL,122DL,122SLおよび不純物領域121SM,120DM,122SMよりも深い位置まで形成する。

(もっと読む)

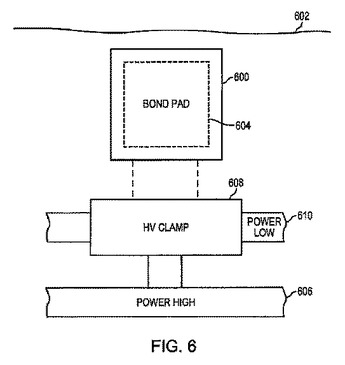

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

(もっと読む)

半導体装置

【課題】 入出力部の電源配線の近傍にバイパスコンデンサを配置する場合、LSIの端子数が多くなると、バイパスコンデンサを配置するための領域を確保することが困難になる。

【解決手段】 半導体基板の表面に、電子回路素子が形成されている電子回路領域が画定される。半導体基板の上に、一方に基準電位が印加され、他方に電源電圧が印加される第1及び第2の配線が配置される。シールリングが、電子回路領域を取り囲むように、半導体基板の上に配置される。シールリングは、第1の配線に電気的に接続される。第1の不純物拡散領域が、シールリングよりも内側において、半導体基板の表層部に形成される。第1の不純物拡散領域の上に誘電体膜が配置される。誘電体膜の上に、シールリングに電気的に接続され、導電材料で形成されたキャパシタ導電膜が配置される。

(もっと読む)

CMOS半導体集積回路

【課題】チップの外周部に出力保護領域を有し、内部回路との間にガードリングによる出力保護パターンが設けられたCMOS半導体集積回路において、周辺部のパターンを改善し、チップサイズを縮小したCMOS集積回路を提供する。

【解決手段】出力保護領域2に接して内部回路領域3が設けられ、出力保護パターンが、出力保護領域2に最も近接したCMOS両半導体型の内部回路領域3の出力保護領域2の近辺に、内部回路領域のトランジスタの基板を形成する半導体と同じ型で且つ濃度の濃く連続して形成されたガードリング用半導体4、5と、ガードリング用半導体上に一定形状のパターンで所定間隔に連続して形成された導体層とのコンタクトパターンと、を有するガードリングで形成されたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズを大きくすることなく、チップ外周のガードリングの、外部応力に対する耐性を強化する。

【解決手段】この半導体装置は、半導体基板と、半導体基板上に形成された集積回路部と、半導体基板上の集積回路部の周辺に存在する絶縁層中に形成された、集積回路部を包囲するガードリング4と、を有する。ガードリング4は、半導体基板に対して垂直な方向に関して重なる位置に配された少なくとも2層の配線層M1,M2,M3と、これらの配線層間を接続するビア9a,9bと、で構成される。ビア9a,9bの形状が、ガードリング4の近傍に位置する一のダイシングライン3から垂直に集積回路部側へ向かう外部応力10を分散させる形状となっている。

(もっと読む)

半導体装置

【課題】半導体装置の高耐圧化を図る。

【解決手段】p-基板200の主面上にはドレイン電極119及びVB電極128が形成されている。p-基板200の主面内には、ドレイン電極119に接続されたn型不純物領域117と、n型不純物領域117とは離間するとともにVB電極128に接続された、n型不純物領域117の側面に対向する側面を有するn型不純物領域121とが形成されている。p-基板200の主面内には、n型不純物領域121の底面に接し、n型不純物領域117の側面に接しない側面を有するn埋め込み層29が形成されている。

(もっと読む)

21 - 40 / 213

[ Back to top ]