Fターム[5F048BH05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | PN接合分離 (956) | ガードリング(ガードバンド) (263)

Fターム[5F048BH05]の下位に属するFターム

ガードリングが複数形成されたもの (50)

Fターム[5F048BH05]に分類される特許

101 - 120 / 213

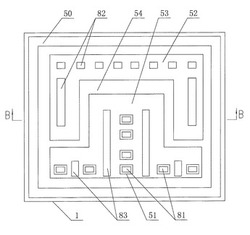

定電流源部品及び製造手段

【課題】直接に交流電源及び直流電源に応用でき、過流過電圧保護機能がある定電流源部品を提供する。

【解決手段】当該部品には、シリコン基板1、于シリコン基板1正面に形成した酸化層、酸化層正面に所在するドレイン金属、ソース金属、グリッド金属、シリコン基板1に植え込んだP+保護リング50、N+ドレイン領域52、N+ソース領域53、N+ソース領域53に所在するP+下敷領域51、N+ドレイン領域52とN+ソース領域53の間を接続するN−通路領域54を有して、ドレイン金属、ソース金属がそれぞれN+ドレイン領域52、N+ソース領域53、P+下敷領域51に接続して、ソース金属、グリッド金属が接続金属で接続する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの所望の特性が出なくなるのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、バイポーラトランジスタ1と、素子分離絶縁膜17および素子分離絶縁膜16と、ベース・コレクタ間分離絶縁膜18とを備えている。また、ベース・コレクタ間分離絶縁膜18と素子分離絶縁膜16との間に埋込コレクタ領域12のリーチスルー領域12aが配置されており、ベース電極20および21は、それぞれ、ベース・コレクタ間分離絶縁膜18および素子分離絶縁膜17に乗り上げるように配置されており、素子分離絶縁膜17のベース電極20が乗り上げている部分およびベース・コレクタ間分離絶縁膜18のベース電極21が乗り上げている部分の厚みは、バイポーラトランジスタ1が形成される領域以外の領域に形成される素子分離絶縁膜16の厚みよりも大きい。

(もっと読む)

SOI(Silicononinsulator)構造の半導体装置およびその製造方法

【課題】効果的にゲッタリングが行えるSOI構造の半導体装置を提供する。

【解決手段】SOI基板100を用いたSOI構造の半導体装置において、活性層3となるシリコン基板に対してArイオンを注入することにより格子歪み層4を形成する。これにより、格子歪み層4をゲッタリングサイトとして機能させることが可能となる。また、Arイオンのドーズ量を調整し、格子歪み層4の引張り応力が11MPa以上かつ27MPa以下となるようにする。これにより、ゲッタリングサイトとして機能させつつ、リーク電流の発生を抑制することが可能となる。

(もっと読む)

半導体装置

【課題】デジタルブロックより発生するノイズから、アナログブロックにおける所定の半導体素子、または、所定の半導体素子群を確実に保護することを目的とする。

【解決手段】本発明に係る半導体装置は、半導体基板21と、半導体基板21上面に領域を区分して配置され、デジタル回路が形成された領域であるデジタルブロック1とアナログ回路が形成された領域であるアナログブロック2とを備える。そして、アナログブロック2における所定の半導体素子群3を平面視で囲んで半導体基板21上に設けられた基板電位固定領域20と、基板電位固定領域20に接続され、外部から所定の電位が付与されるパッドと8を備える。

(もっと読む)

半導体装置

【課題】高耐圧で、かつ、オン抵抗を十分に小さくすることが可能な半導体装置を提供する。

【解決手段】この半導体装置1は、P型の半導体層6と、半導体層6の主表面上の所定領域にゲート絶縁膜4を介して配置されたゲート電極5とを備え、半導体層6は、ゲート電極5の下側を覆うように形成されたN-型ウェル領域11と、N-型ウェル領域11内の主表面側に形成されたP-型ボディ領域12と、P-型ボディ領域12内の主表面側で、かつ、ゲート電極5の一方(矢印A方向)側に形成されたN+型ソース領域13と、N-型ウェル領域11内の主表面側で、かつ、ゲート電極5の他方(矢印B方向)側に形成されたN+型ドレイン領域15と、P-型ボディ領域12の真下でない位置で、かつ、少なくともN+型ドレイン領域15の真下の位置に形成され、N+型ドレイン領域15に接続されたN+型埋め込み領域16とを含む。

(もっと読む)

半導体装置

【課題】ブリッジ回路のMOSFETを1つのチップに形成した場合に、寄生トランジスタによる寄生効果で素子が破壊されることを防ぐ。

【解決手段】nオフセット領域6にアノード電極15を設けてショットキー接合16を形成する。順方向バイアスされる可能性のあるPN接合に並列に多数キャリアデバイスであるショットキーバリアダイオードを接続することで、PN接合が順バイアスされ少数キャリアが発生しないようにし、寄生効果を抑制する。

(もっと読む)

半導体装置

【課題】電源保護回路と入出力回路とが隣接あるいは近接して配置されても、ラッチアップ耐性低下を抑制することのできる半導体装置を提供する。

【解決手段】入出力回路2のN+拡散層221およびP+拡散層222の配置に対して、電源保護回路1のサイリスタ11を形成するP+拡散層211、N+拡散層212、P+拡散層213、N+拡散層214は、N+拡散層221、P+拡散層222の並びに合わせた同じ並びに、一列に配置され、VSSに接続されてサイリスタ11のカソードとなるN+拡散層312が、入出力回路2内でI/Oに接続されるP+拡散層321から遠い位置に配置され、VDDに接続されてサイリスタ11のアノードとなるP+拡散層313が、入出力回路2内でVDDに接続されるN+拡散層322から近い位置に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部の製造工程が増加するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この発明の半導体装置100の製造方法は、半導体基板11を準備する工程と、互いに隣接する素子領域間に素子分離絶縁膜12を形成する工程と、半導体基板11の電界効果型トランジスタ2が形成される領域Bと、互いに隣接する素子領域間に配置される素子分離領域Cとに不純物を導入することにより、電界効果型トランジスタ2が形成される領域Bを覆うpウェル22と、素子分離領域Cの素子分離絶縁膜12の下面に接触するように配置されるpウェル28とを同時に形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の保護ダイオードは、降伏特性が急峻でなく、定電圧ダイオードとしての良質な特性が得られない問題があった。また、保護ダイオードは大部分がMOSトランジスタと別工程で形成するため、工程数の削減、コストの削減が進まない問題があった。

【解決手段】MOSトランジスタと同一の単結晶基板にp−型不純物領域、n+型不純物領域を環状に設けnpn接合を形成する。npn接合を複数設ける場合は、それぞれ離間して同心円の環状に設ける。降伏特性が急峻となるため、良好な定電圧ダイオード特性を得られる。また、MOSトランジスタの製造プロセスを利用して形成できるので、合理化、コストダウンに寄与する。更に耐圧に応じてnpn接合数を選択することにより、耐圧の制御も容易となる。

(もっと読む)

半導体装置

【課題】十分な放電能力を有するESD保護素子を備えた半導体装置を提供する。

【解決手段】基板130上にESD保護素子100を備えた半導体装置であって、ESD保護素子100は、基板130内に形成されたp型ウェル領域101と、p型ウェル領域101に形成された素子分離領域109と、素子分離領域109で取り囲まれた活性領域140上に形成されたn型ESD保護トランジスタ120と、p型ウェル領域101上に形成され、素子分離領域109を挟んで活性領域140を取り囲むp型ガードリング領域106と、p型ウェル領域101上に形成され、活性領域140とp型ガードリング領域106との間に形成されたn型カソード領域107とを備えている。n型カソード領域107と活性領域140との間には素子分離領域109が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】10V以上のリード破壊耐圧を有する高耐圧回路を備えた半導体装置を実現することのできる技術を提供する。

【解決手段】18V系高耐圧駆動回路1HVの高耐圧用nMIS4のソースを構成するn型半導体領域7およびドレインを構成するn型半導体領域7をそれぞれ囲んで、p型第1ウェル3にn型第2ウェル8を形成し、ソースを構成するn型半導体領域7を囲むn型第2ウェル8とドレインを構成するn型半導体領域7を囲むn型第2ウェル8との間にp型チャネルストッパ層13を形成し、n型第2ウェル8とp型第1ウェル3との界面より深く、p型第1ウェル3と基板2との界面より浅い領域に、p型第1ウェル3またはp型チャネルストッパ層13よりも不純物濃度の高いp型埋め込み層16を形成する。

(もっと読む)

半導体装置

【課題】従来に比して静電破壊に対する耐量(ESD耐量)を向上させた半導体装置を提供することを主たる目的とする。

【解決手段】P型の半導体基板1の表面にN型のエピタキシャル層2が形成され、エピタキシャル層2の表面にはP型のウェル層4が形成されている。ウェル層4の表面の所定領域にはソース層5及びドレイン層6が形成され、チャネル領域上にはゲート電極7が形成されている。ウェル層4の表面には複数のP+型のBG層8が、平面的に見た場合にソース層5で周囲が囲まれるようにして、なおかつゲート電極7が延びる方向に沿って一定間隔をおいて複数形成されている。また、BG層8上にはコンタクトホール14及び配線層18が形成されている。このように、BG層8及びコンタクトホール14は、MOSトランジスタ構造の全面に渡ってバランス良く形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の耐電圧を高めることにより、信頼性の高い半導体装置を提供する。

【解決手段】

シリコン層112中に誘電体分離膜120を閉ループ状に形成することによりシリコン層112中のn−型半導体層領域130を絶縁分離し、その内側に拡散抵抗131を形成する。n−型半導体層領域130の四隅部には誘電体分離膜120に少なくともその一部が接するようにp型不純物拡散領域170が形成される。サージ電圧が印加されたとしても、n−型半導体層領域130とp型不純物拡散領域170とによりpn接合が形成されているため、サージ電圧が欠陥に集中することを防ぎ、誘電体分離膜120の破壊を防止することができる。

(もっと読む)

静電放電の保護効果を有するパネルと電子装置

【課題】 静電放電の保護効果を有するパネルと電子装置を提供する。

【解決手段】 パネル基板、及び前記パネル基板上に堆積された複数のパターン化された導電層を含む静電放電の保護効果を有するパネルであって、前記パネルは、アレイ表示域と駆動回路域を有し、前記パターン化された導電層の中の1つの第1導電層は、前記駆動回路域内に複数のほぼ重複したパターンを有し、前記第1導電層は、その他にダミーバーを有し、前記重複性パターンの端パターンの外端に設置され、且つ前記ダミーバーが前記パネルで電力を供給されて操作した時に、電気的に浮動状態となるように設計されており、絶縁物によって任意の電源と絶縁されるため、前記ダミーバーが前記端パターンを保護し、静電放電のダメージを防ぐことができるパネル。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜をドライエッチングしてコンタクトホールを形成する際に、高耐圧トランジスタのゲート絶縁膜が受けるダメージを低減できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上にHVトランジスタ10のゲート電極13と、LVトランジスタ20のゲート電極23と、ダミーゲート電極53とを同時に形成する工程と、シリコン基板1上に層間絶縁膜30を形成する工程と、層間絶縁膜30を部分的にドライエッチングして、ゲート電極13、23、ダミーゲート電極53上にそれぞれコンタクトホール31、33、34を形成する工程と、を含み、コンタクトホール31、33、34を形成する工程では、コンタクトホール31の底面からゲート電極13の表面が露出すると同時に、又はそれよりも前に、コンタクトホール34の底面からダミーゲート電極53の表面が露出するように層間絶縁膜30をエッチングする。

(もっと読む)

マイクロ電子デバイス構造体およびその形成方法(ガード・リングまたはコンタクトをSOI基板に形成する方法)

【課題】セミコンダクタ・オン・インシュレータ(SOI)基板(120)のバルク半導体領域(116)とコンタクトする導電素子(110、310、410a、410b、510)を形成する方法が提供される。

【解決手段】第1の開口部(228)は、トレンチ分離領域(124)の上を覆う共形層(126)に形成される。トレンチ分離領域(124)は、基板(120)のSOI層(108)と端部を共有してもよい。誘電体層(114)は、共形層(126)およびトレンチ分離領域(124)の上面を覆って付着されるのが望ましい。次に、誘電体層(114)および共形層(126)の第1の開口部(228)を通って延びる第2の開口部(416)を形成することができる。バルク半導体領域(116)の一部および共形層の上面(128、328、414a、414b、514)は、第2の開口部(416)内に露出されるのが望ましい。その後、第2の開口部(416)は、金属または半導体のうちの少なくとも1つで充填されて、バルク半導体領域(116)および共形層(126)の上面(128、328、414a、414b、514)の露出部分とコンタクトする導電素子(110、310、410a、410b、510)を形成することができる。

(もっと読む)

半導体装置

【課題】静電保護回路が内部回路の通常動作を妨げない半導体装置の提供。

【解決手段】静電保護回路は、入出力端子10に接続されたドレイン、接地端子12に接続されソース及びソース・ドレイン間上の酸化膜上に形成され入出力端子10に接続されたメタル電極からなるNW−NWフィールドトランジスタ4と、フィールドトランジスタと並列に接続された静電保護素子6を備え、NW−NWフィールドトランジスタ4は、入出力端子10と接地端子12との間に内部回路2の動作電圧よりも大きい電圧が印加されたときにスナップバックし始め、かつスナップバックした後の動作電圧が内部回路2の動作電圧よりも大きくなるように設定され、静電保護素子6は、入出力端子10と接地端子12との間に内部回路の動作電圧よりは大きくNW−NWフィールドトランジスタがスナップバックし始める電圧よりも小さい電圧が印加されたときに動作するように設定されている。

(もっと読む)

集積回路のためのCDMESD保護

【課題】改良された静電放電(ESD)保護回路、より詳細には、集積回路(IC)の保護回路におけるデバイス帯電モデル(CDM)ストレスの場合に対する改良を提供すること。

【解決手段】本発明は、集積回路(IC)のためのデバイス帯電モデル(CDM)静電放電(ESD)保護回路を提供する。ESD保護回路は、第1の導電タイプの基板と、基板上の第1のウェルに形成され、パッドに結合された第2の導電タイプのMOS構成部分と、第1のウェルと基板を隔離するための第1のウェルと基板との間に形成された第2の導電タイプを有する隔離ウェル/領域と、を含む。加えて、回路は、隔離されたウェル/領域に結合されたESDクランプを含む。通常電力の動作中、ESDクランプは開放されている。CDM ESD事象中、基板およびMOS構成部分内に蓄積されたCDM電荷は、ICへの損傷を防止するためにESDクランプにより取り除かれる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の静電破壊強度、ラッチアップ強度等を向上させる。また、静電破壊強度、ラッチアップ強度等のばらつきを無くして、半導体集積回路として一定の品質を保証する。

【解決手段】静電破壊保護セルEC1において、第1のNPN型バイポーラトランジスタ3及び第2のNPN型バイポーラトランジスタ4(静電破壊保護素子の一例)は、P+型の半導体層からなる分離領域6によって囲まれており、他の素子から電気的に分離されている。この分離領域6の幅WB1は、内部回路50を形成している素子を互いに分離する分離領域7の幅WB2より広く形成されている。これにより、静電破壊強度、ラッチアップ強度等を向上させる効果を得ることができる。そのような効果を十分に発揮させるために、分離領域6の幅WB1は、分離領域7の幅WB2(通常は、その半導体集積回路の最小のデザインルールで設計される)より2倍以上広いことが好ましい。

(もっと読む)

101 - 120 / 213

[ Back to top ]