Fターム[5F058BD05]の内容

絶縁膜の形成 (41,121) | 無機積層絶縁膜の構造、材料 (4,921) | 少なくとも一層が酸化物 (2,674) | 金属酸化物 (877)

Fターム[5F058BD05]に分類される特許

101 - 120 / 877

成膜装置、成膜方法及び記憶媒体

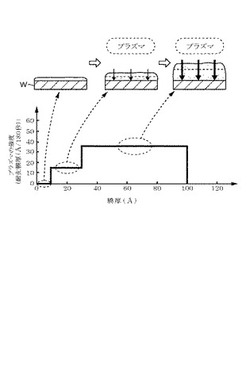

【課題】膜厚方向に亘って緻密な薄膜を得ること。また、良好なデバイス構造を得ること。

【解決手段】回転テーブル2を回転させることにより、Si含有ガスとO3ガスとを用いてウエハWに反応生成物を形成する成膜ステップと、プラズマにより前記反応生成物を改質する改質ステップと、からなる成膜−改質処理を複数回行うと共に、薄膜の形成途中にてプラズマの強度を変更する。具体的には、反応生成物の積層膜厚が薄い時(成膜−改質処理を開始した初期)にはプラズマの強度を小さくすると共に、反応生成物の積層膜厚が増加する程(成膜ステップの回数が増える程)、ウエハWに供給するプラズマの強度を段階的に大きくする。あるいは、反応生成物の膜厚が薄い時にプラズマの強度を強くして、その後弱くする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、ノーマリーオフの特性を有し、かつ電気的特性の変動が小さく、信頼性の高い半導体装置を作製する。

【解決手段】基板に第1の熱処理を行い、次に基板上に下地絶縁層を形成し、次に下地絶縁層上に酸化物半導体層を形成し、第1の熱処理から酸化物半導体層の形成までを大気に暴露せずに行う。次に、酸化物半導体層を成膜した後、第2の熱処理を行う。下地絶縁層には、加熱により酸素を放出する絶縁層を用いる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】メタルゲートを用いたCMISまたはCMOS構造の集積回路デバイスにおいて、Nチャネル領域およびPチャネル領域におけるゲート絶縁膜、メタルゲート層等のつくり分けに関しては、種々の方法が提案されているが、プロセスが複雑になる等の問題があった。

【解決手段】本願発明は、CMOS集積回路デバイスの製造方法において、Nチャネル領域およびPチャネル領域において、ゲート電極膜形成前の高誘電率ゲート絶縁膜の電気的特性を調整するためのチタン系窒化物膜を下方のチタンを比較的多く含む膜と、上方の窒素を比較的多く含む膜を含む構成とするものである。

(もっと読む)

Zr−Ge−Ti−OまたはHf−Ge−Ti−Oの誘電材料を備えた物質とその製造方法

【課題】 フィルム、またはRがZrとHfから選択されたR−Ge−Ti−Oを備えた誘電材料とその製造方法を提供する。

【解決手段】 本発明は、RがZrとHfから選択される、R−Ge−Ti−Oのフィルムを備えた誘電材料に関し、また、その製造方法に関連する。誘電材料は、公式Rx−Gey−Tiz−Owを有することが好ましく、ここで、.05≧x≦1、.05≦y≦1、0.1≧z≦1、1≧w≦2、x+y+z≡1であり、さらに好ましくは、0.15≧x≦0.7、.05≧y≦0.3、0.25≧z≦0.7、1.95≧w≦2.05であり、x+y+z≡1である。本発明は、ダイナミック・ランダム・アクセス・メモリ(DRAM)装置のコンデンサを備えたシリコンチップ集積回路装置での使用に特に有用である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明では、低温での成膜処理により、良質なゲート絶縁膜が得られる半導体装置の製造方法を提供することを課題とする。

【解決手段】本発明では上記課題を解決するため、シリコン基板10上に、600℃以下で原子層堆積法により、ゲート絶縁膜の少なくとも一部となる二酸化シリコン膜31を形成する酸化膜形成工程と、二酸化シリコン膜31の表面に対し、酸化処理を行う表面処理工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体キャパシタ

【課題】 強誘電体膜の上に、SrRuO3膜を形成し、その上に酸化イリジウム等の電極を従来の方法で形成した強誘電体キャパシタでは、目標とする大きさのQswを得ることが困難である。

【解決手段】 基板の上に、下部電極膜を形成する。下部電極膜の上に、強誘電体膜を形成する。強誘電体膜の上に、ペロブスカイト構造を持つ導電性酸化物からなるアモルファスの中間膜を形成する。中間膜の上に、Pt、Pd、Rh、Ir、Ru、Osからなる群より選択された少なくとも1つの金属の酸化物からなる第1の上部電極膜を形成する。第1の上部電極膜を形成した後、酸化性ガスを含む中で第1の熱処理を行うことにより、中間膜を結晶化させる。第1の熱処理の後、第1の上部電極膜の上に、第1の上部電極膜を形成するときの成長温度よりも低温で、Pt、Pd、Rh、Ir、Ru、Osからなる群より選択された少なくとも1つの金属の酸化物からなる第2の上部電極膜を形成する。

(もっと読む)

シリコン表面をパッシベーションする方法

【課題】良好なシリコン表面パッシベーション品質する表面パッシベーション方法を提供する。

【解決手段】シリコン表面をパッシベーションする方法であって、この方法は、(a)シリコン表面を洗浄する工程であって、最終工程が親水性のシリコン表面を得る化学的酸化工程である一連の工程に、シリコン表面を晒す工程を含む工程と、(b)進歩的な乾燥技術を用いて、洗浄したシリコン表面を乾燥させる工程と、(c)シリコン表面上に、ALDAl2O3層のような酸化物層を堆積する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】希土類金属を含有するHigh-k膜のエッチング残渣を抑制するための半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に絶縁膜4を形成する工程と、絶縁膜4の上に希土類元素含有酸化膜7、12を形成する工程と、フッ酸、塩酸、硫酸を含む薬液により希土類元素含有酸化膜7、12をエッチングする工程とを有し、これにより希土類元素含有酸化膜7、12のエッチングを良好に行う。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】金属酸化膜または金属シリケート膜を含む薄膜ゲート絶縁膜を有する半導体装置の製造方法において、VFBを十分に制御し、Vthを十分に制御すること。

【解決手段】基板1上に、第1の金属の酸化膜、または、第1の金属のシリケート膜からなる第1高誘電率ゲート絶縁膜5を形成する第1工程と、第1高誘電率ゲート絶縁膜5上に、第2の金属の酸化膜からなる第2高誘電率ゲート絶縁膜6を形成する第2工程と、第2高誘電率ゲート絶縁膜6上に、ゲート電極膜7を形成する第3工程と、を有し、前記第2工程では、第2の金属元素および炭化水素基からなる主原料と、溶媒材料と、を混合した混合材料を用いて、原子層蒸着法により第2高誘電率ゲート絶縁膜6を形成する半導体装置の製造方法を提供する。

(もっと読む)

多孔性絶縁体及び電界効果トランジスタ

【課題】例えば、チタン酸ストロンチウムを活性層とした電界効果トランジスタのゲート絶縁体としても使用することのできる、新規な絶縁体を提供することを目的とする。

【解決手段】絶縁性を示す材質中に直径5〜100nmである空孔を複数有し、全体の体積に対する前記空孔の占める体積の割合である空孔率が20体積%以上であり、前記空孔には水分が含まれ、前記空孔の体積に対する前記水分の占める体積の割合である水分占有率が23〜100体積%である多孔性絶縁体を使用する。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】良好な電気特性を有する半導体装置を提供することである。

【解決手段】チャネル領域を形成する酸化物半導体層と接するゲート絶縁層に、水素濃度が6×1020atoms/cm3未満であり、且つフッ素濃度が1×1020atoms/cm3以上であるゲート絶縁層を用いることで、ゲート絶縁層から放出される水素量が低減され、酸化物半導体層に水素が拡散することを防ぐことができる。さらに、フッ素により酸化物半導体層内に存在する水素を脱離させ、酸化物半導体層内の水素濃度を低減させることができるため、良好な電気特性を有する半導体装置を提供することできる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタにおける強誘電体層の結晶配向度を向上する半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、下部電極層41上にバッファ層44を形成する工程と、バッファ層44に対して、100体積%の濃度よりも低い酸素濃度の雰囲気下で且つ第1の温度で第1の熱処理を行った後、第1の温度よりも高い第2の温度で第2の熱処理を行う工程と、バッファ層44上に誘電体層42を形成する工程と、誘電体層42上に上部電極層43を形成する工程と、誘電体層42を熱処理して結晶化する工程と、を備える。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が損なわれるのを防止しつつ、電気的特性の良好な半導体装置を提供する。

【解決手段】半導体基板10上に、化学気相堆積法により、シリコンと酸素と炭素とを含む絶縁膜42を形成する工程と、絶縁膜を形成する工程の後、350℃以下の温度で加熱しながら絶縁膜に対して紫外線キュアを行う工程と、紫外線キュアを行う工程の後、絶縁膜に対してヘリウムプラズマ処理を行う工程とを有している。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

有機誘電体を有する有機電界効果トランジスタ

【課題】有機半導体とゲート絶縁体の界面を、材料および製造条件の選択によって改善し、高品質の有機電界効果デバイスを加工する技術を提供する。

【解決手段】溶液から有機半導体層3を堆積させる工程、および、溶液から低誘電率絶縁材料の層2を堆積させて、その低誘電率絶縁材料が上記有機半導体層3と接触するようにゲート絶縁体の少なくとも一部を形成する工程を含み、上記低誘電率絶縁材料は比誘電率が1.1から3.0未満とする。

(もっと読む)

非晶質酸化物薄膜の製造方法及び電界効果型トランジスタの製造方法

【課題】熱処理工程時の温度ムラによる特性のバラつきを抑制し、かつ、高抵抗率に制御可能とする。

【解決手段】In、Ga及びZnを含有し、In及びGaの合計に対するGaのモル比率が0.50<Ga/(In+Ga)の関係を満たす非晶質酸化物薄膜を基板上に成膜する成膜工程と、非晶質酸化物薄膜のGaのモル比率が0.50<Ga/(In+Ga)<0.75の関係を満たす場合には、成膜工程後に100℃以上150℃以下又は350℃以上600℃以下の温度で非晶質酸化物薄膜を熱処理し、非晶質酸化物薄膜のGaのモル比率が0.75≦Ga/(In+Ga)の関係を満たす場合には、成膜工程後に100℃以上200℃以下又は350℃以上600℃以下の温度で非晶質酸化物薄膜を熱処理する熱処理工程と、を有する。

(もっと読む)

101 - 120 / 877

[ Back to top ]