Fターム[5F058BF02]の内容

Fターム[5F058BF02]の下位に属するFターム

Fターム[5F058BF02]に分類される特許

201 - 220 / 519

半導体デバイスおよびその製造方法

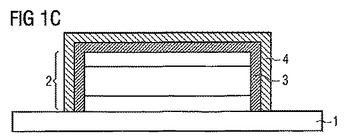

【課題】異なる誘電体材料を含む、デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】第1領域Iと第2領域IIとを有する基板5を用意し、(i)第1領域Iと第2領域IIを覆うようにホスト誘電体層1を形成し、(ii)第1領域Iと第2領域IIの上のホスト誘電体層1を覆うように第1誘電体キャップ層2を形成した後、(iii)第1領域Iの上の下位層1に対して選択的に、第1誘電体キャップ層1を除去して、第1領域Iの上の下位層1を露出させ、(iv)第1領域Iの上の下位層1と、第2領域IIの上の第1誘電体キャップ層2とを覆うようにHfベースの誘電体キャップ層3を形成し、(v)第1領域Iと第2領域IIの上のHfベースの誘電体キャップ層3を覆うように制御電極4を形成する。

(もっと読む)

ALD技術を用いたドーピング

【課題】阻害反応物を用いてドーパント前駆体が利用可能な結合部位の一部を阻害することによって、堆積したドーパントの濃度および均一性を制御することができる。ALDプロセスにおいて、阻害反応物をドーパント前駆体の導入前に導入することができる、または阻害反応物およびドーパント前駆体を同時に導入することができる。

【解決手段】原子層堆積プロセス(ALD)によって、基板表面または2つの薄膜間の界面をドープする方法が提供される。

(もっと読む)

成膜方法および成膜装置

【課題】200℃以下の温度で、ALD法を適用して基板上に膜を形成する場合であっても、基板上に良質な膜を生成することができる成膜方法および成膜装置を提供する。

【解決手段】200℃以下の温度で、原子層成長方法により、基板表面に原料ガスと酸化ガスとを交互に供給して、基板上に原子層単位で酸化膜を形成する工程を所定回数行って所定厚さの膜を形成し、原子層成長法による成膜工程が完了した後、酸化ガスないし不活性ガスを用いてプラズマを発生し、発生されたプラズマを基板上に形成された膜の表面に照射してプラズマ処理する。

(もっと読む)

絶縁膜

【課題】本発明は、絶縁膜、さらに詳しくは、半導体素子デバイスなどにおける層間絶縁膜として使用するのに適した、適当な均一な厚さを有する膜が形成可能な、しかも誘電率、ヤング率などの膜特性に優れた絶縁膜を提供することを目的とする。

【解決手段】シロキサン構造を有する化合物を含む膜に周波数5.8GHzのマイクロウエーブを照射して形成される絶縁膜。

(もっと読む)

半導体装置の製造方法

【課題】配線抵抗のばらつきが低減されて、電気的特性の向上が図られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1の主表面上にLow−k膜3および保護膜5が形成される。配線パターンが相対的に疎な第1領域と密な第2領域のうち、第1領域に位置する保護膜5の部分の厚みが第2領域に位置する部分の厚みよりも薄くされる。保護膜5およびLow−k膜3に所定の深さの溝部が形成される。その溝部を充填するように、保護膜5の表面上に銅膜が形成される。銅膜に研磨処理を施すことにより、溝部内に位置する銅膜の部分を残して保護膜5の表面上に位置する銅膜の部分が除去される。

(もっと読む)

半導体装置の製造方法

【目的】パターン密度の違いによるエッチング差を抑制する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上にポロジェン材料を含む絶縁膜を形成する工程(S104)と、前記絶縁膜に含まれる前記ポロジェン材料の一部を除去する工程(S106)と、前記ポロジェン材料の一部が除去された前記絶縁膜に前記絶縁膜の底部を残すように開口部を形成する工程(S112)と、前記絶縁膜に含まれる前記ポロジェン材料の残部を除去する工程(S114)と、前記開口部の前記底部をエッチングする工程(S116)と、を備えたことを特徴とする。

(もっと読む)

フォトレジスト又はドライエッチングを必要としないパターン化ハードマスク薄膜(RFP)形成のプロセスシーケンス

本発明の一実施形態によれば、紫外線を用いてハードマスク薄膜をパターニングする方法及びシステムが開示される。本発明の実施形態は、ハードマスクパターンを作るためのフォトレジストの被着及びエッチングの加工上の問題を軽減する。最初に、酸化ケイ素などのハードマスク層を被着チャンバ内で基板上に被着させる。場合により、被着に続いてハードマスク層をベーク又はアニールする。その後、ハードマスク層の一部を紫外線で露光する。紫外線はハードマスク材料の露光部分及び未露光部分のパターンを作る。露光に続いて、ハードマスクの未露光部分を除去するウェットエッチングなどのエッチングプロセスが行われてもよい。エッチングに続いて、ハードマスクをアニールするか、ベークするか、又はプラズマ処理してもよい。  (もっと読む)

(もっと読む)

絶縁膜の形成方法、コンピュータ読み取り可能な記憶媒体および処理システム

【課題】 CVD法によって絶縁膜を形成する場合に、シリコンと絶縁膜との界面の形状を極めて平坦化することが可能な絶縁膜の形成方法を提供する。

【解決手段】 複数の孔を有する平面アンテナ31によりチャンバ1内にマイクロ波を導入するプラズマ処理装置100を用い、シリコン表面を酸化して酸化珪素膜を形成する(ステップS1)。この酸化珪素膜上にCVD法により絶縁膜としての酸化珪素膜を成膜し(ステップS4)、さらに、プラズマ処理装置100を用い、チャンバ1内に希ガスと酸素を含む処理ガスを導入するとともに平面アンテナ31によりマイクロ波を導入し、6.7Pa以上267Pa以下の範囲内の圧力条件でプラズマを発生させ、該プラズマにより、絶縁膜を改質する(ステップS6)。

(もっと読む)

半導体デバイスとゲート誘電体組み合わせ層の形成方法

【課題】キャパシタンスを増加させながらリーク電流を減らす半導体デバイスを提供する。

【解決手段】 本発明の半導体デバイスは、(A)導電層と、(B)シリコン製基板と、(C)前記導電層とシリコン製基板との間に形成されてた誘電体層とを有し、前記誘電体層(C)は、(C1)誘電率が3.9以上12以下である酸化シリコン(SiOx≦2 )製の層と、(C2)前記酸化シリコン製の層の上に配置された充填誘電体層とを含むことを特徴とする。

(もっと読む)

電子構成素子を作製する方法および電子構成素子

構成素子をカプセリングするバリア層を有する電子構成素子を作製する本発明の方法には殊に以下のステップが含まれる。すなわち、− 少なくとも1つの機能層(22)を有する基板(1)を準備するステップと、− プラズマ支援原子堆積法(PEALD)を用いて上記の機能層(22)に少なくとも1つの第1バリア層(3)を被着するステップと、− プラズマ支援化学気相成長(PECVD)を用いて前記の機能層(22)に少なくとも1つの第2バリア層(4)を被着するステップとを有する。  (もっと読む)

(もっと読む)

不揮発性半導体メモリ装置

【課題】フローティングゲート電極とコントロールゲート電極を積層したスタックゲート構成において、トンネル絶縁膜と電極間絶縁膜を改良した不揮発性半導体メモリ装置を提供する。

【解決手段】第1導電型の半導体基板10の主面上にトンネル絶縁膜11を介して選択的に形成されたフローティングゲート電極12と、フローティングゲート電極12上に電極間絶縁膜13を介して形成されたコントロールゲート電極14と、各ゲート電極12,14に対応して基板10の主面に形成された第2導電型のソース・ドレイン領域15とを備えた不揮発性半導体メモリであって、トンネル絶縁膜11は、少なくとも2種の金属元素(Al,Hf)と酸素(O)を含む高誘電体膜であり、膜の厚さ方向に対して金属元素の組成が連続的に変化し、かつ対称的な分布を有する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの性能向上を図ってスペーサを形成できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲートを覆って、半導体基板上に、高誘電体材料を含むバリア絶縁膜を形成する工程と、バリア絶縁膜上に、スペーサ絶縁膜を形成する工程と、スペーサ絶縁膜を、異方性エッチングして、ゲートの側壁上にスペーサを残して除去する工程と、露出したバリア絶縁膜を除去する工程と、ゲート及びスペーサをマスクとして、半導体基板に不純物を注入し、エクステンションを形成する工程と、さらにサイドウォールを形成し、ゲート、スペーサ、及びサイドウォールをマスクとして、ソース/ドレイン領域を形成する工程とを有する。

(もっと読む)

アモルファスカーボン膜の処理方法およびそれを用いた半導体装置の製造方法

【課題】エッチング加工後のアモルファスカーボン膜をウエット洗浄した際の酸化による劣化を抑制することができるアモルファスカーボン膜の処理方法を提供すること。

【解決手段】基板上に成膜され、ドライエッチング後にウエット洗浄処理が施されたアモルファスカーボン膜の処理方法であって、ウエット洗浄処理後、上層の形成前に、アモルファスカーボン膜の表面改質処理を行う。

(もっと読む)

三座ベータケトイミネートの金属錯体

【課題】化学蒸着又は原子層蒸着の前駆体として使用される三座β-ケトイミネートの金属錯体の提供。

【解決手段】三座βケトイミネートの金属含有錯体、例えばビス(2,2-ジメチル-5-(1-ジエチルアミノ-2-プロピルイミノ)-3-ヘキサノナト-N,O,N’)ストロンチウム、ビス(2,2-ジメチル-5-(1-メチルエチルアミノ-2-プロピルイミノ)-3-ヘキサノナト-N,O,N’)ニッケル、Ti(O-iPr)3(2,2-ジメチル-5-(1-ジメチルアミノ-2-プロピルイミノ)-3-ヘキサノナト、ビス(4-(1-ジメチルアミノ-2-プロピルイミノ)-2-ペンタノナト)コバルト、トリス(4-(1-ジメチルアミノ-2-プロピルイミノ)-2-ペンタノナト)ランタン、トリス(2,2-ジメチル-5-(1-ジメチルアミノ-2-プロピルイミノ)-3-ヘキサノナト)イットリウムなどの化合物が挙げられる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程中にダメージを受けても、良好な品質を示す低誘電率膜を備えた半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に低誘電率膜14を形成する工程(a)と、低誘電率膜14に凹部20を形成する工程(b)と、工程(b)の後、低誘電率膜14に有機溶液4を塗布する工程(c1)と、シリル化溶液5を用いて低誘電率膜14をシリル化する工程(c2)とを順に行う工程(c)と、工程(c)の後、凹部20に金属を埋め込むことで、低誘電率膜14にビアプラグ及び金属配線のうち少なくとも1つを形成する工程(d)とを備えている。工程(c2)の前に、工程(c1)を行うことで、シリル化溶液5の低誘電率膜14に対する浸透性が向上する。

(もっと読む)

低k誘電体膜用の紫外線硬化法

【課題】熱の費用に悪い影響を与えることなく、機械的特性を向上できる、低k誘電体の形成方法の提供。

【解決手段】基板の表面上に低k誘電体を形成する方法であって、表面上に低k誘電体を成膜し、低k誘電体の機械的特性を効果的に向上させる時間と強さで紫外線に低k誘電体を露光して、これによって、この機械的特性を、紫外線に露光されない低k誘電体の対応する機械的特性や、炉で硬化される低k誘電体の対応する機械的特性や、紫外線の露光の前に過度の活性化エネルギーにさらされる低k誘電体の対応する機械的特性と比べて相当向上させ、この際、過度の活性化エネルギーには、過度のホットプレートベークシーケンス、炉の硬化、焼鈍硬化、複数の温度の硬化プロセス又はプラズマ処理であって、紫外線照射に先立つものが含まれる。

(もっと読む)

多孔性の低kの誘電体を形成するために、紫外線を利用してポロゲンを除去及び/又はキュアするプロセス

【課題】 半導体装置内で使用される多孔性の低kの誘電体を形成すること。

【解決手段】 ポロゲン材料を包含する低kの誘電体フィルムから多孔性の低kの誘電体材料を形成するプロセスが、紫外線照射へ低kの誘電体フィルムを露光することを含んでいる。一実施形態では、該フィルムが、240nm未満の広帯域の紫外線照射へ露光される。他の実施形態では、低kの誘電体フィルムが、フィルムのマトリックスの架橋結合密度を高めるのに効果的な第一の照射パターンへ露光される。このとき同時に、この第一の紫外線照射パターンへの露光の前後で、ポロゲン材料の濃度は、実質的に同一に維持している。低kの誘電体フィルムは、それから、そこで金属の相互接続構造を形成するために処理され、連続して、低kの誘電体フィルムから、ポロゲン材料を除去するのに有効な第二の紫外線照射パターンへ露光され、多孔性の低kの誘電体フィルムを形成する。

(もっと読む)

半導体装置の製造方法

【課題】APM洗浄による側壁絶縁膜のエッチングレートを低減させることができる。

【解決手段】半導体装置の製造方法では、エッチング抑制層107を形成した後に、シリコン基板(半導体基板)104内にn型エクステンション領域(拡散層)112およびp型エクステンション領域(拡散層)115を形成した後、エッチング抑制層107を形成した状態でシリコン基板104の上面を洗浄する。

(もっと読む)

トレンチ内に誘電層を形成する方法

【課題】半導体構造の形成方法、より具体的にはトレンチ内における誘電層の形成方法を提供する。

【解決手段】半導体構造を形成する方法は、基板上にシリコン酸化被膜を形成するために、シリコン前駆体と原子酸素前駆体を約150℃以下の処理温度において反応させることを含む。シリコン酸化被膜は酸素含有環境内で紫外線(UV)硬化される。

(もっと読む)

トランスデューサ用基板の製造方法およびトランスデューサ用基板、並びにトランスデューサ

【課題】ダイヤフラムの寸法精度を高めることが可能なトランスデューサ用基板の製造方法およびトランスデューサ用基板、並びにトランスデューサを提供する。

【解決手段】半導体基板10の一表面側に形成するダイヤフラム20(図1(f))の仮想投影領域を取り囲む不純物ドーピング領域13を半導体基板10の上記一表面側に形成し(図1(b))、半導体基板10の上記一表面側にダイヤフラム20の基礎となる薄膜14を形成した後、半導体基板10の他表面側にダイヤフラム20の平面形状に応じてパターン設計した開孔部15aを有するマスク層15を形成し(図1(d))、その後、マスク層15をエッチングマスクとするとともに薄膜14をエッチングストッパ層として半導体基板10を上記他表面側から薄膜14に達する深さまでエッチングすることにより薄膜14の一部からなるダイヤフラム20を形成する(図1(f))。

(もっと読む)

201 - 220 / 519

[ Back to top ]