Fターム[5F058BF02]の内容

Fターム[5F058BF02]の下位に属するFターム

Fターム[5F058BF02]に分類される特許

121 - 140 / 519

成膜装置、成膜方法及び記憶媒体

【課題】真空容器内にて互いに反応する少なくとも2種類の反応ガスを順番に回転テーブル上の基板の表面に供給しかつこの供給サイクルを実行することにより反応生成物の層を積層して薄膜を形成するにあたり、基板の表面に形成された凹部内に薄膜を良好に埋め込むこと。

【解決手段】ウェハWを載置した回転テーブル2を鉛直軸回りに回転させることによって、ウェハWの表面に第1の反応ガスを供給してこの反応ガスを吸着させ、次いでこの第1の反応ガスと反応して流動性を持つ中間生成物を生成する補助ガス及びこの中間生成物と反応して反応生成物を生成する第2のガスをこの順番でウェハWの表面に供給し、その後ウェハWを加熱ランプ210により加熱して反応生成物を緻密化する。

(もっと読む)

酸化ストロンチウムルテニウム界面

酸化ストロンチウムルテニウムは、ルテニウム伝導体と酸化ストロンチウムチタン誘電体との間に有効な界面を提供する。酸化ストロンチウムルテニウムの形成は、酸化ストロンチウムを形成するための原子層堆積の使用と、その後の酸化ストロンチウムルテニウムを形成するための酸化ストロンチウムの焼鈍とを含む。酸化ストロンチウムの第1の原子層堆積は水を酸素源として使用して行われ、続いて、その後の酸化ストロンチウムの原子層堆積がオゾンを酸素源として使用して行われる。 (もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アニール時の酸化剤の拡散によるゲート電極の酸化を抑制する。

【解決手段】半導体基板の活性領域にゲートトレンチを形成する工程と、前記半導体基板の活性領域上及びゲートトレンチ内にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜の前記ゲートトレンチの開口縁近傍における窒素濃度が、前記ゲートトレンチの底部近傍における窒素濃度よりも高濃度となるように、プラズマ窒化処理によって前記ゲート絶縁膜に窒素を導入する窒化工程と、前記ゲートトレンチを埋めて前記ゲート絶縁膜を覆うようにゲート電極層を積層してから、前記ゲート電極層をエッチングによりパターニングしてゲート電極を形成するゲート電極形成工程と、前記ゲート電極層のエッチングによって露出した前記活性領域をアニールするアニール工程と、を具備してなることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

混合金属酸化物

本発明は、混合金属酸化物、SrM1−xTixO3に関し、xは0<x<1でありMはHf又はZrであり、例えばストロンチウム−ハフニウム−チタニウム酸化物、ストロンチウムジルコニウム−チタニウム酸化物である。また本発明は、前記混合金属酸化物を含む機能装置に関する。 (もっと読む)

窒化物半導体レーザの製造方法

【課題】本発明は、共振器端面にダメージを与えずに表面のクリーニングを行い、瞬時光学損傷への耐性が維持された信頼性の高い窒化物半導体レーザを得ることを目的とする。

【解決手段】この発明にかかる窒化物半導体レーザの製造方法は、窒化物半導体層を有する窒化物半導体レーザ200の製造方法であって、(a)前記窒化物半導体層に、光出射側共振器端面20,光反射側共振器端面21を形成する工程と、(b)窒素を含むガスを熱分解してラジカル化した雰囲気に、前記光出射側共振器端面20,光反射側共振器端面21を暴露する工程とを備える。

(もっと読む)

High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体

【課題】High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体を提供する。

【解決手段】デバイスを形成する方法は、基板を用意するステップと、基板上に界面層を形成するステップと、界面層上にHigh−k誘電体層を堆積するステップと、High−k誘電体層上に酸素除去層を堆積するステップと、アニールを実施するステップとを含む。High−k金属ゲート・トランジスタは、基板と、基板上の界面層と、界面層上のHigh−k誘電体層と、High−k誘電体層上の酸素除去層とを含む。

(もっと読む)

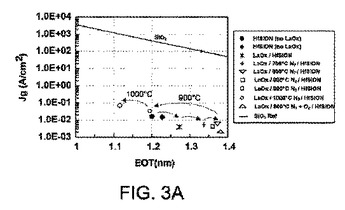

低減された等価酸化膜厚を有する高誘電率ゲートスタックの形成方法

低減された均等酸化物厚さ(EOT)を持つhigh−kゲートスタックを形成する方法を提供し、該方法は:シリコン含有基板を準備し;前記シリコン含有基板上に境界層を形成し、前記境界層が第一の等価酸化物厚さを有し;前記境界層上に第一のhigh−k膜を堆積し;前記第一のhigh−k膜及び前記境界層を、前記第一の等価酸化物厚さと等しいかそれより小さい第二の等価酸化物厚さを持つ変性境界層を形成する温度で熱処理し;及び前記変性境界層上に第二のhigh−k膜を堆積する方法である。ひとつの実施態様によると、前記第一のhigh−k膜がランタン酸化物を含み、前記第二のhigh−k膜がハフニウムシリケートを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 CVD−MnOxをバリア膜に用いても歩留りの低下を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】 N層以上の銅、又は銅合金配線4、8を有し、これらN層の銅、又は銅合金配線4、8のバリア膜としてCVD−MnOx膜を使用する半導体装置の製造方法であって、第1層乃至第N−1層のCVD−MnOx膜3は、セルフリミットがかかる前に成膜を完了させ、第N層のCVD−MnOx膜7は、セルフリミットがかかるように成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体界面のダングリングボンドを終端させて、リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】ボンディングパッド40が設けられる最上層の配線層39の上に、フッ素を含んだ介在層41としてCVD法によりよって形成されたフッ素含有酸化シリコン膜(SiOF)を設ける。この上にパッシベーション膜42としてプラズマCVD法により形成した窒化シリコン膜を設け、フッ素に対するバリアとする。この後熱処理を行い、フッ素をシリコン基板の表面に拡散させる。

(もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の高集積化と供に、メモリ装置のキパシタで容量値の確保のために、酸素欠損のない高誘電率膜を形成する装置の製造方法を提供する。

【解決手段】誘電体膜を形成する工程と、酸化性ガスを供給して誘電体膜に対して酸化処理を行う工程を複数回、断続的に繰り返す熱処理工程と、を有する誘電体膜を備えた半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】配線材料の拡散を抑えながら、金属配線の微細化を図ることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に層間絶縁膜を形成する工程(a)と、層間絶縁膜に配線を形成する工程(b)と、配線の上面及び層間絶縁膜の上面に有機溶液を塗布する工程(c)と、工程(c)の後に、配線の上面及び層間絶縁膜の上面にシリル化溶液を塗布する工程(d)と、工程(d)の後に、基板を加熱する工程(e)と、少なくとも配線の上面上に第1のライナー絶縁膜を形成する工程(f)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の侵食を抑制し、FETの故障や不良の発生を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】基板10上にGaN系半導体層15を形成する工程と、GaN系半導体層15上に酸化アルミニウムからなるゲート絶縁膜18を450℃以下の成膜温度で形成する工程と、ゲート絶縁膜18の上面に保護膜19を形成する工程、ゲート絶縁膜18を熱処理する工程、及びゲート絶縁膜18をプラズマ処理する工程のいずれか一つと、前記いずれか一つの工程の後に、ゲート絶縁膜18を形成する工程の後のアルカリ溶液を用いた処理を実行する工程と、前記ゲート絶縁膜18上にゲート電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 ハフニウムシリケートからなるゲート絶縁膜に、アルミナ膜を重ねると、等価酸化膜厚を薄くすることが困難になる。また、ハフニウムシリケートからなるゲート絶縁膜内にAlが拡散すると、正孔の移動度が低下してしまう。

【解決手段】 半導体基板(10)の上に、HfとOとを含む絶縁膜(16)を形成する。この絶縁膜の上に、構成元素として酸素とチタンとを含むキャップ膜(17)を形成する。絶縁膜及びキャップ膜を、窒素ガスまたは希ガス雰囲気中で熱処理し、キャップ膜中のチタンを絶縁膜内に拡散させることにより、ゲート絶縁膜(18)を形成する。ゲート絶縁膜の上に、ゲート電極膜(19)を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板側から熱酸化膜、CVD酸化膜の2層を積層したゲート絶縁膜を有する半導体装置において、アニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することによる半導体基板等の歪みを低減する。

【解決手段】熱酸化膜とCVD酸化膜との間に、リンガラス膜を形成する。リンガラスは、シリコン酸化膜中にリン(P)を導入して軟化温度(ガラス転移温度)を低くした酸化膜であり、850〜900℃でリフローと呼ばれる流動現象が生じる。900℃以上で行われるCVD酸化膜のアニール処理時には、リンガラス膜がリフロー流動状態となり、熱酸化膜とCVD酸化膜と間で緩衝材として機能する。これによってアニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することが抑制され、ゲート絶縁膜や半導体基板の歪みが低減される。

(もっと読む)

半導体装置

【課題】半導体装置の特性の安定化を図ることができるとともに、半導体装置の耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置2の活性領域Aでは、半導体層4の上側の少なくとも一部に第1絶縁層18が形成されている。第1絶縁層18は、半導体層4が有するダングリングボンドを終端させる終端材料を含んでいる。耐圧領域Bでは、半導体層4の上側に第1絶縁層と異なる材料からなる第2絶縁層20が形成されており、第1絶縁層18は形成されていない。そして、第2絶縁層20が第1絶縁層18より絶縁度が高くされている。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】 本発明の目的は、膜中の炭素、水素、窒素、塩素等の不純物濃度が極めて低い絶縁膜を低温で形成することができる半導体装置の製造方法および基板処理装置を提供することにある。

【解決手段】 基板を収容した処理容器内に所定元素を含む原料ガスを供給することで、基板上に所定元素含有層を形成する工程と、大気圧未満の圧力に設定した処理容器内に酸素含有ガスと水素含有ガスとを供給することで、所定元素含有層を酸化層に改質する工程と、を交互に繰り返すことで、基板上に所定膜厚の酸化膜を形成する工程を有し、酸素含有ガスが酸素ガスまたはオゾンガスであり、水素含有ガスが水素ガスまたは重水素ガスであり、酸化膜を形成する工程では、基板の温度を400℃以上700℃以下とする。

(もっと読む)

基板処理装置、バルブの制御方法及びそのプログラム

【課題】人手を介さずにバルブ制御装置にバルブ開閉パターンを書き込むことができ、バルブの高速な切り替え動作をロギングできる基板処理装置を提供する。

【解決手段】基板処理装置は、複数のバルブの開閉動作を制御するバルブ制御装置300と、前記複数のバルブの開閉状態の設定を行うバルブ切り替えパターンを作成するパターン作成装置302と、を有する。前記パターン作成装置は、作成したバルブ切り替えパターンを前記バルブ制御装置の内部エリアに書き込むと共に、前記パターン作成装置の記憶媒体に保管する。前記バルブ制御装置は、内部エリアに書き込まれたバルブ切り替えパターン306に基づいて複数のバルブの切り替えを行い、その時の前記複数のバルブの開閉状態を前記バルブ制御装置の内部エリアに書き込むと共に、前記パターン作成装置の記憶媒体に保管する。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の仕事関数を得ると共にトランジスタの駆動力を劣化させない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1の上に形成された界面層5と、界面層5の上に形成された高誘電率ゲート絶縁膜6と、高誘電率ゲート絶縁膜6上に形成されたゲート電極とを備える。高誘電率ゲート絶縁膜6はランタンを含有し、高誘電率ゲート絶縁膜6におけるゲート電極との界面に含まれているランタンの濃度は、高誘電率ゲート絶縁膜における界面層との界面に含まれているランタンの濃度よりも大きい。

(もっと読む)

CVD炭窒化ケイ素膜用前駆体

【課題】炭窒化ケイ素膜形成用前駆体の化学気相成長により基材上に膜を形成するための方法を提供する。

【解決手段】

式中、Rが、直鎖、分枝若しくは環状の飽和若しくは不飽和のC1〜C10アルキル基、芳香族、複素環、又は式Cのシリルから選択され、R1が、直鎖、分枝又は環状の飽和又は不飽和のC2〜C10アルキル基、芳香族、複素環、水素、シリル基から選択され、置換基を選択的に有無し、式A中のRとR1を結合して環状基(CH2)n(式中、nは1〜6)にしてもよく、R2が、単結合、(CH2)n鎖、環、SiR2又はSiH2を表すアミノシランからなる前駆体及び混合物を用いる。

(もっと読む)

121 - 140 / 519

[ Back to top ]