Fターム[5F058BF02]の内容

Fターム[5F058BF02]の下位に属するFターム

Fターム[5F058BF02]に分類される特許

41 - 60 / 519

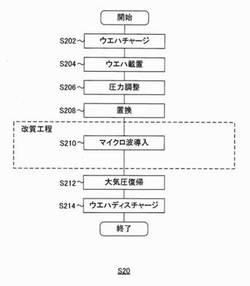

半導体装置の製造方法および基板処理装置

【課題】高誘電率を有する薄膜を改質する半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】高誘電体膜が形成された基板を処理室へ搬入する工程と、基板にマイクロ波を照射することにより、高誘電体膜を加熱して改質する工程と、基板を前記処理室から搬出する工程と、を有する半導体装置の製造方法が提供される。

(もっと読む)

シリコン酸化膜の成膜方法、及びシリコンエピタキシャルウエーハの製造方法

【課題】 CVD法によるシリコン酸化膜の成膜方法であって、シリコン酸化膜成膜後に熱処理または塩素処理などの別の改質工程を行わずとも、OH基の含有量が抑えられたシリコン酸化膜を成膜することができるシリコン酸化膜の成膜方法を提供する。

【解決手段】 エピタキシャル成長用のシリコンウエーハに対してCVD法を用いてシリコン酸化膜を成膜する方法であって、少なくとも、前記シリコンウエーハとして表面にエピタキシャル層を成長する前のシリコンウエーハに対して、シリコン原料ガスの他に塩素ガスを含有する反応ガス雰囲気下で、前記CVD法によりシリコン酸化膜を成膜することを特徴とするシリコン酸化膜の成膜方法。

(もっと読む)

製膜方法および半導体装置の製造方法

【課題】半導体基板上にパターニングされたSiO2膜および/もしくはSiN膜を生成する製膜方法において、拡散制御性能、またはパッシベーション性能を満たすSiO2膜および/もしくはSiN膜を生成する。

【解決手段】SiO2および/もしくはSiO2前駆体を含む溶液を半導体基板上にパターニングして塗布して第1パターンを生成するステップと、CVD法によってSiO2膜および/もしくはSiN膜を生成するステップと、フッ酸水溶液に浸漬させて前記第1パターンを除去することにより、前記CVD法によるSiO2膜および/もしくはSiN膜からなる第2パターンを生成するステップと、を備える。

(もっと読む)

酸化プラセオジムを備えた誘電体、酸化プラセオジムを備えたトランジスタ及びその製造方法

【課題】酸化プラセオジムの誘電体、酸化プラセオジムを備えたトランジスタ及びその製造方法を提供し、以って半導体素子のリーク電流及び等価酸化物膜厚の過大の問題を解決すること。

【解決手段】本発明では、酸化プラセオジムを備えたトランジスタは、少なくとも一つのIII−V族基板と、一つのゲート誘電層と、一つのゲート電極とを含む。また、III−V族基板にゲート誘電層が設けられ、ゲート誘電層にゲート電極が設けられ、誘電層は酸化プラセオジム(PrxOy)である。本発明は、誘電層材料として高誘電率及び高エネルギーギャップを備えた酸化プラセオジム(Pr6O11)を用いることにより、リーク電流を有効に抑制する外、更にIII−V族材料を基板とした素子の等価酸化膜厚(EOT)を薄くさせることもできる。

(もっと読む)

炭化珪素半導体素子の製造方法及び電子デバイスの製造方法

【課題】炭化珪素とその上に形成される絶縁膜との界面の品質及び当該絶縁膜の品質を改善して界面準位密度を低減することができる炭化珪素半導体素子の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】炭化珪素基板1の主表面を、水素ガスを含むクリーニングガスで表面処理し、前記主表面を窒素含有ガスで表面処理し、前記主表面上に絶縁膜2を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】生産性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、シリコン基板101と、同一のシリコン基板101上に設けられたN型トランジスタ200およびP型トランジスタ202と、を備え、N型トランジスタ200およびP型トランジスタ202は、Hfを含む高誘電率ゲート絶縁膜108と、高誘電率ゲート絶縁膜108上に設けられたTiN膜110と、を有しており、N型トランジスタ200は、シリコン基板101と高誘電率ゲート絶縁膜108との間に、La添加SiO2膜109aを有しており、P型トランジスタ202は、高誘電率ゲート絶縁膜108とTiN膜110の間に、N型トランジスタ200と同じ仕事関数調整用元素を含有するLa添加SiO2膜109bを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】選択メタルキャップを用いることなしに、生産性の高いエアギャップ配線を形成する。

【解決手段】ウエハ14上の絶縁膜200にCuダマシン配線210を形成する第1の工程と、ウエハ14上に第1のバリア膜220を形成する第2の工程と、後続する接続孔242を開口する工程において、接続孔242の孔底部244に露出するCu配線206と隣接する絶縁膜200、及び最小寸法スペースの3倍以上の幅をもつ幅広スペース200aを保護するように、第1のバリア膜220をパターニングする第3の工程と、第1のバリア膜220をマスクとして絶縁膜200を除去する第4の工程と、ウエハ14上に第2のバリア膜224を形成する第5の工程と、Cu配線206間にエアギャップ232を残しつつ絶縁膜230を形成する第6の工程と、を有する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】メタルゲートを用いたCMISまたはCMOS構造の集積回路デバイスにおいて、Nチャネル領域およびPチャネル領域におけるゲート絶縁膜、メタルゲート層等のつくり分けに関しては、種々の方法が提案されているが、プロセスが複雑になる等の問題があった。

【解決手段】本願発明は、CMOS集積回路デバイスの製造方法において、Nチャネル領域およびPチャネル領域において、ゲート電極膜形成前の高誘電率ゲート絶縁膜の電気的特性を調整するためのチタン系窒化物膜を下方のチタンを比較的多く含む膜と、上方の窒素を比較的多く含む膜を含む構成とするものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明では、低温での成膜処理により、良質なゲート絶縁膜が得られる半導体装置の製造方法を提供することを課題とする。

【解決手段】本発明では上記課題を解決するため、シリコン基板10上に、600℃以下で原子層堆積法により、ゲート絶縁膜の少なくとも一部となる二酸化シリコン膜31を形成する酸化膜形成工程と、二酸化シリコン膜31の表面に対し、酸化処理を行う表面処理工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】保護膜としてSiN膜が使用されている場合であっても、素子動作特性の変動を軽減することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置2は、ドレインドリフト領域12を有する半導体基板11と、ドレインドリフト領域12上に形成されたフィールド酸化膜17と、ゲート電極18と、中間絶縁膜17と、メタル層21,22と、これらを覆うSiN膜23と、SiN膜23上にO3−TEOSを用いたCVD法により形成され、カーボンを含有するPSG膜24とを有する。

(もっと読む)

シリコン表面をパッシベーションする方法

【課題】良好なシリコン表面パッシベーション品質する表面パッシベーション方法を提供する。

【解決手段】シリコン表面をパッシベーションする方法であって、この方法は、(a)シリコン表面を洗浄する工程であって、最終工程が親水性のシリコン表面を得る化学的酸化工程である一連の工程に、シリコン表面を晒す工程を含む工程と、(b)進歩的な乾燥技術を用いて、洗浄したシリコン表面を乾燥させる工程と、(c)シリコン表面上に、ALDAl2O3層のような酸化物層を堆積する工程とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

シリコン酸化膜からのOH基除去法

【課題】OH基を含有するシリコン酸化膜から、TFTの性能である界面特性や絶縁性のため、及び基板を安価なものにするため低温で作製するため、低温で簡便な方法でOH基を減少させる方法を提供する。

【解決手段】基板上に低温形成された、OH基を含有するシリコン酸化膜を有機溶媒に接触・浸漬させる工程と、その後、前記シリコン酸化膜を低温加熱する熱アニール処理を加える工程と、を有することを特徴とするシリコン酸化膜からのOH基除去法。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置の製造方法、半導体装置およびカメラモジュール

【課題】研磨により露出した基板端部からの汚染を低減することができる半導体装置の製造方法を得ること。

【解決手段】半導体基板1の周縁部を研削する研削工程と、研削工程により露出した表面8を含む前記半導体基板1の表面に、絶縁膜6である保護膜9を形成する保護膜形成工程と、を含む。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Ga2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

非晶質酸化物薄膜の製造方法及び電界効果型トランジスタの製造方法

【課題】熱処理工程時の温度ムラによる特性のバラつきを抑制し、かつ、高抵抗率に制御可能とする。

【解決手段】In、Ga及びZnを含有し、In及びGaの合計に対するGaのモル比率が0.50<Ga/(In+Ga)の関係を満たす非晶質酸化物薄膜を基板上に成膜する成膜工程と、非晶質酸化物薄膜のGaのモル比率が0.50<Ga/(In+Ga)<0.75の関係を満たす場合には、成膜工程後に100℃以上150℃以下又は350℃以上600℃以下の温度で非晶質酸化物薄膜を熱処理し、非晶質酸化物薄膜のGaのモル比率が0.75≦Ga/(In+Ga)の関係を満たす場合には、成膜工程後に100℃以上200℃以下又は350℃以上600℃以下の温度で非晶質酸化物薄膜を熱処理する熱処理工程と、を有する。

(もっと読む)

間隙率を求める装置及び方法

【課題】所定の圧力及び所定の温度に加圧された部屋に配置した基板に形成されている物質(特に、薄膜)の間隙率を求める装置及び非破壊方法に関する。

【解決手段】ガス物質(例えば、トルエン蒸気)が部屋1に導入され、所定時間後、部屋に配置した基板2に形成されている薄膜の間隙率が、少なくとも偏光解析測定によって求められる。特に、偏光解析器6から得られる光学的特性は、薄膜の間隙(ポア)に凝縮されたガス物質の量を求めるために利用される。その量は、薄膜の間隙率を計算するために利用される。

(もっと読む)

41 - 60 / 519

[ Back to top ]