Fターム[5F064EE22]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699)

Fターム[5F064EE22]の下位に属するFターム

Fターム[5F064EE22]に分類される特許

41 - 60 / 566

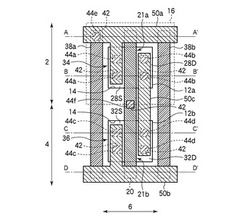

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体集積回路のタイミング解析システム、タイミング解析方法及びプログラム

【課題】統計的STAの実行時間を短縮できるタイミング解析システムを提供する。

【解決手段】本発明のタイミング解析システムは、ばらつき要素をばらつき要素マージ部に入力するばらつき要素入力部と、2種類のばらつき要素のばらつきを、1種類のばらつき要素のばらつきにマージするばらつき要素マージ部と、マージしたばらつき要素を使用して統計的STAを実行する統計的STA実行部とを備える。

(もっと読む)

レイアウト設計装置、レイアウト設計方法およびプログラム

【課題】配線およびダミーパターンが配置された領域の割合を各メタル層において均一に保ちつつ、ダミーパターンの生成によって生じたタイミングエラーを解消できるようにすること。

【解決手段】レイアウト設計装置は、配線およびダミーメタルが配置されたメタル層において、エラーを生じた配線の周囲に配置された複数のダミーメタルの中から該エラーの原因となったダミーメタルを抽出し、該メタル層を分割して得られた複数の領域のそれぞれにおいて、配線およびダミーメタルを含むメタルが占める割合であるメタル密度が該メタル層に対して規定された所定のメタル密度以上となるようにしつつ、該エラーが解消されるように、抽出したダミーメタルの中から削除すべきダミーメタルを選択するダミーメタル選択部と、選択されたダミーメタルを削除するダミーメタル変更部と、を備えている。

(もっと読む)

半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラム

【課題】長さが均一で直線的な配線を配置することができる半導体集積回路のレイアウト設計方法、レイアウト設計装置及びレイアウト設計プログラムを提供すること。

【解決手段】半導体集積回路のレイアウト設計方法は、第1の配線ピッチで配線を行う高速配線処理と、第1の配線ピッチより狭い第2の配線ピッチで配線を行う通常配線処理と、を有する。高速配線処理は、所定の高速バス配線上の複数のネットを第1の配線ピッチで略平行、かつ、略等長となるように自動配線を行う。通常配線処理は、高速配線処理より前に実行されない。

(もっと読む)

マクロ用レイアウト検証装置及び検証方法

【課題】マクロのレイアウト情報に基づいて、当該マクロが使用されるLSIのレイアウト設計時に発生する可能性がある設計規則違反を予め検出する。

【解決手段】マクロ用レイアウト検証装置は、マクロの端子にビアコンタクトを配置したと仮定する手段と、ビアコンタクトとマクロ内レイアウトとの関係が設計規則に違反するか否かを判定する手段と、を具備する。

(もっと読む)

配線削減方法及び回路生成装置

【課題】モジュール間の配線を自動的に削減する。

【解決手段】モジュール11A及び11Bの間に接続された配線に関する情報を含む仮配置/仮配線情報33に基づき、モジュール11A及び11Bの間に接続された配線の本数を抽出し、抽出された配線の本数と、予め設定された、配線の本数に対する閾値を少なくとも含む閾値情報34とを比較し、比較の結果、配線の本数が閾値を超えた場合に、モジュール11A及び11Bのうち、送信側のモジュール11Aに、パラレル信号をシリアル信号に変換するパラレルシリアル変換回路13を挿入するとともに、受信側のモジュール11Bに、シリアル信号をパラレル信号に変換するシリアルパラレル変換回路14を挿入し、モジュール11A及び11Bの間の接続をパラレル接続からシリアル接続に変更する。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

配線配置情報検証方法および配線配置情報検証装置

【課題】半導体集積回路の製造工程等におけるマスクレイアウト等の配線配置情報において、配線のループを効率良く検証する。

【解決手段】マスクレイアウトにおいて、分岐配線毎に矩形状のセグメントに分割し(ステップS01〜S03)、各セグメントの隣接関係の判定条件から配線の端部を特定し(ステップS04〜S05)、配線の末端から縮退加工処理を、末端図形の削除が発生しなくなるまで(ステップS08)、繰り返し行うことで(ステップS06〜S07)、真のループ配線箇所のみ検出し、オリジナルのマスクレイアウト上に強調表示して、配線ループの検証を支援する。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

半導体集積回路

【課題】動作特性を劣化させることなくセル面積の縮小化を図ったマクロセル構造の半導体集積回路を得る。

【解決手段】Pウェル領域1の中央部にNウェル領域2が形成される。Nウェル領域2の平面視上方及び下方にN活性領域4a及び4bが形成される。Pウェル領域1内においてN活性領域4aの平面視上方及び下方にPウェルコンタクト領域5a及び5bが横方向に延びて形成される。Nウェル領域2内において中央にP活性領域3が形成され、P活性領域3の左横に縦方向に延びてNウェルコンタクト領域6が形成される。P活性領域3の中心部を横断するVDD用メタル配線層14の一部であるウェルコンタクト部14cは、Nウェルコンタクト領域6上にも形成され、ウェルコンタクト部14cとNウェルコンタクト領域6とは複数のコンタクトホール21を介して電気的に接続される。

(もっと読む)

配線基板の配線経路決定方法及び半導体装置の配線経路決定方法

【課題】設計時間とコンピュータ資源の消費とを抑えつつ、配線性を向上させることができる配線方法を提供する。

【解決手段】始点から、第1の配線形成用格子を連続的になぞって、複数の第1の交点のうちから選択された1つの第1の選択済交点まで、追加配線を伸ばすステップと、設計済配線及び設計済ビアの位置に基づいて、第1の配線層上に追加ビアを配置することができる第1のビア配置可能領域と、第2の配線層上に追加ビアを配置することができる第2のビア配置可能領域とを算出するステップと、第1の選択済交点を下面の領域内のいずれかの位置に含む追加ビアを、下面が第1のビア配置可能領域に含まれ、且つ、上面が第2のビア配置可能領域に含まれるように配置するステップと、追加ビアから、第2の配線形成用格子を連続的になぞって、終点まで追加配線を伸ばすステップとを有する。

(もっと読む)

電子素子の製造方法および電子素子

【課題】有機絶縁層を有する電子素子の配線短絡を簡素な工程により絶縁することが可能な電子素子の製造方法および電子素子を提供する。

【解決手段】配線層21,22の上に有機絶縁層12を形成したのち、配線層21,22の短絡部23に、有機絶縁層12に対して透過性を持つ波長のレーザ光LBを有機絶縁層12を介して照射、または基板11に対して透過性を持つ波長のレーザ光LBを基板11を介して照射する。レーザ照射領域24では短絡部23が消失して、配線層21と配線層22との間の絶縁が回復する。短絡部23の上下に接する有機絶縁層12または基板11は残されている一方、レーザ照射領域24(短絡部23が消失した部分)には空洞25が生じる。

(もっと読む)

半導体装置の設計装置、半導体装置の設計方法、及び半導体装置

【課題】回路の面積の増大や、設計時間の長期化や、大規模な回路の場合における修正の困難性などの問題が発生することなく、EMの発生が著しく抑制された配線を設計する。

【解決手段】半導体装置の設計方法は、互いに平行に配置された複数の配線と複数の配線を互いに接続する複数のビアとを備えるグリッド配線を配置するステップS01と、グリッド配線に接続された複数の内部回路を配置するステップS02と、複数の内部回路によりグリッド配線内に流れる電流の電流密度を計算するステップS03と、電流密度に応じたエレクトロマイグレーションを抑制する配線長となるように、複数の配線の各々を分断するステップS04、S05とを具備する。

(もっと読む)

半導体装置のレイアウト方法及びその半導体装置

【課題】トランジスタのしきい電圧の変化を減らすことにより、半導体装置の信頼性を向上させることができる半導体装置のレイアウト方法及びその半導体装置を提供する。

【解決手段】半導体基板内に形成された少なくとも1つの第1電極と第2電極を有する複数個のトランジスタのアクチブ領域を配置する段階と、前記複数個のトランジスタのアクチブ領域のそれぞれの少なくとも1つの第1電極と第2電極との間に位置し、前記半導体基板上に所定の幅と長さを有する1つ以上の実質的に同一間隔に分離された前記複数個のトランジスタのゲートを配置する段階と、前記複数個のトランジスタの間に、所定の幅と長さを有し、前記半導体基板上に前記複数個のトランジスタの分離されたゲートの間隔と実質的に同一間隔に配置された複数個のダミーゲートを配置する段階とを有する。

(もっと読む)

半導体装置、および、配線設計方法

【課題】チップサイズを縮小し、再配線層の配線を容易にすることが可能な半導体装置を提供する。

【解決手段】略矩形のLSI基板1の上面に、パッド電極4a1、4a2、4c1を被覆する絶縁膜3a、3bが設けられ、前記絶縁膜3b上に、前記パッド電極4a1、4a2、4c1の何れかに接続された第1のコンタクト配線7a1、7a2、7c、および前記第1のコンタクト配線7a1、7a2に接続された再配線8b1、8b2が設けられ、第1の再配線エリア3上に設けられたボール電極2b、2cと、第1のパッド電極4c1が上面の端部に設けられたLSIコア1a3と、前記第1のパッド電極4c1に接続された第2のコンタクト配線9b1に接続された配線層6b1と前記パッド電極4a1、4a2のうちの第2のパッド電極4a1とに接続された第3のコンタクト電極9b2が形成され、前記LSIコア1a3に隣接した第2の再配線エリア1a2、とを有する。

(もっと読む)

41 - 60 / 566

[ Back to top ]