Fターム[5F064EE22]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699)

Fターム[5F064EE22]の下位に属するFターム

Fターム[5F064EE22]に分類される特許

81 - 100 / 566

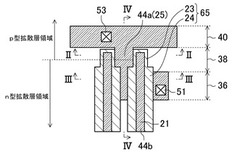

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

半導体集積回路装置およびその製造方法、配線配置装置、配線配置方法、配線配置プログラム、並びに記録媒体

【課題】スタンダードセルを利用して機能回路ブロックをレイアウトする際、供給電源の品質を動作レベルに保ちながら、製造品質を左右する各配線層の占有率のばらつきを少なくする。

【解決手段】スタンダードセル1を、これを構成するセル構成トランジスタを有し、全スタンダードセルに共通接続される電源供給配線及び接地供給配線、および個々のスタンダードセルの機能を実現するための信号配線を含まず、かつ各スタンダードセルの機能を該セル構成トランジスタにより決定する最小限の配置配線、および該セル構成トランジスタの直近に配置され、該スタンダードセルの信号端子を含むよう構成した。

(もっと読む)

半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置

【課題】チップサイズを縮小可能な半導体集積回路のレイアウト設計方法、プログラム、及びレイアウト設計装置を提供すること。

【解決手段】チップ内にY方向メタルデータを持つプリミティブセルが存在するか判定する工程(ステップB1)と、プリミティブセルが上下に隣接しているか判定する工程(ステップB3)と、各プリミティブセル内のY方向メタルデータを有する層が同じか判定する工程(ステップB4)と、各プリミティブセルのうち移動可能なスペースがあるプリミティブセルがあるか判定する工程(ステップB5)と、各判定を満たす場合に、各プリミティブセルの種類が同じか否かを判定する工程(ステップB6)と、各プリミティブセルの種類に応じてプリミティブセルのX座標の配置位置調整を行う工程(ステップB7、8)と、プリミティブセルの位置を固定する工程(ステップB9)と、を含む。

(もっと読む)

半導体装置

【課題】電源配線やグランド配線に流れる電流の周波数が上がってもインピーダンスが上がるのを抑えられる半導体装置を提供すること。

【解決手段】トランジスタ20、21の近傍に配線された電源配線11a及びグランド配線11cを備え、電源配線11a及びグランド配線11cは、それぞれ、分割した構造となっており、所定間隔をおいて一方向に配線された複数本の分割配線11a、11cよりなる。

(もっと読む)

スパイラルコイルの配線構造および集積回路装置

【課題】 第1インダクターおよび第2インダクターを有する3ポートのスパイラルコイルにおける特性の対称性を確保し、かつ、3つのポートを、スパイラルコイルの中心を通る直線を基準として同じ側に配置すること。

【解決手段】 第1ポートと第3ポートとの間に設けられる第1インダクターと、第2ポートと前記第3ポートとの間に設けられる第2インダクターとを含むスパイラルコイルの配線構造であって、スパイラルコイルの中心を通る直線を基準として、前記第1ポートおよび第2ポートは同じ側に配置され、第1ポートから引き出される第1配線と、第2ポートから引き出される第2配線とが、スパイラルコイルの中心を通る直線を基準として、第1ポートおよび第2ポートの側において交差することによって第1交差部が設けられる。

(もっと読む)

半導体装置

【課題】電源サブ幹線に接続された内部素子に異常電圧が印加される恐れを小さく

する。

【解決手段】VSSQ0パッド143と、静電耐圧非対応素子を含むセル配置領域1(301)と、静電耐圧非対応素子よりも高い耐圧性を有する静電耐圧対応素子を含むセル配置領域2(302)と、VSSQ0パッド143を介して外部から供給される電位を静電耐圧非対応素子に供給するVSSQサブ幹線351〜353と、VSSQ0パッド143とVSSQサブ幹線351〜353との最短距離よりも長い配線長を有し、VSSQ0パッド143に入力された電位をVSSQサブ幹線351〜353に対して印加する引き込み配線部(第1VSSQ引き込み配線331とVSSQメイン幹線321と第2VSSQ引き込み配線341とからなる配線部)とを備えている。

(もっと読む)

設計支援プログラム、設計支援装置、設計支援方法、半導体素子、およびマクロ

【課題】マクロの向きが変更されても、マクロ内に配置されている複数のセルの向きおよびセル間の接続線が維持可能とし、向きの異なるマクロの生成の容易化を図ること。

【解決手段】設計支援装置は、複数の向きで配置されるマクロ内で用いられるセルのレイアウトデータから、セルの端子の配置位置を第1の端子の配置位置として検出する。設計支援装置は、複数の向きのうち、第1の端子が用いられる一の向きと異なる他の向きで用いられるセルの第2の端子の位置を、一の向きから他の向きへの変化量と第1の端子の配置位置に基づいて算出する。設計支援装置は、第1の端子の配置位置と、第2の端子の配置位置と、セルのレイアウトデータとを関連付ける。設計支援装置が、第2の端子の配置位置に端子を挿入する。具体的には、所定のビア層のビアが第2の端子の配置位置に挿入される。設計支援装置が、第1の端子と第2の端子とを接続する。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上にシリコンヒューズ5、シリコン配線パターン7、シリコンガードリング9が形成されている。シリコンガードリング9は、シリコンヒューズ5の周囲を取り囲み、シリコン配線パターン7と接触しないようにシリコン切欠き部9aをもつ。シリコンガードリング9上の層間絶縁膜11に、シリコン切欠き部9a上にビア切欠き部15aをもつビアガードリング15が形成されている。層間絶縁膜11上及びビアガードリング15上に環状の金属配線ガードリング17が形成されている。金属配線ガードリング17を覆って層間絶縁膜11上に窒化シリコン膜19が形成されている。ビア切欠き部15aにおける層間絶縁膜11と金属配線ガードリング17の界面は窒化シリコン膜19で覆われている。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】レーザートリミング加工を行うヒューズ素子を有する半導体集積回路装置の信頼性を向上させる。

【解決手段】隣り合うヒューズ素子に接続する第1層目のアルミニウム配線間のスペース幅を第1層目の金属間絶縁膜の側壁厚さの2倍未満とすることで、吸湿性のSOGの露出を防止する。また、第1層目のアルミニウム配線側面にサイドスペーサーを設けることでより一層の信頼性向上を図る。

(もっと読む)

半導体装置

【課題】ボンディングプロセス及びプロービングプロセスにより発生した応力から素子を保護し且つボンディングパッドの下側の絶縁膜にクラックが発生することのない、信頼性の高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板と半導体基板の上に形成された第1の層間絶縁膜3と、第1の層間絶縁膜3の上に形成されたパッド1と、パッド1の直下の領域において、第1の層間絶縁膜3中にそれぞれが互いに間隔をおいて独立して形成された複数の第1の配線12とを備えている。複数の第1の配線12は、パッド1の直下の領域において、第1の方向に延びる複数の第1方向配線12Aと、第1の方向と直交する第2の方向に延びる複数の第2方向配線12Bとを有する。

(もっと読む)

配線設計方法およびプログラム

【課題】配線性の低下を最小限に抑えながら、信号の特性インピーダンスの変化を抑制する。

【解決手段】ビアVに近接する特定信号配線Whがある場合、該特定信号配線Whを含む配線の配線性を評価すべき領域ERの一端LPを、特定信号配線Whの輪郭線E1〜E4のうちビアVに対向する側の輪郭線E4に一致させた上で、評価関数の値を求める。

(もっと読む)

寄生素子の抽出システムと抽出方法

【課題】ある程度の精度を保ちながらレイアウトデータから寄生素子の寄生値を抽出する時間を短縮することを可能とする。

【解決手段】寄生素子の抽出システムは、半導体装置のレイアウトを構成する各配線層を所定の基準に基づいて上層配線層と下層配線層とに分類する分類部と、上層と下層の配線層を接続するビアを示すマーカーを生成するマーカー生成部と、第1の基準に基づいて上層配線層の寄生素子を抽出することにより上層寄生素子リストを生成する上層寄生素子リスト生成部と、第1の基準と異なる第2の基準に基づいて下層配線層の寄生素子を抽出することにより下層寄生素子リストを生成する下層寄生素子リスト生成部と、マーカーを用いて上層寄生素子リストと下層寄生素子リストとを結合することによりレイアウトの寄生素子リストを生成する寄生素子リスト生成部とを備える。

(もっと読む)

設計方法

【課題】設計期間の短縮を図る。

【解決手段】設計装置11は、セルのレイアウト設計処理において、半導体装置のデザインに応じて、セルに含まれる端子に接続する信号配線を形成するための信号アクセストラック数を定量化した信号アクセス率を算出し、信号アクセス率に従って対応する端子のパターンを変更する。該信号アクセス率算出は、半導体装置の層数とロウ使用率に応じて設定された目標端子アクセス指数を記憶する記憶手段から、半導体装置に応じた目標端子アクセス指数を読み出し、前記セルの初期レイアウトデータを生成し、前記セルに含まれる端子を順次選択して着目端子とし、前記着目端子以外の端子のレイアウトをサイジングし、サイジングしたレイアウトの影響を受けない配線トラックを前記着目端子の信号アクセストラックとして抽出し、抽出した前記信号アクセストラックの数と前記目標端子アクセス指数とに基づいて、行う。

(もっと読む)

半導体記憶装置

【課題】2列パッド配置の半導体記憶装置におけるレイアウトを最適化することにより、電源電圧を安定化する。

【解決手段】メモリセルアレイ領域201,202と、これらの間に配置された周辺回路領域301と、メモリセルアレイ領域201と周辺回路領域との間に配置されたパッド列101と、メモリセルアレイ領域202と周辺回路領域との間に配置されたパッド列102と、を備える。メモリセルアレイ領域201とパッド列101との間及びメモリセルアレイ領域202とパッド列102との間に、周辺回路が実質的に配置されていない。これにより、上層の低抵抗配線を用いてメモリセルアレイ領域と所定のパッドとを短距離で接続できるため、メモリセルアレイ領域に電源電位を安定的に供給することが可能となる。

(もっと読む)

半導体集積回路

【課題】入力回路または出力回路を介して電源配線にサージ電圧が印加された場合においても、素子面積の増大を抑制しつつ、内部回路を静電破壊から安定的に保護する。

【解決手段】入出力セル3c〜3fの間の隙間に電源保護素子6a〜6dをそれぞれ配置し、電源保護素子6a〜6dとして、電源配線7、8間に接続されたダイオードストリングS2〜S5をそれぞれ用いる。

(もっと読む)

半導体装置

【課題】レーザートリミングによって除去される金属配線を有した半導体装置において、金属配線の下層の素子分離領域においてクラックの発生を抑止する。

【解決手段】例えばP型の半導体基板10には、N−型の半導体層11と隣接するP+型の素子分離領域12と、それを覆うLOCOS絶縁膜13が形成されている。これらは第1の層間絶縁膜21に覆われている。第1の層間絶縁膜21上には、ヒューズ配線として、並行して延びる金属配線23A,23B,23Cが形成されている。第1の層間絶縁膜21の貫通孔21TH内には、タングステン等からなる高融点金属層22が形成されている。この高融点金属層22は、レーザートリミングの際に生じる余分な熱を吸収するため、第1の層間絶縁膜21にクラックが生じにくくなる。

(もっと読む)

半導体装置の設計方法及び半導体装置の製造方法

【課題】溝内に配線を埋め込む際に層間絶縁膜の表面に深い凹部が生じるのを防止し得る半導体装置の設計方法等を提供する。

【解決手段】単位面積当たりの配線パターンの周囲長の総和を各々の単位領域毎に算出するステップS6と、単位領域内における配線パターンの周囲長の総和が第1の値以上である第1の領域と第2の値以下である第2の領域とを抽出するステップS7,S8と、第1の領域に隣接する第3の領域内に単位面積当たりの周囲長の総和が第3の値である第1のダミーパターンを配置し、第2の領域に隣接する第4の領域内に単位面積当たりの周囲長の総和が第4の値である第2のダミーパターンを配置するステップS9,S10と、第3の領域と第4の領域との間の第5の領域内に単位面積当たりの周囲長の総和が第3の値より小さく、第4の値より大きい第5の値である第3のダミーパターンを配置するステップS11とを有している。

(もっと読む)

半導体集積回路

【課題】複数の相補トランジスタ対(CMOS対)を同相駆動するような回路を実現するためのスタンダードセルのスペース削減、コスト低減を図る。

【解決手段】所望の回路を形成するためのセルに相補対を同相駆動するタイプのスタンダードセルを含む。例えばダブルハイトの場合、CMOS対を複数(ここでは7対)含み、その少なくとも一部(ここでは7対とも)同相駆動される。このスタンダードセルは、CMOS対の1対分に対応した基本セル長のM(ここではM=2)倍のM倍セル長で、規格化されたセル長(縦)のサイズが規定されている。同相駆動される少なくとも2対分の共通ゲート電極21,22,23が規格セル長(縦)の方向に直線配置されている。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】開口不良や形状の精度に優れたコンタクトホールを有する半導体素子の提供。

【解決手段】基板4と、基板4上に第1配線パターン2と、基板4の第1配線パターン2を有する側の面に層間絶縁膜6,8と、層間絶縁膜6,8上に第2配線パターンと、を有し、且つ層間絶縁膜6,8に第1配線パターン2および第2配線パターンを連結するためのコンタクトホールCHを備え、基板4の単位面積あたりにおいて第1配線パターン2が存在する比率(密度)が、より高い領域と、より低い領域とを有し、前記比率がより低い領域におけるコンタクトホールCHの開口面積が、より高い領域におけるコンタクトホールCHの開口面積よりも小さい半導体素子。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

81 - 100 / 566

[ Back to top ]