Fターム[5F064EE22]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699)

Fターム[5F064EE22]の下位に属するFターム

Fターム[5F064EE22]に分類される特許

101 - 120 / 566

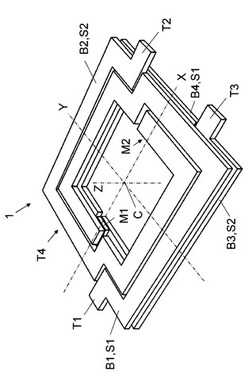

2層式トランス

【課題】それぞれ少なくとも2つの巻数からなる2つのコイルを備え、2つの導電層に実現可能であって、これによりコイルの端子がこの構造の反対側に配置される、対称型トランスのための構造を提供する。

【解決手段】積層コイル構造を持つ対称型トランスは、それぞれ少なくとも2つの巻線を有する2つのコイルを備える。該構造は、4つの同じ基本エレメントを備え、各基本エレメントは、前記コイルの一部のための導電経路を提供するものである。トランスの端子は、該構造の反対側に配置されており、構造はチェーン式に容易に接続できる。本発明はまた、こうした構造を備えた半導体デバイスに関する。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】ストレスマイグレーションにより発生する不良を容易に減少させることを図ること。

【解決手段】設計支援装置は、設計対象回路の回路情報100内の対象配線101の面積と当該対象配線101と他層の配線とを接続するビアの個数に基づいて、ビア1個あたりの対象配線101の面積が所定の規格値より大きいか否かを判断する。ビア1個あたりの対象配線101の面積が所定の規格値より大きい場合、設計支援装置は、対象配線101を分割し、他層の配線を介して分割された後の配線間を接続することでビアの個数を増加させ、ビア1個あたりの対象配線101の面積を小さくすることができる。

(もっと読む)

電子部品装置および変化部品の製造方法

【課題】製造ばらつき等に対しても、高品質で電気的接続状態を変化させる。

【解決手段】電子部品装置200は、第1のヒューズ素子102aを含む第1のヒューズユニット100a、および第2のヒューズ素子102bを含む第2のヒューズユニット100bを含む電気ヒューズ101と、第1のヒューズ素子102aおよび第2のヒューズ素子102bの少なくともいずれか一方が電気的に切断されている場合に、電気ヒューズ101が電気的に切断されていると判定する判定回路150とを含む。第1のヒューズユニット100aおよび第2のヒューズユニット100bは、それぞれ独立に電流が印加され、所定の電流または電圧を印加した場合に電気的接続状態の変化が生じない割合に影響を与える制御パラメータの適正範囲が異なるように構成されるかまたは、値の異なる電流により切断される。

(もっと読む)

レイアウト設計システム、及びレイアウト設計方法

【課題】配線修正などのデータ量が処理速度に依存する処理を、処理能力の低く、少ないメモリを搭載した安価なコンピュータで設計可能にする。

【解決手段】半導体集積回路のレイアウト設計において、レイアウトデザインに応じて使用頻度の高いレイアウトセルを選択してダミーメタルを配置する共通な場所(座標)を特定し、特定した配置箇所に予めダミーメタルを配置した新規のレイアウトセルを作成する工程と、新規のレイアウトセルの作成元である使用頻度の高いレイアウトセルを、ダミーメタルを有する新規のレイアウトセルとを置換、もしくは重ね合わせて配置してダミーメタルを配置する工程と、を実施する。

(もっと読む)

半導体集積回路

【課題】機能マクロセルの周辺において、配線を形成するための領域を十分に確保する。

【解決手段】半導体集積回路100は、機能マクロセル110に形成される機能マクロセル用電源配線181と、機能マクロセル110の内部に形成される電源配線261と、機能マクロセル110の内部に形成され、機能マクロセル用電源配線181と電源配線261とを電気的に接続するコンタクト170と、コンタクト170と、論理セルとを電気的に接続する電源配線とを備える。機能マクロセル用電源配線181は、論理セル電圧を、コンタクト170および電源配線を介して、論理セルへ供給する。

(もっと読む)

テストデータ生成方法

【課題】 複数のテストデータを準備することなく、検証プログラムをテストすることができるテストデータを生成する技術を提供する。

【解決手段】 テストデータ生成方法は、第1平面データ生成工程と第2平面データ生成工程とテストレイアウトデータ生成工程とを備える。第1平面データ生成工程は、夫々が各レイヤに対応している擬似レイヤを有する擬似レイヤ群が一つの平面上に規則的に配置された第1平面データを生成する。第2平面データ生成工程は、擬似レイヤ群が他の一つの平面上に規則的に配置された第2平面データであり、第1平面データと重ね合わせたときに第2平面データ上の各擬似レイヤが第1平面データ上の各擬似レイヤと重なる第2平面データを生成する。テストレイアウトデータ生成工程は、第1平面データと第2平面データとが重なり合ったレイアウトデータを含むテストレイアウトデータ70を生成する。

(もっと読む)

半導体集積回路

【課題】電源線のレイアウト面積を広げることなく、コア回路とバイアス供給回路との間

の電圧降下を抑え、かつ、コア回路間の高速信号ノードを短縮できるようにする。

【解決手段】Si基板11にトランジスタQ及び抵抗素子Rを有して高電位側の電源線と

低電位側の配線D1とバイアス供給用の配線D2とに接続されてトランジスタ動作をする

コア回路1と、Si基板11に設けられてコア回路1にバイアスを供給するバイアス供給

回路とを備え、コア回路1の中の定電流源用のトランジスタQに、その一端が接続された

抵抗素子Rの他端がバイアス供給用の配線D2に接続され、この配線D2が接続された抵

抗素子Rの他端がコンタクトホール35を介してバイアス供給用の配線D2よりも上層の

低電位側の配線D1に接続されるものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるセル列に配置されたセル間をセル間の配線に用いられる配線層を用いずにセル内配線に用いられる配線層を用いて配線する半導体装置及び半導体装置の製造方法を提供する。

【解決手段】スタンダードセルが並べて配置されたセル列であって、互いに平行に列が延びる方向の辺で接して配置された第1及び第2のセル列を備え、第1のセル列に配置された第1のセルの入力配線、出力配線、入出力配線のいずれかの配線である第1の入出力機能配線が、第2のセル列に配置された第2のセルの第2の入出力機能配線と同一の配線層で接続されている。

(もっと読む)

不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置

【課題】高速動作が可能で、しかも可逆的に安定した書き換え特性を有し、半導体製造プロセスと親和性の高い不揮発性記憶素子およびその製造方法、並びにその不揮発性記憶素子を用いた不揮発性半導体装置の提供を目的とする。

【解決手段】第1電極103と、第2電極105と、第1電極103と第2電極104との間に介在させ、両電極103,105間に与えられる電気的信号に基づいて可逆的に抵抗値が変化する抵抗変化層104とを備えている。この抵抗変化層104は少なくともハフニウム酸化物を含み、当該ハフニウム酸化物をHfOxと表した場合に、0.9<x<1.6を満足するように抵抗変化層104が構成されている。

(もっと読む)

半導体装置

【課題】半導体装置のレイアウトの自由度を向上させる。

【解決手段】本発明による半導体装置は、第1行おいて、行方向に連続的に配置される第1電源供給セル20及び複数の第1セル10と、第1行に隣接する第2行において、行方向に連続的に配置され、前記第1行に隣接する複数の第2セル10とを具備する。第1電源供給セル20は、行方向に直交する第1電源配線62に接続され、第1電源配線62から供給される電圧に応じた電源電圧を、複数の第1セル10及び複数の第2セル10に供給する。第2行において、第1行に配置された第1電源供給セル20に隣接する第2セルと第1電源配線62とは、直接接続されず第1行に配置された第1電源供給セル20を介して接続される。

(もっと読む)

半導体集積回路のレイアウト方法及び論理修正方法

【課題】論理ゲートや論理ゲートの入出力端子の配置にかかわらず、信号配線の引き出し端子を密集させることなく配置すること。

【解決手段】本発明は、複数の論理ゲート309に接続された配線層301〜303を、論理ゲート出力端子306と論理ゲート入力端子307又は論理ゲート出力端子306及び論理ゲート入力端子307と配線分岐点308とを結ぶ線分に分割する。続いて、この線分において、この線分よりも上層の配線層に配置された配線が最も少ない点を、仮想分割点として抽出する。そして、この線分を仮想分割点にて分割することにより、仮想分割配線401を生成する。続いて、仮想分割配線401を構成する配線層と、配線層303とを接続する追加配線501を配置する。追加配線501は、仮想分割点の直上を避けて配置される。

(もっと読む)

半導体集積回路の設計方法及び設計システム

【課題】デザインルールエラーやショートの発生を抑制しながら、設計TATを短縮すること。

【解決手段】半導体集積回路の設計方法は、(A)配線パターン及び特殊パターンが配置されたレイアウト領域を複数の分割領域に分割する。デザインルールで規定される最小間隔は、配線パターンよりも特殊パターンの方が大きい。設計方法は更に、(B)各分割領域に関して、各分割領域を囲む所定幅の領域中に含まれる特殊パターンを周辺パターンとして抽出するステップと、(C)各分割領域に関して、各分割領域に包含されるダミーパターン配置領域を決定するステップ。設計方法は更に、(D)各分割領域の周囲にある上記抽出された周辺パターンとのデザインルールエラーを回避しながら、各分割領域のダミーパターン配置領域にダミーパターンを追加するステップと、(E)ダミーパターンが追加された複数の分割領域同士を結合するステップ。

(もっと読む)

半導体装置

【課題】局所的な電圧降下を効果的に抑制できる電源配線構造を有した半導体装置を提供する。

【解決手段】第1配線層は複数の第1配線ブロック10を含み、当該各第1配線ブロック10には、第1電位を持ち且つ少なくとも二方向以上に延びる第1配線11と、第1電位と異なる第2電位を持ち且つ少なくとも二方向以上に延びる第2配線12とが配置されている。第2配線層は、隣り合う一対の第1配線ブロック10における第1配線11同士を電気的に接続する第3配線21と、当該一対の第1配線ブロック10における第2配線12同士を電気的に接続する第4配線22とを含む。

(もっと読む)

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

ダミーパターンの配置方法及びダミーパターンを備えた半導体装置

【課題】従来よりも簡単にダミーパターンを配置し、スクライブ領域に隣接した半導体チップの形成領域において、層間絶縁膜が薄くなるのを抑制する方法を提供する。

【解決手段】配線層を備えた半導体チップの形成領域と、該形成領域を囲むスクライブ領域とを備えた半導体チップにおいて前記配線層と同じ層からなるダミーパターンを配置する方法であって、前記配線層から少なくとも所定距離だけ離間する位置に第1のダミーパターンを設定する段階と、前記スクライブ領域に隣接する所定幅の範囲内において、前記配線層から少なくとも所定距離だけ離間しかつ前記第1のダミーパターンから少なくとも所定距離だけ離間する位置に第2のダミーパターンを設定する段階と、を備えたダミーパターンの配置方法を提供することによって、上記課題を解決できる。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の特性を保持或いは高めると共に小型化を図る。

【解決手段】 主面および前記主面とは反対側の裏面を有し、第1辺を含む平面形状が矩形状の半導体基板と、前記主面上に形成された複数のボンディングパッドと、前記主面上に形成された内部回路形成部と、前記第1辺と前記内部回路形成部との間に配置されており、前記内部回路形成部に電位を供給する内部回路用電源配線と、前記第1辺と前記内部回路用電源配線との間に配置されており、前記複数のボンディングパッドと電気的に接続され、トランジスタを備えた複数のセルと、前記複数のセル上に配置され、前記複数のセルに電位を供給するセル用電源配線と、を有し、前記複数のセルは、外部からの入出力信号を送受信する回路を含む入出力セルを有し、前記複数のボンディングパッドのそれぞれは、前記入出力セルと平面的に重なるように配置されている。

(もっと読む)

半導体集積回路チップおよびそのレイアウト方法

【課題】フリップチップ接合により基板に実装される半導体集積回路チップについてIOセルが配置されずに空いた領域を有効利用する。

【解決手段】半導体集積回路チップ(1)は、複数の電極パッド(10)と、内部層の平面周縁のコーナー部(15a)と、コーナー部の1辺に隣接した第1の直線領域(15b)と、コーナー部の他の1辺に隣接した第2の直線領域(15c)と、第1の直線領域の、コーナー部と反対側に隣接した第3の直線領域(15d)を備えている。コーナー部と第1の直線領域のうちの少なくとも一部には回路コア配置領域(18)が配置され、第2および第3の直線領域には複数の電極パッドとそれぞれ接続される複数のIOセル(11)が配置され、第2の直線領域の複数のIOセルはコーナー部の上部である当該チップのコーナー部から内方にn行×n列内の複数の電極パッドとそれぞれ接続されている。

(もっと読む)

スタンダードセルおよび半導体装置

【課題】回路動作に必要な配線を形成するための領域が広く、回路の高速動作が可能なスタンダードセルを提供する。

【解決手段】第1のMOS素子および第2のMOS素子に信号を供給するための信号線が、電源配線および接地配線の2つの配線と平行に設けられ、これら2つの配線に挟まれ、かつ、第1の導電型MOS素子および第2の導電型MOS素子のそれぞれから等しい距離に配置されている構成である。

(もっと読む)

レイアウト設計方法、レイアウト設計プログラム、レイアウト設計装置

【課題】内部回路領域に複数の電源系統を持つ半導体集積回路に関してチップ面積の小さいレイアウトを生成することを可能にする。

【解決手段】内部領域に第1電源の電源供給線の配線を生成する。その電源供給線に接続されるように複数のプリミティブセルの各々の配置を生成する。第1電源の電源供給線から複数のプリミティブセルの各々に供給される信号のタイミングが所定の基準を満たすか否かの確認を行う。その所定の基準を満たすことが確認された後に、複数のプリミティブセルの中の少なくとも一つの電源分離対象セルに対して、第1電源が供給する第1電位に替えて第2電源が生成する第2電位を供給するために配線する。

(もっと読む)

101 - 120 / 566

[ Back to top ]