Fターム[5F064EE22]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699)

Fターム[5F064EE22]の下位に属するFターム

Fターム[5F064EE22]に分類される特許

161 - 180 / 566

レイアウト密度検証システム、レイアウト密度検証方法、及びレイアウト密度検証用プログラム

【課題】メタル密度チェックの精度を向上し、メタル密度チェック実行時のメモリ使用量、処理負荷、及び処理時間を削減する。

【解決手段】LSIレイアウト設計用マクロモデルにおいて、メタル密度チェックを行う際にチェック単位となるウィンドウの1辺の長さ分と同等、もしくは長さ分以上だけ、マクロ外周部から内側にレイアウト形状を見せるような構造を持たせたマクロモデルを作成することで、マクロモデル使用時のメタル密度チェックの精度を向上させると共に、処理実行時のメモリ消費量及び実行時間の削減を行う。

(もっと読む)

半導体装置の作製方法

【課題】機能を制限することによって利用可能な半導体装置の作製方法を提供する。

【解決手段】半導体装置が有する、同時に使用する複数の機能回路の検査を行う。検査によって動作が規格に則していないと判定された機能回路と制御回路とを電気的に接続する信号線を、レーザーを用いて切断することによって、制御回路によって機能回路が制御されず、動作しない状態とする。また、規格に則していないと判定された機能回路に電気的に接続された第1の信号線と、機能回路が動作しない電位に固定された第2の信号線と、を絶縁する絶縁体を、レーザーを用いて除去することによって、第1の信号線と第2の信号線とを電気的に接続し、機能回路が動作しない状態とする。

(もっと読む)

配線設計方法と配線設計装置及び配線設計プログラム

【課題】従来技術よりもDRCエラーの少ない(結線率の高い)配線結果を得ることのできる配線設計方法を提供する。

【解決手段】第1配線部分とボンディングワイヤを介して接続された第2配線部分を有したSiPの配線を設計するための配線設計方法であって、第1配線部分又は第2配線部分のDRCエラーの有無を判定し、DRCエラーが有る場合に該エラーを選択する工程(S101)、選択されたDRCエラーに関する複数のネットを特定する工程(S103)、特定されたネットの配線を引き剥がす工程(S104)、特定されたネットのボンディングワイヤ割り当てを変更する工程(S105)、特定されたネットをDRCエラーが生じないように再配線する工程(S106)、再配線の結果を受け入れるか否かを判断する工程(S107)、を有する。

(もっと読む)

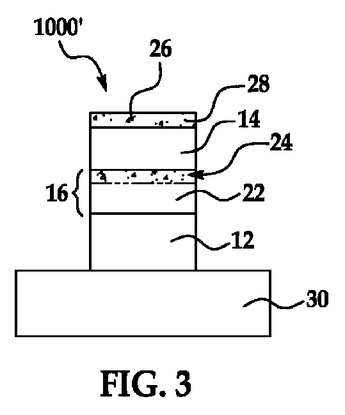

電気的に作動するデバイス及びそのデバイスにおけるドーパントの形成を制御する方法

電気的に作動するデバイスが、第1の電極、第2の電極並びに当該第1及び第2の電極間に堆積させた活性領域を備えている。当該デバイスは、i)第1の電極と活性領域との界面、又はii)第2の電極と活性領域との界面、又はiii)活性領域と第1及び第2の電極のそれぞれとの各界面で局在化された、少なくとも1つのドーパント導入剤又はドーパントをさらに含む。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】分周回路において消費電流を削減することを課題とする。特に、多段の分周回路において消費電流を削減すること課題とする。

【解決手段】多段の分周回路100では、初段ほど入力される信号の周波数が高く、後段ほど入力される信号の周波数は低くなる。よって、高い周波数の信号が入力される分周回路に対応する基本セル(D1)から優先的に配置し、配線接続を行う。つまり、高い周波数の信号が入力される配線を、より低い周波数の信号が入力される配線と比較して、配線長が短く、他の配線との交差が少なくなるように、即ち配線の寄生容量、寄生抵抗が小さくなるように、多段の分周回路に対応する複数の基本セルをレイアウトする。

(もっと読む)

半導体装置

【課題】面積の増加なしに、印加電圧の揺らぎの許容範囲を広くする。

【解決手段】半導体装置200は、電気ヒューズ100と、電気ヒューズ100に電圧を印加するための第1の大面積配線116および第2の大面積配線126とを含む。電気ヒューズ100は、上層ヒューズ配線112と、下層ヒューズ配線122と、上層ヒューズ配線112および下層ヒューズ配線122とを接続するビア130と、から構成されるヒューズユニット102と、上層ヒューズ配線112と第1の大面積配線116とを接続するとともに、屈曲したパターンを有する上層引出配線114と、下層ヒューズ配線122と第2の大面積配線126とを接続するとともに、屈曲したパターンを有する下層引出配線124とを含む。

(もっと読む)

配線パターン設計方法およびプログラム

【課題】レイアウト設計の自由度を維持したまま、配線用の冗長部分を削除可能にした配線パターン設計方法を提供する。

【解決手段】回路情報およびセル情報に基づいて、セルの枠にその両端が接する線分の第1の配線パターンと、第1の配線パターンに第1のビアを介して接続される第2の配線パターンと、第1の配線パターンに第2のビアを介して接続される第3の配線パターンとをセルに配置し、第1および第2のビアのそれぞれの位置を特定し、第1のビアおよび第2のビアに対して互いに対向する側にそれぞれサイズを拡大して1つにしたリサイズパターンを生成し、リサイズパターンに対応する、第1の配線パターンの部位をマスクパターンに決定するものである。

(もっと読む)

半導体装置

【課題】製造バラツキに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置200は、基板(不図示)上に形成された上層ヒューズ配線112、下層ヒューズ配線122、および上層ヒューズ配線112の一端と接続され、上層ヒューズ配線112と下層ヒューズ配線122とを接続するビア130から構成される電気ヒューズ100を含む。上層ヒューズ配線112には、一端側で配線幅が狭くなった幅変動領域118が設けられている。

(もっと読む)

半導体装置

【課題】チップ内における配線領域の占有面積の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】ゲート電極、ソース領域およびドレイン領域をそれぞれが有する第1および第2のトランジスタ121,122と、第1トランジスタ121のソースおよびドレイン領域の一方と第2トランジスタ122のソースおよびドレイン領域の一方と互いに連結する拡散領域150とを備える半導体装置110を採用する。

(もっと読む)

半導体装置

【課題】サイズおよびコストを抑えることができる半導体装置を提供する。

【解決手段】pMIS領域は、方向Xに沿って複数のスタンダードセルCffの各々を通る境界BRと、第1の外縁OTpとの間に形成されている。nMIS領域は、境界BRと第2の外縁OTnとの間に形成されている。電源配線VDおよび接地配線VSのそれぞれは、第1および第2の外縁OTp、OTnに沿って延びている。複数のpMIS配線M1pおよび複数のnMIS配線M1nのそれぞれは、方向Xに沿って延びかつ方向Yに沿ってピッチPminで配置された複数の第1の仮想ラインVLpおよび複数の第2の仮想ラインVLnの上に配置されている。複数の第1の仮想ラインVLpのうち境界BRに最も近いものと、複数の第2の仮想ラインVLnのうち境界BRに最も近いものとの間隔は、ピッチPminよりも大きい。

(もっと読む)

FETスイッチ

【課題】1入力多出力スイッチおよび多入力1出力スイッチとして、広帯域化ならびに小型化・低コスト化が可能なFETスイッチを提供する。

【解決手段】第1の端子とn個(n:正整数、図1の場合n=4)の第2の端子との間の切替制御を行うSPnTスイッチとして、第1の端子と接続した配線210を分岐点Aにてn分岐した配線211〜214に、それぞれ、n個のFET41〜44のソースまたはドレインを接続し、n個のFET41〜44のドレインまたはソースには、それぞれ、配線221〜224を介して第2の端子を接続するとともに、少なくとも、配線211〜214を、それぞれ、直線で形成し、かつ、それぞれの長さを互いに等しくする。

(もっと読む)

半導体集積装置及び自動配置配線方法

【課題】セル内の抵抗成分を考慮して自動配置配線が行われた高密度セルを備えた半導体集積装置及び自動配置配線方法を提供する。

【解決手段】ライブラリ内に蓄積されたセルX1及びセルY2を含む2種類以上のセルから、所定の条件に基づいて選択されたセルが配列された半導体集積装置であって、ライブラリ内に格納された各々のセルの拡散抵抗値を示す情報に基づいて、隣接する列において自動配線配置における最大値ルールを満たすように選択されたセルX1、セルY2が配列されている。

(もっと読む)

半導体装置及び半導体装置の設計方法及び半導体装置の設計装置

【課題】フローティングな状態のダミーパターンの発生抑止と、半導体装置の配線層のパターン密度の均一化との両立を容易化する。

【解決手段】半導体装置の設計装置は、半導体装置のレイアウトデータからダミーパターンを生成する層の配線パターンを抽出する。次に、半導体装置の設計装置は、前記配線パターンから固定電位パターンを抽出する。次に、半導体装置の設計装置は、前記固定電位パターンを取り除いたパターンを反転させ、かつ、反転前のパターンと反転後のパターンとの間に間隙が生じるようにしたダミーパターンを生成する。次に、半導体装置の設計装置は、前記ダミーパターンと、下層又は上層の固定電位パターンとを層間接続する。最後に、半導体装置の設計装置は、前記ダミーパターンデータ及び前記層間接続データを前記レイアウトデータに合成する。

(もっと読む)

自動配線装置、自動配線方法および自動配線プログラム

【課題】最小メタル面積エラーを適切に防止しつつ、LSIの高密度化を実現することを課題とする。

【解決手段】自動配線装置10は、メタル面積を矩形に分割し、分割された各矩形の面積を計算し、各矩形の面積の合計を計算し、計算されたメタル面積が所定の閾値である最小メタル面積より小さいか否かを判定する。そして、自動配線装置10は、メタル面積が最小メタル面積より小さいと判定された場合には、メタル面積が最小メタル面積以上となるように、LSIの配線を修正する。

(もっと読む)

レイアウトパターン生成方法、半導体装置の製造方法、プログラム、レイアウトパターン生成装置

【課題】リワークセル上でのダミー配線に起因するショートエラーを抑制すること。

【解決手段】レイアウトパターン生成方法は、半導体チップ領域に配置されたリワークセルとフィルセルのうち、編集に使用されるリワークセルを特定し、該特定リワークセルの配線層に所定形状の特定パターンを生成するステップと、前記リワークセルのうち前記特定リワークセル以外の非特定リワークセルと前記フィルセルの少なくとも一部の前記配線層にダミー配線パターンを配置するステップと、前記特定リワークセルの前記配線層から前記特定パターンを削除するステップと、前記特定リワークセルを論理セルとして配線して、前記特定リワークセルの前記配線層に配線パターンを配置するステップとを具備している。

(もっと読む)

半導体装置の製造方法

【課題】高集積化が容易で製造コストが増加しないヒューズ回路を有する半導体装置の構造及びその製造方法、並びに、このようなヒューズの切断に適したレーザ装置を提供する。

【解決手段】下地基板10上に形成されたブロック層12と、ブロック層12上に形成された絶縁膜14と、絶縁膜14上に形成されたヒューズ22とにより半導体装置を構成する。ヒューズ22の下層部にブロック層12を設けることにより、レーザアブレーションによりヒューズを切断し、且つ、ブロック層12によってレーザアブレーションを制御性よく停止することができる。

(もっと読む)

半導体チップ

【課題】 加工処理を行なうための加工位置を精度よく特定することができる半導体チップを提供する。

【解決手段】 複数の半導体回路素子が形成され、それら半導体回路素子上に層間絶縁膜と配線層とが交互に積層されてなる半導体チップ10において、この半導体チップ10を構成する最上層の配線層であるダミーメタル13に、半導体チップ10上のX座標の位置を表わすX座標用コードパターン13_1およびY座標の位置を表わすY座標用コードパターン13_2を付加した。

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含む電気ヒューズ100であって、切断状態において、電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、上層配線110および下層配線120の一方と同層に上層配線110および下層配線120の一方の側方に形成されるとともに、上層配線110および下層配線120と電気的に接続された熱拡散用上層配線152aを含む熱拡散部150aとを含む。

(もっと読む)

LSIの設計方法

【課題】LSIの設計において、電源ノイズによる電源電圧変動を考慮した論理セルの配置を実現する。また、論理セルのタイミング保証のためのマージンを小さくしてチップサイズの縮小を図る。

【解決手段】互いに交差してグリッドを形成した複数の電源線と、電源線から電源供給を受ける複数の論理セルとを有するLSIの設計方法において、電源線上の複数の点における電圧波形を取得し、電圧波形から最小電圧を求め、電源線の複数の点の中の2点間の距離に対する前記最小電圧の空間相関を表す相関係数を求め、その相関係数に基づいて複数の論理セルの配置を決定する。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置のロジック領域に冗長救済を行う構成を提供することを目的とする。

【解決手段】本発明の1つの実施の形態は、ロジック領域2を有する半導体装置1である。そして、当該半導体装置1は、ロジック領域2内に設けられる同一の構成を有する複数の基本セル21と、複数の基本セル21と同一の構成を有する冗長セル22と、複数の基本セル21及び冗長セル22のそれぞれに入力される信号を切り替える入力セレクタ23と、基本セル21及び冗長セル22のそれぞれから出力される信号を切り替える出力セレクタ24とを備えている。さらに、当該半導体装置1は、入力セレクタ23及び出力セレクタ24のうち少なくとも一方を切り替えて、冗長セル22を機能させ複数の基本セル21のうち故障したセルを救済する。

(もっと読む)

161 - 180 / 566

[ Back to top ]