Fターム[5F064EE27]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | コンタクト手段 (1,033)

Fターム[5F064EE27]に分類される特許

41 - 60 / 1,033

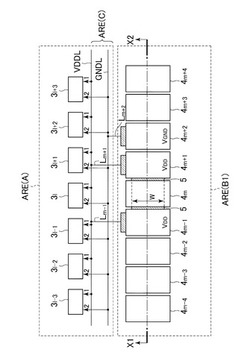

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

レイアウト設計方法、および、レイアウト設計プログラム

【課題】チップ面積の増大を抑制しつつ、ダミー配線パターンの配置にかかる工数を低減する。

【解決手段】レイアウト設計方法は、レイアウト設計装置が、レイアウト領域に対して、半導体集積回路の配置配線(S1)を行った後、レイアウト領域に配置されているバルクセルを抽出し(S2)、レイアウト領域において、抽出したバルクセルの周囲に、所定の大きさを備える空き配線領域が存在するかどうかを検索し(S3)、検索の結果、所定の大きさを備える空き配線領域を検出した場合、抽出したバルクセルの座標を基準にして、検出した空き配線領域にダミー配線パターンを配置(S4)する。

(もっと読む)

レイアウト検証装置、レイアウト検証方法、及びプログラム

【課題】半導体集積回路のレイアウト検証であって、検証済のレイアウトパタンデータへ部分的に変更を加えた後で行うDRC検証において、検証の対象とならない箇所に対するDRC検証の時間を省略し、アンテナ比のようなDRC検証の時間を短縮する。

【解決手段】検証済のレイアウトパタンデータへ部分的に変更を加えた後で行うDRC検証において、変更箇所から等電位追跡を用いてDRC検証の検証対象箇所を特定する。具体的には、変更前後のレイアウトパタンデータの差分図形を抽出して該差分図形から変更ノードを抽出する。また、変更後のレイアウトパタンデータに対して等電位番号を付与して該等電位番号を参照して該変更ノードと同じ等電位番号を持つ検証対象箇所を抽出する。更に、前抽出された記検証対象箇所に対して、アンテナ比のDRC検証を実行する。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体集積回路装置

【課題】標準論理セルのセル高さを縮小する。

【解決手段】第1,第2,第3の電源配線(WP1,WP2,WP3)および複数の第1の信号配線(WS1)は、半導体基板の上層に形成され、少なくとも1つの第2の信号配線(WS2)は、複数の第1の信号配線(WS1)の上層に形成される。第1および第2の電源配線(WP1,WP2)は、セル高さ方向に互いに離間してセル幅方向に延伸する。第3の電源配線(WP3)は、第1および第2の電源配線(WP1,WP2)の間をセル幅方向に延伸する。複数の第1の信号配線(WS1)は、第1,第2,第3の電源配線(WP1,WP2,WP3)から離間し、複数の回路要素(DF,GW)の少なくとも1つに電気的に接続される。少なくとも1つの第2の信号配線(WS2)は、セル幅方向に延伸し、複数の回路要素(DF,GW)および複数の第1の信号配線(WS1)の少なくとも1つに電気的に接続される。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の電源線および接地線の高抵抗化を抑制する。

【解決手段】第1の方向に延伸された第1の回路セル列及び第2の回路セル列と、第1の方向に延伸され、第1の回路セル列上に配置され、第1の電源線には第1の電源電位が供給される、第1及び第2の電源線と、第1の方向に延伸され、第2の回路セル列上に配置され、第2の電源電位が供給される第3の電源線と、第2の電源線と第3の電源線との間に接続され、導通状態において第2の電源線と第3の電源線とを接続して第3の電源線から第2の電源線に第2の電源電位を供給し、非導通状態において第2の電源線と第3の電源線とを電気的に切り離す第1のトランジスタと、第1の回路セル列に配置され、第1の電源線から供給される第1の電源電位と第2の電源線から供給される第2の電源電位との間の電源電圧で動作する第1の回路素子とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ロジック回路を含む半導体装置に関し、処理時間を短縮し製造コストを低減する。

【解決手段】ロジック回路の形成領域(114)は、所定の精度で光近接補正処理された第1領域(114b,170)と、所定の精度より低い精度で光近接補正処理された第2領域(114a,180)とを備える。特に第1領域(114b,170)は、トランジスタとして動作するゲート配線(172)を有し、第2領域(114a,180)は、トランジスタとして動作しないダミーレイアウト(182)を有する。

(もっと読む)

電気ヒューズ、半導体装置、及び、電気ヒューズの情報書き込み方法

【課題】 例えば半導体集積回路等のチップに搭載する電気ヒューズの容量を省スペースで効率よく増加させることのできる電気ヒューズ、及び、それを備える半導体装置を提供する。

【解決手段】 電気ヒューズは、第1導電層4と、第1導電層4上に形成された第2導電層5とを有しフィラメント1を備える。そして、フィラメント1は、第1導電層4の状態及び第2導電層5の状態の組み合わせを変えることにより、少なくとも3つの識別可能な抵抗状態が生成されるように構成される。

(もっと読む)

設計支援プログラム、該プログラムを記録した記録媒体、設計支援方法、および設計支援装置

【課題】半導体集積回路の長寿命化、および設計期間の短縮を同時に実現すること。

【解決手段】設計支援装置700は、検出部701により、レイアウト情報によって表現された設計対象回路から配線間を接続するビアを検出する。つぎに、決定部702により、配線間を接続しないダミービアの接続位置を、検出部701によって検出されたビアに接続された配線のうち、少なくとも一つの配線上の位置に決定する。そして、挿入部704により、決定部702によって決定された接続位置にダミービアを挿入する。

(もっと読む)

半導体集積回路装置

【課題】電源幹線内で同電位の電源線を相互に接続することにより配線抵抗を削減するとともに、電源幹線間で同電位の電源線を接続することにより配線抵抗をさらに削減できるようにすること。

【解決手段】半導体集積回路装置は、第1の層において第1の方向に延伸する第1の電源線および第2の電源線と、第2の層において第1の方向に延伸するとともに第1の電源線の直上に設けられた第3の電源線と、第2の層において第1の方向に延伸するとともに第2の電源線の直上に設けられた第4の電源線とを備え、第1の電源線および第2の電源線は第1の方向に延伸するセル棚(セル列)に含まれる複数のセルに電源を供給し、第3の電源線は第1の電源線の電位と異なる電位が供給され、第4の電源線は第2の電源線の電位と異なる電位が供給される。

(もっと読む)

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

41 - 60 / 1,033

[ Back to top ]