Fターム[5F064EE27]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | コンタクト手段 (1,033)

Fターム[5F064EE27]に分類される特許

81 - 100 / 1,033

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

チャージアップダメージの検証方法および検証装置

【課題】 配線と非配線とを分けて扱い、マクロ等にも半導体集積回路全体にも適用できるアンテナルールを用いるチャージアップダメージの検証方法等を提供できる。

【解決手段】 配線層毎のアンテナ比の上限値を、注目配線層の階層数と総配線層数とに基づいて設定する第1のステップS10、半導体集積回路のレイアウトデータに基づいて、配線層毎に所与のゲートにチャージアップダメージを与えるノードの面積を演算し、下位の配線層に含まれる同一のノードの面積との積算値を求める第2のステップS20、半導体集積回路のモジュール毎に、注目モジュールに含まれる所与のゲートにチャージアップダメージを与えるノードについて、注目モジュールの最上位配線層までの面積の積算値と所与のゲートの面積とに基づいてアンテナ比を求め、注目モジュールの最上位配線層におけるアンテナ比の上限値と比較する第3のステップS30を含む。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

半導体集積回路装置

【課題】メーカーの設計負担を増加させることなくセルタイプの異なるICを実現することができるとともに、チップサイズおよび消費電力並びに動作速度が最適化された半導体集積回路を容易に実現可能な設計技術を提供する。

【解決手段】所望の機能を有する回路セルの設計情報を目的別にオブジェクトとして記述し、所定のオブジェクトの情報の削除もしくは追加のみで基体電位固定型セルと基体電位可変型セルのいずれをも構成可能なセル情報として、セルライブラリに登録するようにした。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、半導体基板の上方に形成された半導体素子と、半導体素子の上方に形成された第1絶縁膜と、第1絶縁膜上に形成されたアルミニウム(Al)を含有する第1導電性膜よりなるヒューズ素子Fと、を有する。さらに、第1絶縁膜上に形成され、第1導電性膜よりなる第1配線と、第1配線上に形成された第2絶縁膜と、を有し、ヒューズ素子Fのプログラム領域は、第2絶縁膜に設けられた開口部OA1から露出している。また、ヒューズ素子Fのプログラム期間およびヒューズ素子にプログラムされたデータの読み出し期間以外の期間において、ヒューズ素子Fの両端を接地電位に維持する。例えば、ヒューズ素子Fの一端は、接地電位に接続され、他端は、スイッチング素子を介して接地電位に接続されている。

(もっと読む)

半導体集積回路のレイアウト設計装置、半導体集積回路のレイアウト設計方法及びプログラム

【課題】信号の遅延調整を柔軟に行なうことができる半導体集積回路レイアウト設計装置を提供する。

【解決手段】図1に示す半導体集積回路レイアウト設計装置は、配線部と遅延調整部を備える。配線部では、第1の配線層の配線上に、第2の配線層では接続先となる配線がないビア(未接続ビア)を形成する。その後、遅延調整部において、遅延時間の調整が必要であれば、未接続ビアから、遅延調整に適したビアを選択し、第1の配線上のビア間の配線を削除する。その後、第2の配線層において第1のビアと第2のビアを配線する。その結果、信号配線の抵抗は、ビアの持つ抵抗値の分上昇し、遅延時間の調整を行なうことができる。

(もっと読む)

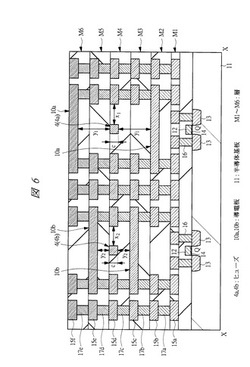

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】金属シリサイド層を利用した電気ヒューズの信頼性を向上する。

【解決手段】半導体装置50は、電気ヒューズ16を有する。電気ヒューズ16は、第1の端子領域16aと、第2の端子領域16bと、第1の端子領域16a及び第2の端子領域16bを接続するヒューズリンク領域16cとを備える。ヒューズリンク領域16cは、第1のシリコン膜12cと、第1のシリコン膜上に形成された第1の金属シリサイド層15cとを有する。平面視において、第1の端子領域16aと第2の端子領域16bとが並ぶ方向に垂直な方向の寸法を幅とするとき、第1のシリコン膜12cの少なくとも一部の幅は、第1の金属シリサイド層15cの幅よりも大きい。

(もっと読む)

集積回路デバイス

【課題】プロセス寸法の縮小に伴う光相互作用の予測品質の低下を抑止する。

【解決手段】ゲートレベル仮想格子の、連続的に隣接して配置された少なくとも3本の仮想ラインのそれぞれは、その上に定義された少なくとも1つの線形導電体形状を有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第1の仮想ラインは、その上に定義され、第1の終端−終端間スペーシングで分離された2つの線形導電体セグメントを有し、ゲートレベル仮想格子の少なくとも3本の仮想ラインの第2の仮想ラインは、その上に定義され、第2の終端−終端間スペーシングで分離された他の2つの線形導電体セグメントを有し、第1の仮想ラインに沿って測定された第1の終端−終端間スペーシングの寸法は、第2の仮想ラインに沿って測定された第2の終端−終端間スペーシングの寸法に等しく、ゲートレベル仮想格子の仮想ラインは、いかなる導電体形状によっても占有されない。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】半導体集積回路のレイアウト設計において、幅が広い第1の配線と幅が狭い第2の配線との間に無駄なスペースが発生することによる配線性の悪さを改善する。

【解決手段】このレイアウト設計方法は、回路情報に基づいて、レイアウト領域において複数の横ラインと複数の縦ラインとが交差する格子点上に、複数の回路素子の接続点を配置するステップ(a)と、回路情報及び複数の回路素子の配置に基づいて、いずれかの横ライン又は縦ラインの位置を始点として、第1の方向に格子間隔よりも大きい所定の幅を有する第1の配線を配置するステップ(b)と、ステップ(b)において配置された第1の配線に第1の方向と反対の第2の方向において隣接する横ライン又は縦ライン上に、最小幅を有する第2の配線を配置するステップ(c)とを含む。

(もっと読む)

半導体集積回路

【課題】例えばクラック発生などに起因する大量生産段階での低歩留りという問題を防止できる半導体集積回路を提供する。

【解決手段】パッドメタルの下に回路を有する半導体集積回路において、パッド開口部分のパッドメタルの少なくとも下全面に、互いに同一の電位を有する配線メタルを形成し、当該配線メタルの電位を上記パッドメタルと異なる電位に設定した。また、上記配線メタル、及び上記配線メタル以外の電位を有する別の配線メタルは、上記パッドメタルよりも下層に形成される。さらに、上記半導体集積回路の複数のパッドにおいて、バッド開口部分のパッドメタルの少なくとも下全面に形成された複数の配線メタルは互いに同一の電位に設定される。

(もっと読む)

回路設計支援装置、回路設計支援方法および半導体集積回路

【課題】配線の遅延特性のばらつきを抑制すること。

【解決手段】回路設計支援装置1は、設定部1aと生成部1bとを有している。設定部1aは、半導体集積回路モデル2の層2a、2bそれぞれに、積層方向および面方向に隣接するユニット3の配線方向が互いに異なる方向に配線が生成される複数の矩形のユニット3を設定する。生成部1bは、ユニット3の境界で異なる層のユニット3に跨る配線を生成する。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化されても高精度を維持できるキャパシタを提供する。

【解決手段】キャパシタは、平面上に交互に配列した、直線状で第1の長さを有し第1の方向に延在する第1の電極パターンと、直線状で前記第1の長さより短い第2の長さを有し、前記第1の方向に延在する第2の電極パタ―ンと、前記第1の電極パターンに第1の電圧を、第1のビアプラグを介して供給する第1の配線パタ―ンと、前記第2の電極パターンに第2の電圧を、第2のビアプラグを介して供給する第2の配線パタ―ンと、を備え、前記第1および第2の電極パターンをそれぞれの前記第1の方向で比較した場合、前記第1の電極パターンの第1の端部が、前記第1の端部に対応する前記第2の電極パターンの第2の端部よりも突出しており、前記第1の電極パターンの前記第1の端部に対向する第3の端部が、前記第3の端部に対応する前記第2の電極パターンの第4の端部よりも突出している。

(もっと読む)

回路レイアウト設計システム、リーク対策セル、回路レイアウト設計方法及びプログラム

【課題】正規回路のタイミングを変えずに、未使用セル群の全てのセルのダイナミック電流及びチャンネルリーク電流を削減することができる回路レイアウト設計システムを提供する。

【解決手段】本発明の回路レイアウト設計システムは、レイアウトデータから、出力端子がオープン状態の未使用インバーターセルを検出する出力オープンセル検出部と、オープンセル検出部が検出した未使用インバーターセルの出力オープンセル情報を、出力オープンセル情報ファイルに格納する出力オープンセル情報抽出部と、レイアウトデータから、未使用インバーターセルを削除する出力オープンセル削除部と、出力オープンセル情報のセル名を、リーク対策セルに対応するセル名に変換した置換情報ファイルに格納するセル名変換部と、置換情報ファイルを参照して、レイアウトデータの未使用インバーターセルをリーク対策セルに置換する出力オープンセル置換部とを備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体集積回路および電源配線方法

【課題】信号配線リソースを確保しながら、チップ中心部のIRドロップを少なくすることのできる半導体集積回路および電源配線方法を提供する。

【解決手段】実施形態の半導体集積回路は、チップ内に等間隔で配線される下層電源配線1と直交する方向に所定の間隔で配線される上層電源配線が、下層電源配線との接続用のビア3が配線中央部にのみ配置された上層電源配線2Aと、配線中央部を除く領域に上層電源配線2Aへの配置個数よりも多数のビア3が配置された上層電源配線2Bとの対により構成され、上層電源配線2Aの上層電源配線2Bに対する配線幅の比が、配線中央部を除く領域では、上層電源配線2Aの上層電源配線2Bに対する供給電流比の逆数であり、配線中央部では、供給電流比の逆数よりも大きい。

(もっと読む)

81 - 100 / 1,033

[ Back to top ]