Fターム[5F064EE27]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 配線パターン (7,249) | 多層配線 (2,699) | コンタクト手段 (1,033)

Fターム[5F064EE27]に分類される特許

61 - 80 / 1,033

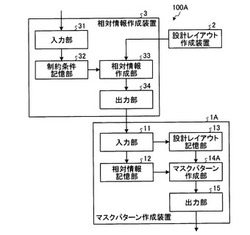

パターン作成方法および半導体装置の製造方法

【課題】高歩留まり且つ低コストで半導体装置を製造することができるパターン作成方法を提供すること。

【解決手段】実施形態によれば、パターン作成方法が提供される。パターン作成方法では、設計パターンに応じた基板上パターンを形成できるよう前記基板上パターンに応じたマスクパターンを作成する際に、前記設計パターン間が満たす必要のある相対関係に基づいて、前記設計パターン間に対応するマスクパターン間が前記相対関係を満たすよう前記マスクパターンを作成する。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体装置の設計支援装置、設計支援プログラム及びレイアウト情報生成方法

【課題】従来の設計支援装置により生成したインダクタは、周囲の回路の影響により特性ずれが生じる問題があった。

【解決手段】本発明の設計支援装置は、生成対象のインダクタに接続される接続対象回路領域の第1、第2の接続端子の位置情報を回路設計情報から生成されるフロアプラン結果から得て、インダクタを他の回路と接続する第3、第4の接続端子を、第1の接続端子と第3の接続端子との間及び第2の接続端子と第4の接続端子との間が最短の配線によって接続可能な位置に設定する端子位置設定部10と、第3、第4の接続端子の位置を基準としてインダクタの配線パターンを生成し、当該配線パターンに基づきインダクタのレイアウト情報を生成するパターン生成部13と、を有する。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

信頼性を改良するための導電性層間のビア

【課題】ビアの信頼性を改良するための技術を提供する。

【解決手段】別の半導体デバイスが、複数の導電性配線(12−20)を含む第1層(21)および第2層(33)を含み、複数の非機能的ビアパッド(34)が、第2層または第1層と第2層との間に含まれる。複数のダングリングビア(40)は、第1層の特定の領域内に含まれる。ダングリングビアは、第1層の1つまたは複数の配線をビアパッドの対応する一つに接続する。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体集積回路

【課題】製造コストを増大させずに、半導体集積回路の電源配線、接地配線の電圧降下を減少させる。

【解決手段】半導体チップ1上の第1の方向に延びる電源配線12Aが配置され、半導体チップ1上の第2の方向に延びると共に、第2の方向から第1の方向に屈曲し、電源配線12Aの一部と重畳する屈曲部24Aを有する電源引き出し配線22Aが配置されている。また、第1の方向に延びる接地配線12Bが配置され、第2の方向に延びると共に、第2の方向から、第1の方向とは逆方向の第3の方向に屈曲し、接地配線12Bの一部と重畳する屈曲部24Bを有する接地引き出し配線22Bが配置されている。電源引き出し配線22Aと接地引き出し配線22Bを覆う第1の層間絶縁膜13の中には、電源配線12Aと屈曲部24Aを接続する電源配線ビアコンタクト14Aと、接地配線12Bと屈曲部24Bを接続する接地配線ビアコンタクト14Bが配置されている。

(もっと読む)

半導体装置

【課題】電源遮断がされる領域同士の場合であっても生じる、電源遮断移行時および復帰時の貫通電流の問題を解決しつつアイソレーション回路を不要とする半導体装置を提供する。

【解決手段】半導体装置は、第1の電源線601と、第1のスイッチ605を介して第1の電源線に接続される第2の電源線101、および第2の電源線に接続されるマクロセルコア508を有するマクロセルと、第2のスイッチ603を介して第1の電源線に接続される第3の電源線602と、第3の電源線に接続され、マクロセルコアの入力または出力の少なくともいずれかに接続される回路ブロック501とを備え、第2の電源線と第3の電源線とが接続される。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】電位ドロップに起因するセルの動作不良を防止すること。

【解決手段】本発明に係る半導体集積回路は、チップ1上に配置された電源パッド2aと、電源配線構造10を介して電源パッド2aに接続された回路群21,22とを備える。その電源配線構造10は、異なる配線層に形成され複数の交差点IS1,IS2においてオーバーラップする複数の第1電源配線11及び複数の第2電源配線12と、それら複数の第1電源配線11と複数の第2電源配線12を接続するビア13とを有する。上記回路群は、第1領域R1に配置された機能ブロック21を含む。ビア13は、第1領域R1と電源パッド2aの間の第2領域R2における複数の交差点IS2の一部に配置されていない。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

半導体集積回路

【課題】内側のセル列と外側のセル列とでセルの形状が同じ場合において、内側のセル列におけるセルの配列ピッチを外側のセル列におけるセルの配列ピッチより大きくしなくても外側のセル列のセルに接続される配線のための領域を確保することができる。

【解決手段】半導体集積回路は、半導体チップの外周11に沿って配置される複数の第1セル40と、複数の第1セル40の内側で外周11に沿って配置される複数の第2セル40とを具備する。複数の第1セル40及び複数の第2セル40は同一の長方形形状に形成される。複数の第1セル40のそれぞれの長辺4aは外周11に平行である。複数の第2セル40のそれぞれの長辺4aは外周11に垂直である。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置

【課題】2個のビアを用いた配線接続構造を、ホットスポットが生じにくい構造によって実現する。

【解決手段】第1配線層において第1方向に延びる第1配線11と、第1配線層の上層または下層の配線層に形成された接続対象配線30とを電気的に接続するために、第1および第2のビア21,22が設けられている。そして、第1配線11の第2端部11bから、第1方向と直交する第2方向に第3配線13が延びており、さらに第3配線13から、第1方向において第1配線11と反対の向きに第4配線14が延びている。すなわち、第1、第3、第4配線11,13,14によってクランク状の配線が形成されている。そして、第3配線13の配線幅W3は、第1配線11における端部11a,11b間の部分の配線幅W1以上である。

(もっと読む)

配線削減方法及び回路生成装置

【課題】モジュール間の配線を自動的に削減する。

【解決手段】モジュール11A及び11Bの間に接続された配線に関する情報を含む仮配置/仮配線情報33に基づき、モジュール11A及び11Bの間に接続された配線の本数を抽出し、抽出された配線の本数と、予め設定された、配線の本数に対する閾値を少なくとも含む閾値情報34とを比較し、比較の結果、配線の本数が閾値を超えた場合に、モジュール11A及び11Bのうち、送信側のモジュール11Aに、パラレル信号をシリアル信号に変換するパラレルシリアル変換回路13を挿入するとともに、受信側のモジュール11Bに、シリアル信号をパラレル信号に変換するシリアルパラレル変換回路14を挿入し、モジュール11A及び11Bの間の接続をパラレル接続からシリアル接続に変更する。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置では、コンデンサの容量値が配置場所で変化するため、容量値の見積もりが煩雑になるという問題を解決する。

【解決手段】内部電源と、該内部電源に電源を供給する補償容量部を有する半導体装置の補償容量部のレイアウト配置の際に、補償容量部を構成する領域に拡散層の矩形領域を配置する。また、該拡散層の矩形領域の各辺に対し、各辺の中心が直行する箇所に矩形開口部を設ける。また、該拡散層の矩形領域の中心線近傍に沿ってゲート電極を直行するように形成する。また、該拡散層の該矩形領域の四隅に上層の金属層と接続するためのコンタクトを形成する。また、該ゲート電極と該拡散層の矩形開口部の重なる箇所にゲート電極と上層の金属層を接続するコンタクトを形成する。また、該ゲート電極が直行する箇所で容量を形成する。また、補償容量の単位セルを構成する。

(もっと読む)

チャージアップダメージの検証方法および検証装置

【課題】 配線と非配線とを分けて扱い、マクロ等にも半導体集積回路全体にも適用できるアンテナルールを用いるチャージアップダメージの検証方法等を提供できる。

【解決手段】 配線層毎のアンテナ比の上限値を、注目配線層の階層数と総配線層数とに基づいて設定する第1のステップS10、半導体集積回路のレイアウトデータに基づいて、配線層毎に所与のゲートにチャージアップダメージを与えるノードの面積を演算し、下位の配線層に含まれる同一のノードの面積との積算値を求める第2のステップS20、半導体集積回路のモジュール毎に、注目モジュールに含まれる所与のゲートにチャージアップダメージを与えるノードについて、注目モジュールの最上位配線層までの面積の積算値と所与のゲートの面積とに基づいてアンテナ比を求め、注目モジュールの最上位配線層におけるアンテナ比の上限値と比較する第3のステップS30を含む。

(もっと読む)

半導体集積回路の製造方法

【課題】短波長リソグラフィ装置において、広いフィールドサイズと高い解像力との両立が困難であった。

【解決手段】半導体集積回路1は、基板上の領域11(第1の領域)に設けられた第1の配線と、基板上の領域12(第2の領域)に設けられた第2の配線と、を備えている。領域12は、領域11を取り囲む領域である。第1の配線の配線幅の最小設計寸法は、第2の配線の配線幅の最小設計寸法よりも小さい。これにより、短波長リソグラフィにおいて充分な光強度を得ることが可能となる。

(もっと読む)

61 - 80 / 1,033

[ Back to top ]