Fターム[5F083BS00]の内容

半導体メモリ (164,393) | SRAM (3,190)

Fターム[5F083BS00]の下位に属するFターム

転送トランジスタ (757)

駆動トランジスタ (792)

負荷素子 (1,002)

局所配線 (248)

MOS以外の素子からなるもの(バイポーラ) (34)

セルを構成するトランジスタの数が4又は6個以外 (118)

Fターム[5F083BS00]に分類される特許

101 - 120 / 239

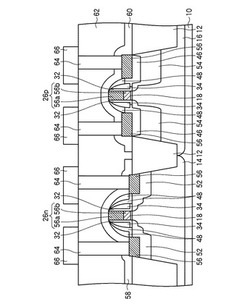

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

選択的プリチャージを使用したメモリ読取り安定性の改善

メモリデバイスは、ビットセル(34)にアクセスする前にビット線電圧を低減するために、選択的プリチャージおよび電荷共有を利用する。ビット線電圧の低減は、ビット線の異なるセクション(31、33)を異なる電圧(たとえば、供給電圧および接地)にプリチャージし、これらのセクション間で電荷共有を使用することによって達成される。読取り安定性は、ビット線電圧の低減の結果として改善される。ビット線セクション間の相対容量差(B2−C2)により、電荷共有後のビット線電圧を決定する。したがって、メモリデバイスはプロセス変動または温度変動に耐性がある。ビット線電圧は、供給電圧または接地にプリチャージされるセクションを選択することによって、設計において制御できる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】駆動能力を高めることができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置500aにおいては、基板10上に、ゲート酸化膜31およびポリシリコン層30を順次積層させたゲート構造が配置されている。ゲート構造の側面に沿って酸化膜40が配置され、酸化膜40の側面および基板10の上面に沿って酸化膜50が配置されている。酸化膜40,50からなるサイドウォール酸化膜において、ゲート構造の側面に沿った第1の層の厚みの最小値は、基板10の上面に沿った第2の層の厚みより小さい。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造技術において、同一基板上に金属シリサイド膜厚の異なる領域を作り分ける。

【解決手段】シリコン基板1の主面f1の第1領域R1に第1トランジスタQ1を、同第2領域R2に第2トランジスタQ2を形成する。その後、主面f1に保護酸化膜PT1を形成し、第1ドライエッチングDE1を施すことで、第1領域R1および第2領域R2を覆う保護酸化膜PT1を除去する。その後、第1ドライエッチングDE1よりも低い高周波パワーで、かつ、炭素、水素およびフッ素の化合物を含まないガスを用いた第2ドライエッチングDE2を、第2領域R2に対して施す。その後、シリコン基板1の主面f1上に金属膜M1を堆積し、熱処理を施すことで、金属シリサイド膜scを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ配線部の開口工程において、ヒューズ配線にダメージを与えて誤切断してしまうことを防ぐ。

【解決手段】ヒューズ配線6上の開口部17下にて、SiCN膜からなる保護膜11とプラズマCVD法によって成膜された窒化シリコン膜または酸化シリコン膜からなる保護膜18とが積層された構造を形成することにより、ヒューズ配線6上のシード膜23およびバリア導電膜22をウエットエッチングする際の洗浄液のヒューズ配線6への浸入を保護膜18にて防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】埋め込み酸化膜にディボットが発生することを防ぎ、トランジスタのしきい値電圧をメモリセル領域外とメモリセル領域の両方において所望の値に調整する。

【解決手段】メモリセル領域外3に対応する第1領域とメモリセル領域4に対応する第2領域を含むシリコン基板10上に窒化膜30を形成し、隣り合う2つの溝41を第1領域に形成し、隣り合う2つの溝42を第2領域に形成する。溝41、42の幅W41、W42が広がるように窒化膜30を後退させる。このとき、第1溝41に挟まれた第1部分11上の窒化膜30を残し、第2溝42に挟まれた第2部分12上の窒化膜30を除去する。埋め込み酸化膜50で溝41、42を埋め、窒化膜30をストッパーとして用いて埋め込み酸化膜50を研磨し、窒化膜30を除去する。不純物を第1部分11に注入し、第1部分11及び第2部分12上にゲート電極71、72を形成し、不純物を第2部分12に注入する。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路のチップサイズを低減する。

【解決手段】 入出力データを伝達する複数の入出力端子と、入出力データのうち互いに異なる番号のビットが割り当てられ、互いに異なるアドレスが割り当てられた複数のメモリセルアレイ領域とを備えている。ビット線スイッチは、各メモリセルアレイ領域のメモリセルにそれぞれ接続される複数のビット線を、メモリセルアレイ領域に形成された共有ビット線にそれぞれ接続する。センスアンプは、共有ビット線に接続され、前記ビット線スイッチを介して伝達される前記ビット線のデータを増幅する。センスアンプを、互いに異なるビットの入出力データに対して共有させることで、センスアンプの数を減らすことができ、チップサイズを低減できる。

(もっと読む)

半導体装置の製造方法

【課題】微細なパターンの配線分離を行うことができる半導体装置の製造方法を提供すること。

【解決手段】基板に素子分離領域を形成し第1及び第2の拡散領域に分ける工程と、前記基板上に被加工対象膜を形成する工程と、前記被加工対象膜上にハードマスク層と第1レジスト層を形成する工程と、前記第1レジスト層に第1パターンを形成する工程と、前記第1パターンをマスクとして前記ハードマスク層をエッチングする工程と、前記ハードマスク層上に第2レジスト層を形成する工程と、前記第2レジスト層に前記第1パターンを分離する第1スペース幅を有する第2パターンを形成する工程と、前記第2レジスト層に形成された前記第2パターンをマスクとして寸法変換エッチングを行うことにより前記ハードマスク層に第1スペース幅から縮小された第2スペース幅を有する第3パターンを形成する工程と、前記ハードマスク層に形成された第3パターンを用いて前記被加工対象膜をエッチングする工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

エミュレートされるコンビネーションメモリデバイス

【課題】集積回路メモリデバイス、および、単一の集積回路メモリデバイス内における複数のメモリタイプへのアクセスを提供する。

【解決手段】メモリデバイスは、エミュレートされる第1のメモリ領域およびエミュレートされる第2のメモリ領域を有する不揮発性メモリアレイと、インターフェースを有するコントローラとを備えている。メモリデバイスは、エミュレートされる第1のメモリタイプ、およびエミュレートされる第2のメモリタイプをエミュレートするように構成されている。メモリデバイスはさらに、メモリデバイスがエミュレートされる第1のメモリタイプをエミュレートする時にエミュレートされる第1のメモリ領域内にデータを記憶するように構成されており、また、メモリデバイスがエミュレートされる第2のメモリタイプをエミュレートする時にエミュレートされる第2のメモリ領域内にデータを記憶するように構成されている。

(もっと読む)

半導体装置

【課題】ビアホールの位置が大きくシフトした場合でも、層間絶縁膜に形成されるボイドとの接触を確実に防止して、高い信頼性および高い歩留まりを確保できる半導体装置を提供する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜の下側に配置された下側配線層と、層間絶縁膜の上側に配置された上側配線層と、層間絶縁膜を貫通して、下側配線層に属する配線と上側配線層に属する配線を電気接続するためのビアホールとを備える。下側配線層において、所定の方向に沿って延びる複数の配線ラインと、少なくとも2つの配線ラインの部分的連結によって形成され、ビアホールと接触するためのコンタクト領域とが設けられる。互いに隣接した配線ライン間に位置する層間絶縁膜には、ボイドが存在しており、一方、コンタクト領域におけるビアホールの接触部分と、コンタクト領域に隣接する配線ラインとの間に位置する層間絶縁膜にはボイドが存在していない。

(もっと読む)

半導体装置

【課題】配線層にスイッチ素子を有するプログラム可能な半導体装置の提供。

【解決手段】第1の配線層101の配線と第2の配線層102の配線を接続するビア103の内部、ビアの第1の配線との接触部、第2の配線との接触部のうちの少なくとも1つに、電解質材料104等導電率が可変の部材が配設され、ビア103は、第1の配線との接触部を第1の端子、第2の配線との接触部を第2の端子とする導電率が可変型のスイッチ素子又は可変抵抗素子として用いられ、スイッチ素子の導電率を変えることで、第1の端子と第2の端子との接触部との接続状態を、短絡、開放、又はその中間状態に可変に設定自在とされる。金属イオンの酸化還元反応によって、第1の電極と第2の電極間の導電率が変化する2端子スイッチ素子を備え、前記第1の電極に接続された逆極性の第1、第2のトランジスタと、第2の電極に接続された逆極性の第3、第4のトランジスタを備えている。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】周辺トランジスタの駆動特性の劣化を抑制できる不揮発性半導体メモリを提供する。

【解決手段】不揮発性半導体メモリは、第1の領域を取り囲む有機物を含む第1の素子分離絶縁膜9と、第1の領域内に配置されるメモリセルと、第2の領域を取り囲む有機物を含む第2の素子分離絶縁膜9と、第2の領域内に配置される周辺トランジスタHVTrと、第2の素子分離絶縁膜9の側面に沿って、半導体基板1内に設けられる不純物層7と、素子分離絶縁膜9の底面に沿って、p型の第1の不純物層8とを備える。素子分離絶縁膜9の側面に沿って不純物層7を設けることで、有機物に起因する固定電荷トラップの影響を緩和でき、不揮発性半導体メモリに用いられる周辺トランジスタ、例えばイントリンシック領域内に設けられるnチャネル型の高耐圧系MISトランジスタの逆ナローチャネル効果を抑制できる。

(もっと読む)

半導体記憶装置

【課題】配線ピッチが微細化した場合などでも読み出し電圧を確保する。

【解決手段】サブビット線SBL00〜SBLn3等は、第1メタル(第1金属配線層)で形成されている。一方、メインビット線は、第2、第3メタル(第2、第3金属配線層)に分散して形成されている。これにより、メインビット線のカップリング容量やオーバラップ容量が小さく抑えられ、カップリングノイズの影響も低減される。

(もっと読む)

メモリの動的電圧調整

集積回路(10)上のメモリ(14)のための電力供給電圧は、メモリを作動する間、動的に調整される。メモリを作動することは、供給電圧(VDD1)でメモリに給電することを含む。メモリの作動中、集積回路のテストメモリ(16)は並行して電力を供給される。テストメモリおよびメモリは、各々第1のビットセル構成タイプのビットセルを含む。テストメモリのテストに基づいてメモリを作動させながら、供給電圧の電圧レベルが、調整される(30)。電圧レベルが、メモリの失敗した作動を保証しないだけでなく、供給電圧を正確に最小化した値とみなすように、外部の変化によって調整される。システム及び方法は、いかなる種類ものメモリでも実装されうる。メモリ(14)およびテストメモリ(16)は、分離されるか、または、集積回路上に散在して物理的に実装されうる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】共通の構造を有していながら端子の配列が面対称の関係にある2つの半導体チップを有する半導体チップ及び半導体装置並びにこれらの製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】第1の半導体チップ100の第1の端子T1の位置と、第2の半導体チップ200の第2の端子T2の位置とは、面対称の関係にある。第1の半導体チップ100の第1のバッファ回路C1,C2と、第2の半導体チップ200の第2のバッファ回路C1,C2とは、少なくとも設計上同一である。第1及び第2の内部回路(デコーダ11、制御回路21等)は、少なくとも設計上同一である。配線55,61は異なるパターンで形成されてなる。

(もっと読む)

自己組織化材料を使用するピッチマルチプリケーション

ブロック共重合体などの自己組織化材料は、ピッチマルチプリケーションのためのマンドリル(162)として使用される。共重合体は、基板(110)上に堆積され、所望のパターンへと自己組織化を促される。ブロック共重合体を形成するブロックのうちの一つ(164)は、選択的に除去される。残っているブロックは、ピッチマルチプリケーションのためのマンドリル(162)として使用される。スペーサ材料は、ブロック(162)上にブランケット堆積される。スペーサ材料は、マンドリル(162)の側壁上にスペーサを形成するために、スペーサエッチングに暴露される。マンドリル(162)は、独立したスペーサを残すために選択的に除去される。スペーサは、下部基板(110)内にパターンを画定するために、ピッチ増倍化マスク機構として使用されうる。  (もっと読む)

(もっと読む)

ゲート電極下に金属シリサイドのパイプを有する電気ヒューズ

【課題】 信頼性が向上しているとともに比較的低い電圧でプログラムされることが可能な電気ヒューズを提供する。

【解決手段】 電気ヒューズは、半導体基板と、導電性または一部導電性のポリシリコンを具備するゲートと、を具備する。半導体基板はゲートの近くにおいてアモルファス化されたパイプ領域を具備するとともにパイプ領域に隣接する第1、第2電極領域を具備する。電気ヒューズは、第1、第2電極領域内の半導体基板上の金属シリサイド層をさらに具備する。金属シリサイドは、ニッケル・シリサイド、コバルト・シリサイド、チタン・シリサイド、パラジウム・シリサイド、プラチナ・シリサイド、エルビウム・シリサイド、およびこれらの組合せからなる群から選択される。

(もっと読む)

半導体装置及びその製造方法

【課題】特性ばらつきが低減され、且つマスク枚数を増やす事なく製造可能なトランジスタを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板1上に形成された第1導電型のウエル3と、ウエル3上に形成された第1のトランジスタ、および第2のトランジスタを備えている。第1のトランジスタは、第1導電型の不純物を含む第1のポケット領域9a、第2導電型の不純物を含む第1のソースおよびドレイン領域11aを有し、第2のトランジスタは、第1導電型の不純物を含む第2のポケット領域9b、第2導電型の不純物を含む第2のソース領域および第2のドレイン領域を有し、アナログ機能を実行する。ソース側及びドレイン側の第2のポケット領域9bに含まれる第1導電型の不純物の濃度は、第1のポケット領域9aに含まれる第1導電型の不純物の濃度よりも低い。

(もっと読む)

半導体装置及びその形成方法

【課題】半導体装置及びその形成方法を提供する。

【解決手段】セルゲートパターン及び周辺ゲートパターン周辺に互いに異なる絶縁パターンをそれぞれ配置してセルゲートパターン及び周辺ゲートパターン周辺に互いに異なる熱処理負担(Heat Budget)をそれぞれ与えるための方策を提供する。そのために、セルアレイ領域及び周辺回路領域を有する半導体基板を準備する。セルアレイ領域に第1及び第2セルゲートパターンが配置される。周辺回路領域に位置して第2セルゲートパターンに隣り合う周辺ゲートパターンが形成される。第1及び第2セルゲートパターン周辺に埋め込み絶縁パターンが配置される。周辺ゲートパターンの周辺に平坦化絶縁パターンが配置される。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】デュアルダマシン(Dual-Damascene)法を用いた多層Cu配線の形成工程を簡略化する。

【解決手段】層間絶縁膜45上に形成したフォトレジスト膜51をマスクにして層間絶縁膜45をドライエッチングし、層間絶縁膜45の中途部に形成したストッパ膜46の表面でエッチングを停止することによって配線溝52、53を形成する。ここで、ストッパ膜46を光反射率の低いSiCN膜によって構成し、フォトレジスト膜51を露光する際の反射防止膜として機能させることにより、フォトレジスト膜51の下層に反射防止膜を形成する工程が不要となる。

(もっと読む)

101 - 120 / 239

[ Back to top ]