Fターム[5F083BS00]の内容

半導体メモリ (164,393) | SRAM (3,190)

Fターム[5F083BS00]の下位に属するFターム

転送トランジスタ (757)

駆動トランジスタ (792)

負荷素子 (1,002)

局所配線 (248)

MOS以外の素子からなるもの(バイポーラ) (34)

セルを構成するトランジスタの数が4又は6個以外 (118)

Fターム[5F083BS00]に分類される特許

121 - 140 / 239

ビット線コンタクトプラグを形成する方法及びトランジスタ構造

【課題】ビット線コンタクト材料膜を直接にエッチングしてビット線コンタクトプラグを形成する方法を提供する。

【解決手段】方法は、ゲート構造と、基板内にありゲート構造の両側に隣接するソース/ドレインを備えるトランジスタを含む基板を設ける段階、基板の上に導電膜を形成し、導電膜の上にビット線コンタクト材料膜を形成し、ビット線コンタクト材料膜にハードマスク膜を形成する段階、導電膜をエッチングストップ膜として用い第一エッチング工程を行い、ハードマスク膜とビット線コンタクト材料膜をエッチングし、ソース/ドレインの上にビット線コンタクトプラグを形成する段階からなる。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】デュアルダマシン(Dual-Damascene)法を用いた多層Cu配線の形成工程を簡略化する。

【解決手段】層間絶縁膜45上に形成したフォトレジスト膜51をマスクにして層間絶縁膜45をドライエッチングし、層間絶縁膜45の中途部に形成したストッパ膜46の表面でエッチングを停止することによって配線溝52、53を形成する。ここで、ストッパ膜46を光反射率の低いSiCN膜によって構成し、フォトレジスト膜51を露光する際の反射防止膜として機能させることにより、フォトレジスト膜51の下層に反射防止膜を形成する工程が不要となる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】厚さが異なる2種類以上のゲート絶縁膜を有する半導体集積回路装置の信頼性を向上させることのできる技術を提供する。

【解決手段】半導体基板1の表面に形成された酸化シリコン膜6の上層に酸化シリコン膜7を形成し、次いで厚いゲート絶縁膜を形成する領域Aを覆ったフォトレジストパターン8をマスクとして、薄いゲート絶縁膜を形成する領域Bの酸化シリコン膜6,7を除去した後、フォトレジストパターン8および酸化シリコン膜7を除去し、続いて熱酸化処理を半導体基板1に施すことによって、厚さの異なるゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】2層ゲート構造と1層ゲート構造を有する半導体記憶装置において1層ゲート構造を有する回路素子のゲート電極と基板間の電気的短絡を防止する。

【解決手段】本発明は、1層ゲート構造を有する選択ゲートトランジスタ及びMOSトランジスタの下層ゲート電極層23b、23cの膜厚をメモリセルトランジスタの浮遊ゲート電極層23aの膜厚より厚くすることにより、第2電極間絶縁層24b、24cに開口部28b、28cを形成する際のエッチングにより下層ゲート電極層23b、23cを貫通しゲート絶縁層22b、22cの上面が露出されることを防止する。従って、後の下層ゲート電極層23b、23cの露出表面に形成された自然酸化膜を除去する際にゲート絶縁層22b、22cが同時に除去されることがなく、選択ゲートトランジスタ及びMOSトランジスタのゲート電極SG、TGと半導体基板21との電気的ショートを防止することができる。

(もっと読む)

三次元半導体デバイスの製造方法、基板生産物の製造方法、基板生産物、及び三次元半導体デバイス

【課題】金属からなる層間配線を容易に形成できる三次元半導体デバイスの製造方法、基板生産物の製造方法、基板生産物、及び三次元半導体デバイスを提供する。

【解決手段】この製造方法は、シリコン基板80の表面80aに有底の穴82を形成する穴形成工程と、犠牲材料85により穴82を埋め込む埋込工程と、集積回路層90をシリコン基板80の表面80aに形成する集積回路形成工程と、シリコン基板80の裏面80bよりシリコン基板80を薄化することにより、穴82を貫通させると共にシリコン基板80の裏面80bから犠牲材料85の一部を露出させる薄化工程と、犠牲材料85を除去して金属材料を埋め込むことにより層間配線を形成する配線形成工程と、シリコン基板80を他の基板上に積み重ね、集積回路層90の回路と他の基板上の回路とを層間配線を介して電気的に接続する積層工程とを備える。

(もっと読む)

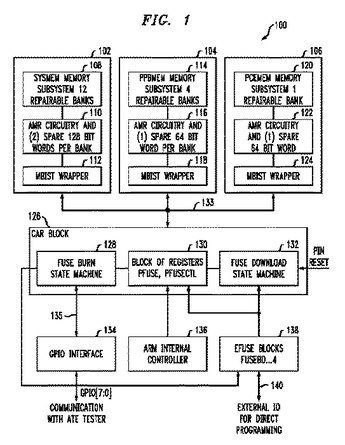

ヒューズ焼付け状態機械及びヒューズダウンロード状態機械に基づく内蔵メモリ修理方法

内蔵メモリ内の1以上の不良を修理するためのメモリ修理回路は少なくとも1つのヒューズレジスタ及び当該ヒューズレジスタに結合された状態機械回路を含む。状態機械回路は、(i)内蔵メモリ内の1以上の不良に関するステータス情報を受信し、(ii)ステータス情報に基づいてメモリが修理可能かを判断し、(iii)メモリが修理可能であるとみなされるときは、メモリの不良メモリセルに対応するアドレスを記憶し、(iv)メモリ修理回路に供給された電圧源を用いて、不良メモリセルに対応するアドレスをヒューズレジスタに焼き付け、及び(v)不良メモリセルに対応するアドレスがヒューズレジスタに焼き付けられたことを確認するように動作する第1の状態機械を実装する状態機械回路を備える。状態機械回路がさらに、(i)少なくとも1つのヒューズレジスタに記憶された情報を内蔵メモリに関連する少なくとも1つの修理レジスタにダウンロードし、及び(ii)アドレスが内蔵メモリ内の不良メモリ部分に対応する回路で受信されると、不良メモリ部分へのアクセスを少なくとも1つの修理レジスタに再ルーティングするように動作する第2の状態機械を実装する。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】外部から局所的に圧力がかかっても破損しにくい半導体装置を提供する。また、外部からの局所的押圧による非破壊の信頼性が高い半導体装置を歩留まり高く作製する方法を提供する。

【解決手段】単結晶半導体領域を用いて形成された半導体素子を有する素子基板上に、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体を設け、加熱圧着することにより、有機化合物または無機化合物の高強度繊維に有機樹脂が含浸された構造体及び素子基板が固着された半導体装置を作製する。

(もっと読む)

半導体構造の製造方法

【課題】積層メモリ・ダイを利用する半導体構造とその構造を形成する方法を提供する。

【解決手段】半導体構造は、第1の半導体ダイD1と、前記第1の半導体ダイと同一の第2の半導体ダイD2を有している。第1の半導体ダイは、第1の識別回路IDと、第1の半導体ダイの表面に、第1の複数個数の入出力パッドPIO1〜PIOnを有している。第2の半導体ダイは、第2の識別回路を有しており、第1および第2の識別回路は、互に異なるプログラムを書き込まれている。第2の半導体ダイは、また、第2の半導体ダイ表面において第2の複数個数の入出力パッドを有している。第1の複数個数の入出力パッドは、各々、垂直方向に一直線上に配列されており、各第2の複数個数の入出力パッドの1個に接続されている。第2の半導体ダイは、第1の半導体ダイに対して垂直方向に一直線上に配列され、第1の半導体ダイに固着されている。

(もっと読む)

再構成可能回路およびそのプログラミング方法

【課題】面積、消費電力、待ち時間が減少され、かつ再構成可能な集積回路を提供する。

【解決手段】再構成可能回路は、複数のロジックブロック(1)と、前記複数のロジックブロック(1)の間を接続する複数の配線(5,6)と、前記複数の配線(5,6)の間に選択的に挿入され、1kΩ以下のオン抵抗を有する複数のスイッチブロック(2)とを具備する。

(もっと読む)

半導体集積回路装置及びそのレイアウト方法

【課題】ノイズによる誤動作を従来よりも低減すること。

【解決手段】メモリマクロ1は、複数のメモリセル3を含むメモリセルアレイ2と、メモリセル3に接続された相補デジット線対DTj、DBjと、相補デジット線対DTj、DBjに接続されたカラム系周辺回路6とを備えている。通過配線20−1〜20−Mは、メモリマクロ1上の相補デジット線対DTj、DBjに対して垂直に交差する方向に設けられる。メモリマクロ1の相補デジット線対DTj、DBjに水平な部分の長さをYとし、部分Yのうちの、メモリセルアレイ2、カラム系周辺回路6の幅に対応する長さをそれぞれYa、Ybとしたとき、Mが(Ya+Yb)/Yb以上である場合、カラム系周辺回路6上に設けられる通過配線を禁止するために、通過配線20−1〜20−Mの全てがメモリセルアレイ2上に均等に配置される。

(もっと読む)

タイミング制御用のダミービット線を有するメモリ

N本のワード線を含む1つ以上のメモリアレイブロック(10)を有するメモリを提供する。ここで、Nは1より大きい。このメモリは、該1つ以上のメモリアレイブロック(10)に結合された複数のセンスアンプ(28,29)を備える。このメモリは、M個のダミービットセル(42,43)を含む1つ以上のダミービット線(40,41)をさらに備える。ここで、MはNに等しい。このメモリは、該1つ以上のダミービット線(40,41)に結合されたタイミング回路(20)をさらに備える。タイミング回路(20)は、1つ以上のプルダウントランジスタスタック(60,61)を備え、同スタックはメモリアクセスのタイミング制御のために用いられるラッチ制御出力信号(104)を発生させるための感知回路(70)に結合されている。タイミング制御には、読取動作について複数のセンスアンプ(28,29)をイネーブルとするためのセンストリガ信号(44)を発生させること、書込動作について複数の書込ドライバ(26,27)をディスエーブルとするなど、メモリアクセスを終了させるためのローカルリセット信号(100)を発生させること、またはその両方が含まれる。  (もっと読む)

(もっと読む)

積層メモリ

【課題】 積層メモリの貫通電極は同一配置位置であり、各層は並列接続となる。そのため各層を個別にアクセスするために複数の貫通電極が必要になるという問題がある。

【解決手段】 本発明の積層メモリは、各層の階層認識情報を設定するID用貫通電極の配置位置を異ならせた第1及び第2のメモリチップを交互に積層する。このように交互に積層することで、各層の階層認識情報用の内部回路はカスケード接続となる。内部回路は各層の階層認識情報を簡単に生成することができる。これらの階層認識情報を識別することで各層の動作又は非動作が選択できる積層メモリが得られる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトライナー膜を有し、ゲート絶縁膜に水素を効果的に供給することが可能な構造を有するPMISトランジスタを備える半導体装置を提供する。

【解決手段】活性領域100上に形成されたP型MISトランジスタを有する半導体装置は、ゲート絶縁102膜と、ゲート電極103と、側壁絶縁膜112と、ソースドレイン領域107と、ゲート電極103及び側壁絶縁膜112を覆うように形成されたコンタクトライナー膜109と、層間絶縁膜110と、コンタクトプラグ111とを備える、コンタクトライナー膜109は、側壁絶縁膜112の側面と活性領域100の上面とが交わる角部近傍において、上面側から角部に向かって延びるスリット109Aを有している。

(もっと読む)

半導体記憶装置

【課題】面積を削減する階層ビット線方式を用いた半導体記憶装置を提供する。

【解決手段】各メモリセルアレイ11の列を選択する複数のローカルビット線LBLと、2つのメモリセルアレイ11ごとに1つ設けられ、かつメモリセルからローカルビット線LBLを介して転送されるデータを検知する複数のローカルセンスアンプ12と、複数のローカルセンスアンプ12に対応して設けられた複数のレプリカセル群15と、複数のレプリカセル群15にそれぞれ接続された複数のレプリカビット線RBLと、レプリカビット線RBLの電位に基づいてローカルセンスアンプ12を活性化する複数の活性回路14と、メモリセルを構成するトランジスタのウェル領域に電源を供給するためのコンタクトが配置されるコンタクト領域17とを具備する。異なるローカルセンスアンプ12に接続された2つのメモリセルアレイ11は、コンタクト領域17を挟まずに隣接している。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

情報処理方法

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】絶縁表面を有する基板10上に形成された第1の電極11と、第1の電極11の側壁部に形成されたサイドウォール絶縁層12と、第1の電極11上及びサイドウォール絶縁層12を覆って形成されたシリコン膜13と、シリコン膜13上に形成された第2の電極14と、を有し、第1の電極11又は第2の電極14は、シリコン膜13と合金化する材料で形成されているメモリ素子を複数有している。

(もっと読む)

半導体記憶装置

【課題】チップ平面上の余剰領域を削減し、チップサイズを縮小する。

【解決手段】データの入出力を行う複数のデータパッド22aは、基板20の外周の一辺の近傍に、その一辺に沿って配置され、複数のデータパッド22aに沿って、その内側にデータの入出力を行う複数のデータパッド22bが配置されている。データを出力するためのNMOS28a,28bは、データパッド22a,22bの間に配置され、データを出力するためのPMOS27a,27bは、データパッド22a,22bの近傍に、NMOS28a,28bに対向する位置に配置されている。

(もっと読む)

半導体メモリ素子の製造方法

【課題】エッチング方法を変化させてビットラインの損失を防止する半導体メモリ素子の製造方法を提供する。

【解決手段】第1の絶縁膜102上に金属配線層とエッチング停止膜112を形成する。金属配線層とエッチング停止膜112をパターニングして金属配線110を形成する。そして、第1の絶縁膜102上に第2の絶縁膜114を形成し、エッチング停止膜112が露出されるように第1のエッチングガスで第2の絶縁膜114の一部をエッチングする。続いて金属配線110が露出されるように第2のエッチングガスでエッチング停止膜112を除去する。それによって、たとえば比抵抗が低いアルミニウムを金属膜106として用い、そのアルミニウム金属膜106によるビットラインにビアホール120を連結する際、エッチングガスを変化させるだけで別途に追加膜を形成せずともアルミニウム金属膜106のエッチング損傷を抑制できる。

(もっと読む)

半導体記憶装置

【課題】行選択回路の小面積化と製造時の露光、エッチング等の影響を解消する半導体記憶装置を実現する。

【解決手段】アドレス入力に応じて所望のワード線を選択するように行アドレス信号と接続されたワード線選択回路と、疑似メモリセルのワード線に接続された疑似ワード線電位固定回路とを備え、疑似ワード線電位固定回路をワード線選択回路と同様にNANDゲートNANDR(i)(i=−1〜m+2)とインバータINVR(i)(i=−1〜m+2)で構成し、疑似ワード線電位固定回路の入力は疑似メモリセルのワード線を常に非選択となるように行アドレス信号と接続されている。これにより全てのワード線を選択駆動する回路の構成を同一とすることが可能となり、行選択回路の小面積化と製造時の露光、エッチング等の影響を解消することが可能となる。

(もっと読む)

121 - 140 / 239

[ Back to top ]