Fターム[5F083BS00]の内容

半導体メモリ (164,393) | SRAM (3,190)

Fターム[5F083BS00]の下位に属するFターム

転送トランジスタ (757)

駆動トランジスタ (792)

負荷素子 (1,002)

局所配線 (248)

MOS以外の素子からなるもの(バイポーラ) (34)

セルを構成するトランジスタの数が4又は6個以外 (118)

Fターム[5F083BS00]に分類される特許

221 - 239 / 239

半導体記憶装置

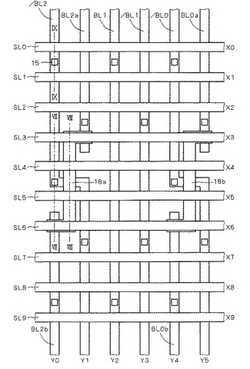

【課題】ビット線交差方式を採用して隣接ビット線間の容量を低減する効果を維持しつつも、ダミーメモリセルを無くしてメモリセルアレイの面積の増大を回避し得る半導体記憶装置を得る。

【解決手段】第2配線層内には、交差配線18a,18bとシャント配線SL0〜SL2,SL7〜SL9とが形成されている。交差領域TR3,TR4は、第X3〜X6行に属している。シャント配線SL0〜SL2,SL7〜SL9は、交差領域TR3,TR4が属さない第X0〜X2,X7〜X9行にそれぞれ属している。第4配線層内には、シャント配線SL3〜SL6が形成されている。シャント配線SL3〜SL6は、交差領域TR3,TR4が属する第X3〜X6行にそれぞれ属している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 半導体装置の配線構造の微細化に対応して、LT法での歩留まり低下を防止し、ヒューズ部構造の信頼性を確保できる半導体装置及び半導体装置の製造方法を得ることを目的とする。

【解決手段】 この発明の半導体装置は、メモリ部救済用の金属製のヒューズ配線を搭載しており、ヒューズ配線01上にSiCN膜05、ビア層間絶縁膜06、パッシベーション膜を形成後、パッシベーション膜をエッチングで除去し、ビア層間絶縁膜06をエッチバックして除去する。その結果ヒューズ配線01上にはSiCN膜05のみを備えている。

(もっと読む)

ヒューズ構造

【課題】 上層電気ヒューズの一端と下層電気ヒューズの一端にかかる電位を容易に一致させることができるヒューズ構造を得る。

【解決手段】 本発明のヒューズ構造は、上下に配置された上層電気ヒューズ及び下層電気ヒューズを有する。そして、これらの上層電気ヒューズ及び下層電気ヒューズは、電気的にバイアスを加えることで溶断することができる。さらに、上層電気ヒューズの一端と下層電気ヒューズの一端は、共通接続されている。

(もっと読む)

ワード長可変記憶装置製造方法

【課題】従来のワード長可変記憶装置では、積層収納する半導体メモリ毎にチップアドレスデータ比較回路をあらかじめ備えなければならず、汎用の半導体メモリを使用できないという問題がある。

【解決手段】本発明は、複数の半導体メモリチップを実装基板上に樹脂封止し、前記実装基板にはデータ入出力用の端子が設けられ、前記各半導体メモリチップのデータ入出力端子は前記実装基板のデータ入出力端子に別々に接続することを特徴とする、ワード長可変記憶装置製造方法に関するものである。

(もっと読む)

ピッチ増倍を使用する集積回路の製造方法

周辺回路100のアレイ102及び周辺104の異なるサイズのフィーチャーが1つのステップで基板110上にパターン化される。特に、独立に形成された2つのパターン177、230を組合せた混合パターンが、一つのマスク層160上に形成され、次に、下の基板(110)に転写される。独立に形成されたパターンのうち第1パターン177はピッチ増倍によって形成され、独立に形成されたパターンのうち第2パターン230は従来のフォトリソグラフィによって形成される。第1パターン177は、第2パターン230の形成に使用されたフォトリソグラフィ法の解像度以下のフィーチャー175を含む。これらのラインは、フォトレジスト上にパターンを形成し、そしてそのパターンを非晶質炭素層にエッチングすることによって製作される。非晶質炭素のエッチングされていない部分の幅より小さい幅を有する側壁スペーサー175は、前記非晶質炭素の側壁上に形成される。その後、非晶質炭素は除去されて、側壁スペーサー175を残してマスクパターン177を形成する。従って、スペーサー175は、フォトレジスト上にパターンを形成するために使用されたフォトリソグラフィ方法の解像度より小さいフィーチャーサイズを有するマスク177を形成する。保護物質200がスペーサー175のまわりに形成される。スペーサーは175さらに、ハードマスク210を用いることにより保護され、そして次にフォトレジスト220がハードマスク210上に形成されパターン化される。フォトレジストパターン230はハードマスク(210)を通じて保護物質200に転写される。その後、スペーサー175及び保護物質200によって作成されたパターン177、230の組合せは、下の非晶質炭素ハードマスク層160に転写される。その後、異なるサイズのフィーチャーを有する組合せパターンは下の基板110に転写される。  (もっと読む)

(もっと読む)

半導体装置

【課題】 ビット線及びワード線に対するクロストークを低減しながら上層の信号配線を配置可能とし、かつブロック配置ローテーションの制約がなくチップ上の信号配線方向に適合したレイアウト構造を有することで、デッドスペースの発生や配線乗り換えによる面積ロスを低減する。

【解決手段】 スタティックRAMのメモリセルアレイ領域10上においてワード線21,22…とビット線31a,31b…との交点を縦横2点ずつ覆うようにダミー配線パターン411,412…,421,422…を形成することで、これらダミー配線パターンの間に横方向に走る配線チャネル5a1,5a2…と、縦方向に走る配線チャネル5i1,5i2…とを格子状に形成する。いずれかの配線チャネル(例えば5a2)を通るように信号配線70を自動配置する。この信号配線70は、ワード線21,22…の上層に位置し、かつダミー配線パターンと同層のメタル配線である。

(もっと読む)

半導体装置の製造方法

【課題】深さの異なる溝に絶縁膜を埋め込んで素子分離を形成するに際して、各素子分離の半導体基板表面からの高さを均等とし、高品質の半導体装置を製造する半導体装置の製造方法を得ること。

【解決手段】半導体基板上に第1〜第3のマスク層を形成し、第3及び第2のマスク層において深さの深い第1の素子分離及び深さの浅い第2の素子分離の対応領域をエッチングし、第1のマスク層において第1の素子分離の対応領域をエッチングし、第3及び第1のマスク層をマスクとして半導体基板における第1の素子分離の形成領域をエッチングして第1の溝を形成し、第1のマスク層における第2の素子分離に対応する領域をエッチングし、第3のマスク層をマスクとして半導体基板における第1の素子分離及び第2の素子分離の形成領域をエッチングして第2の溝を形成すると共に第1の溝をさらに深堀し、第1の溝及び第2の溝に絶縁膜を埋め込み、絶縁膜を平坦化する。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置

【課題】面積当たりに占めるゲート数の割合が大きい密パターンの領域と面積当たりに占めるゲート数の割合が小さい疎パターンの領域とが混在する場合において、1つのマスクを用いて低消費電力に優れた半導体集積回路装置と高速動作に優れた半導体集積回路装置とを作り分けること。

【解決手段】図1(イ):写真製版に使用するマスクの作成時に、高速動作や低消費に効く周辺回路部領域(1)を意図的にパターンが疎(2A<B)となるように形成し、パターンを密(2A≧B)にするメモリ部領域(2)と区別する。図1(ロ):絶縁膜5のマスクエッチにおいて、O2(酸素)などのエッチング条件を変更する。これによって、パターンが密(2A≧B)になっているメモリ部領域(2)とパターンが疎(2A<B)になっている周辺回路部領域(1)とでCDシフト量が別々に変更される。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 冗長救済機能を備えた半導体記憶装置を有するロジック半導体装置において、半導体装置の高集積化に伴って生じる半導体装置の面積を増大させることなく、冗長救済を行なった後も、内部回路素子の金属配線における腐食の発生を防止する。

【解決手段】 半導体基板10上に形成された冗長救済されるべき回路素子を含む内部回路素子26と、半導体基板10上に内部回路素子26を覆うように形成された第1、第2及び第3の層間絶縁膜15、18及び21と、第3の層間絶縁膜21の上に形成された冗長救済されるべき回路素子26の冗長救済に用いられるヒューズ25とを備えている。第3の層間絶縁膜21とヒューズ25との間には、耐透水性を有する絶縁膜22が介在している。

(もっと読む)

半導体装置

【課題】本発明は、階層化されたビット線を有する半導体メモリにおいて、これらのビット線の配線レイアウトの効率化を図るとともに、全体のレイアウト面積を削減できるようにするものである。

【解決手段】たとえば、1つのカラムにおいて、グローバルビット線対GBL,GBLBには、複数のローカルビット線対LBL,LBLBが、それぞれ、選択トランスファーゲート15a,15bを介して共通に接続されている。そして、それぞれの選択トランスファーゲート15a,15bを構成する、PMOSスイッチトランジスタSPa,SPbおよびNMOSスイッチトランジスタSNa,SNbが、それぞれ、メモリセルアレイ11を挟んで反対側に配置されてなる構成となっている。

(もっと読む)

メモリ領域とロジック領域を混載する半導体装置の製造方法

【課題】 メモリ領域とロジック領域でのSTIの突き出し量のバラツキを低減するのと共に、ゲート写真製版のフォーカスマージンを向上し得る半導体装置の製造方法を得ることを目的とする。

【解決手段】 素子分離としてのSTI形成後の半導体基板において、メモリ領域のメモリセル部に対するチャネルドープ工程をゲート酸化前に行い、所定の不純物注入完了後にレジスト付きの状態にてフッ酸含有の溶液によりSTI段差を調整するためウエットエッチングを行い、メモリ領域とロジック領域のSTI突き出し量の差が同程度になるようにした。

(もっと読む)

ソフトエラー率計算方法及び計算装置

【課題】

従来の、SRAMやロジック回路等の半導体素子あるいはLSIの、α線、或いは宇宙線によるソフトエラーのエラー率計算方法では、マルチビットエラーが発生した場合、パターンが実際と異なるという問題があった。

【解決手段】

発生したイオンによる電荷が水平にイオンが走った場合、従来は、VH(High電位)側NMOSノード3に対するVL(Low電位)側NMOSノードの領域6、VH側NMOSノード3に対するVH側PMOSノードの領域5、VL側PMOSノード4に対するVH側PMOSノード5の領域、VL側PMOSノード4に対するVL側NMOSノードの領域6はエラーとは関係ないとして計算では考慮しなかった。本発明では、このHigh-Lowが問題となるノードのペアとなる領域に電荷が発生した場合、従来エラーに関係ないと見なしていた電荷によるエラー抑制効果をソフトエラーシミュレーションに組込むようにした。これにより、マルチビットエラーのパターンが実測に合うようになった。

(もっと読む)

積層型半導体メモリ装置

【課題】 3次元半導体メモリ装置において、データ転送時の充放電に必要な配線容量を減らして低消費電力化する。

【解決手段】 第1の半導体チップ上に複数積層され、バンクメモリが分割されたサブバンクが入出力ビットに対応してまとめられて配置されたメモリセルアレイチップと、前記入出力ビットの数分設けられ、前記サブバンクを対応する入出力ビットが同じとなるように前記メモリセルアレイチップをその積層方向に貫通する形態で接続するチップ間配線とを有する。

(もっと読む)

3次元半導体装置

【課題】3次元半導体装置において、信号伝送路の3次元配線容量を減らして消費電力を削減する。

【解決手段】半導体回路チップ30を複数枚積層し、この半導体回路チップ間の信号伝送のためのチップ間配線50を複数本備えた3次元半導体装置において、信号伝送時に信号伝送の経路となる1つのチップ間配線50のみを選択し、それ以外のチップ間配線50をチップ間配線50と信号線との間に設けたスイッチによって電気的に切り離す。これによって、配線の充放電に関わるチップ間配線容量を最小限にする。

(もっと読む)

半導体装置

【課題】デュアルゲート構造を有するMIS型トランジスタにおいて、デュアルゲートにおけるシリサイド部分の断線に起因する遅延の劣化を防止して、動作不良を防止できるようにする。

【解決手段】 半導体装置は、上部がシリサイド化されたゲート電極22を有するP型MOSトランジスタ100及びN型MOSトランジスタ200を備え、ゲート電極22におけるP型MOSトランジスタ100部分は、P型不純物が導入されたポリシリコンを含み、そのN型MOSトランジスタ200部分は、N型不純物が導入されたポリシリコンを含む。P型MOSトランジスタ100及びN型MOSトランジスタ200の互いのドレインは、シリサイド化されたポリシリコンを含む共有配線23により接続されている。共有配線23の線幅は、ゲート電極22の線幅よりも大きくなるように設定されている。

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

中性子変換層組み込み型半導体基板

【解決手段】シングル中性子イベントの測定を可能にするのに十分な感度のある中性子変換層を組み込んだ半導体基板。前記基板は、アクティブ半導体素子層と、ベース基板と、前記アクティブ半導体素子層と前記ベース基板との間に提供される絶縁層と、前記アクティブ半導体素子層と前記ベース基板との間に提供される中性子変換層を含む。前記中性子変換層は、前記絶縁層内に位置し、且つ同絶縁層と前記ベース基板との間、若しくは前記アクティブ半導体素子層と同絶縁層との間に位置する。前記中性子変換層と前記アクティブ半導体素子層との間、および前記中性子変換層と前記ベース基板との間の少なくとも1つの間に障壁層が提供され、前記中性子変換層中に提供される中性子変換材料の拡散を防ぐ。さらに、前記アクティブ半導体素子層に複数の溝を形成する場合がある。 (もっと読む)

半導体集積回路装置

【課題】 入力回路の簡素化と製品管理の取り扱いを簡便にしつつ、実質的な低消費電力化及び素子の微細化に適合して安定した入出力伝達特性を実現できる入力回路を備えた半導体集積回路装置を提供する。

【解決手段】 外部端子から供給される入力信号を受ける差動増幅回路に第1と第2の動作電圧を第1と第2のスイッチMOSFETを介して供給するようにし、バイアス電圧発生回路により上記入力信号が上記第1と第2の動作電圧の中心電圧付近にあるときに上記第1と第2スイッチMOSFETをオン状態にし、その入力信号が継続的に一定期間上記第1電圧又は第2電圧にあるときには、それに対応した出力信号を形成すべく上記第1又は第2スイッチMOSFETのいずれか一方をオン状態に他方をオフ状態にする制御電圧を形成し、上記第1動作電圧と第2動作電圧に対応した第1振幅の入力信号と、上記第1動作電圧と第2動作電圧の間の所定の中間電圧に対応した第2振幅の入力信号の双方の供給を可能とする。

(もっと読む)

半導体記憶装置

【課題】チップサイズを増大させることなく特性の向上を図ることができる半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、メモリセル領域50と周辺回路領域との間に配置されたセル形状の書込動作補助回路2を有し、書込動作補助回路2は、書込開始時にデジット線のディスチャージ動作を行い、書込終了時にデジット線のプリチャージ動作を行う第1の回路4と、デジット線のディスチャージ動作及びデジット線のプリチャージ動作の切替を行う第2の回路5とを有する。

(もっと読む)

221 - 239 / 239

[ Back to top ]