Fターム[5F083ER11]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | ホール注入 (502)

Fターム[5F083ER11]に分類される特許

1 - 20 / 502

半導体装置

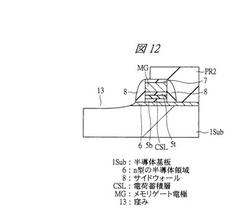

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性の均一化を図る。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に設けられた積層体と、絶縁膜と、チャネルボディと、半導体層とを備えている。前記積層体は、選択ゲートと、前記選択ゲート上に設けられた絶縁層とを有する。前記絶縁膜は、前記積層体を積層方向に貫通して形成されたホールの側壁に設けられている。前記チャネルボディは、前記ホール内における前記絶縁膜の側壁に設けられ、前記選択ゲートにおける前記絶縁層側の端部近傍で前記ホールを閉塞し、且つ前記ホールを閉塞する部分より下で空洞を囲む。前記半導体層は、前記チャネルボディが前記ホールを閉塞する部分より上の前記ホール内に、前記チャネルボディと同材料で連続して埋め込まれている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置(不揮発性メモリを有する半導体装置)の特性を向上させる。

【解決手段】本発明の半導体装置は、制御ゲート電極CGと半導体基板との間に形成された絶縁膜3と、メモリゲート電極MGと半導体基板との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成された絶縁膜5であって、その内部に電荷蓄積部を有する絶縁膜5と、を有する。この絶縁膜5は、第1膜5Aと、第1膜5A上に配置された電荷蓄積部となる第2膜5Nと、第2膜5N上に配置された第3膜5Bと、を有し、第3膜5Bは、制御ゲート電極CGとメモリゲート電極MGとの間に位置するサイドウォール膜5sと、メモリゲート電極MGと半導体基板との間に位置するデポ膜5dとを有する。かかる構成によれば、絶縁膜5の角部における距離D1を大きくすることができ、電界集中を緩和できる。

(もっと読む)

3次元不揮発性メモリ素子及びその製造方法

【課題】消去動作の際、充分な量の正孔を生成させて消去特性を確保することができる3次元不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】基板から突出されたチャンネル膜と、チャンネル膜に沿って積層された複数のメモリセルと、チャンネル膜の一側端と繋がれたソースラインと、チャンネル膜の他側端と繋がれたビットラインと、チャンネル膜の一側端とソースラインとの間に介在されて、Pタイプの不純物がドープされた第1ジャンクションと、チャンネル膜の他側端と前記ビットラインとの間に介在されて、Nタイプの不純物がドープされた第2ジャンクションと、を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】読出動作の精度を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングは、半導体基板の上方に設けられ、複数のメモリセルを含む。制御回路は、複数のメモリセルのうち、選択メモリセルに保持されたデータを読み出す読出動作を実行する。メモリストリングは、半導体層、電荷蓄積層、及び導電層を有する。半導体層は、半導体基板に対して垂直方向に延びメモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積可能とされる。導電層は、半導体層と共に電荷蓄積層を挟むよう設けられメモリセルのゲートとして機能する。制御回路は、読出動作の実行前に、選択メモリセル及び非選択メモリセルを導通状態としてメモリストリングの一端から他端へと電流を流すリフレッシュ動作を実行する。

(もっと読む)

半導体装置

【課題】MONOS型不揮発性メモリの信頼性を向上させる。

【解決手段】メモリセルは、選択ゲート6とその一方の側面に配置されたメモリゲート8とを有している。メモリゲート8は、一部が選択ゲート6の一方の側面に形成され、他部がメモリゲート8の下部に形成されたONO膜7を介して選択ゲート6およびp型ウエル2と電気的に分離されている。選択ゲート6の側面にはサイドウォール状の酸化シリコン膜12が形成されており、メモリゲートの側面にはサイドウォール状の酸化シリコン膜9と酸化シリコン膜12とが形成されている。メモリゲート8の下部に形成されたONO膜7は、酸化シリコン膜9の下部で終端し、酸化シリコン膜12の堆積時にメモリゲート8の端部近傍の酸化シリコン膜12中に低破壊耐圧領域が生じるのを防いでいる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

不揮発性半導体記憶装置

【課題】エッチング加工がし易く、データ保持の劣化を抑制する。

【解決手段】実施形態の不揮発性半導体記憶装置は、下地層と、前記下地層の上に設けられた積層体であって、それぞれ交互に積層された複数の電極層と複数の絶縁層と、前記複数の電極層と前記複数の絶縁層との間に設けられた拡散抑制層と、を有する前記積層体と、前記積層体を積層方向に貫通するホールの側壁に設けられたメモリ膜と、前記メモリ膜の内側に設けられたチャネルボディ層と、を備える。前記複数の電極層のそれぞれは、第1の不純物元素を含む第1の半導体層である。前記拡散抑制層は、前記第1の不純物元素とは異なる第2の不純物元素を含む第2の半導体層である。前記拡散抑制層は、前記第1の不純物元素の拡散を抑制する効果を有する膜である。

(もっと読む)

不揮発性半導体装置およびその製造方法

【課題】絶縁体に電荷を蓄える不揮発性メモリにおいて、データ保持特性を向上させることのできる技術を提供する。

【解決手段】メモリゲート電極MGと半導体基板1との間に介在する電荷蓄積層CSLをメモリゲート電極MGのゲート長または絶縁膜6t,6bの長さよりも短く形成して、電荷蓄積層CSLとソース領域Srmとのオーバーラップ量(Lono)を40nm未満とする。これにより、書込み状態では、書き換えを繰り返すことによって生じるソース領域Srm上の電荷蓄積層CSLに蓄積される正孔が少なくなり、電荷蓄積層CSL中に局在する電子と正孔との横方向の移動が少なくなるので、高温保持した場合のしきい値電圧の変動を小さくすることができる。また、実効チャネル長を30nm以下にすると、しきい値電圧を決定する見かけ上の正孔が少なくなり、電荷蓄積層CSL中での電子と正孔との結合が少なくなるので、室温保持した場合のしきい値電圧の変動を小さくすることができる。

(もっと読む)

半導体装置

【課題】電荷トラップを含むゲート電極と、電荷トラップを含まないゲート電極とを有する半導体装置において、両ゲート電極下のチャネル層にポテンシャルバリアが形成されないようにする。

【解決手段】基体8上に絶縁膜を介して第一のゲート電極1、第二のゲート電極2が形成され、両ゲート電極1、2を挟んで第一の拡散層5と第二の拡散層6が形成され、両拡散層5、6の間にチャネル層が形成されている。前記絶縁膜は、第一の拡散層5から第二の拡散層6の方向に第一の絶縁領域3、第二の絶縁領域4が配設された、両絶縁領域3、4のうち第二の絶縁領域4が電荷トラップを含み、第一の絶縁領域3を介して第一のゲート電極1が、第二の絶縁領域4を介して第二のゲート電極2が形成され、両ゲート電極1、2底部下に形成されるチャネル層の高さが相互に異なり、第二の拡散層6の先端部は、第二のゲート電極2直下の領域にまで到達している。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

半導体装置

【課題】消去特性と消去ディスターブ特性との双方を向上することが可能な、MONOS型メモリセルなどの半導体装置を提供する。

【解決手段】半導体基板SUBの主表面に形成される第1のゲート電極CGと、主表面上において第1のゲート電極CGと隣接するように形成された第2のゲート電極MGと、第2のゲート電極MGと半導体基板SUBとに挟まれた領域から、第1のゲート電極CGと第2のゲート電極MGとに挟まれた領域に連なるように延びる絶縁膜ONOと、第1および第2のゲート電極CG,MGの真下のチャネル領域を挟むように、主表面に形成される1対のソース/ドレイン領域NR1,NR2とを備える。上記ソース領域NR1は、第1のソース領域N11および第2のソース領域N12を含んでいる。上記第2のソース領域N12は第1のソース領域N11よりも主表面から深い領域に形成されている。上記第1のソース領域N11と第2のソース領域N12とに含まれる不純物の材質が異なっている。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数のメモリストリングのうち特定のメモリストリングに対して選択的に消去動作を実行可能な不揮発性半導体記憶装置を提供する。

【解決手段】一態様に係る不揮発性半導体記憶装置は、メモリセルアレイ、複数のメモリストリング、ドレイン側選択トランジスタ、ソース側選択トランジスタ、複数のワード線、複数のビット線、ソース線、ドレイン側選択ゲート線、ソース側選択ゲート線、及び制御回路を有する。制御回路は、選択したビット線に第1電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を実行する一方、非選択としたビット線に第2電圧を印加して当該ビット線に接続されたメモリストリングに対し消去動作を禁止する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

熱アシスト誘電体電荷トラップメモリ

【課題】

誘電体電荷トラップメモリの動作速度及び/又は耐久性を向上させる技術を提供する。

【解決手段】

メモリデバイスは、ワードライン及びビットラインを含む誘電体電荷トラップ構造メモリセルのアレイを含む。該アレイに、読み出し、プログラム及び消去の動作を制御するように構成された制御回路が結合される。コントローラは、該アレイのメモリセル内の誘電体電荷トラップ構造を熱アニールする支援回路を備えるように構成される。熱アニールのための熱を誘起するために、ワードラインドライバ及び前記ワードライン終端回路を用いて、ワードラインに電流を誘起することができる。熱アニールは、サイクルダメージからの回復のために、通常動作とインターリーブされて適用されることが可能である。また、熱アニールは、消去のようなミッション機能中に適用されることもでき、それにより該機能の性能を向上させ得る。

(もっと読む)

ダイオードストラッピングを備えた熱アシストフラッシュメモリ

【課題】フラッシュメモリの動作速度及び耐久性を向上させる技術の提供。

【解決手段】メモリが、行及び列を含むメモリセルのアレイを有している。該メモリは、アレイ内の単数又は複数のワード線上の第1の離隔位置のセットに第1のバイアス電圧を印加するとともに、単数又は複数のワード線上の第2の離隔位置のセットに第1のバイアス電圧とは異なる第2のバイアス電圧を印加する、ワード線に結合された回路部を有し、第1の離隔位置のセットにおける位置は、第2の離隔位置のセットの位置の間に介在しており、それにより、第1の離隔位置のセットにおける位置と第2の離隔位置のセットにおける位置との間に、単数又は複数のワード線の加熱をもたらす電流の流れが誘導される。

(もっと読む)

1 - 20 / 502

[ Back to top ]