Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

2,361 - 2,380 / 2,405

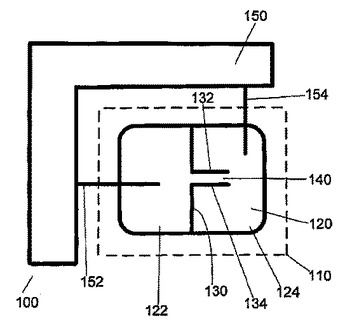

自己スイッチングメモリデバイス

メモリデバイス、及び関連する製造及び動作の方法を説明している。該メモリデバイスは、移動電荷キャリアを支持する基板(120)を具えている少なくとも1つのメモリユニットを含む。該基板表面上には絶縁部(130、132、134)が形成され、該絶縁部の両側に第1及び第2基板領域(122、124)を形成している。該第1及び第2基板領域は、絶縁部によって形成された細長チャネル(140)によって接続されている。メモリユニットは、前記第1及び第2領域間の所定の電位差でチャネルが第1及び第2領域間に第1のコンダクタンスを与える第1の状態と、前記所定の電位差でチャネルが第1及び第2領域間に第2の異なるコンダクタンスを与える第2の状態との間で切り換え可能である。メモリユニットを第1の状態に変更するため、前記メモリユニットの第1及び第2領域に第1の電位差を、そしてメモリユニットを第2の状態に変更するため第2の異なる電位差を印加するよう、書き込み回路(150)が構成されている。メモリユニットの状態を読み出すため、メモリユニットの第1及び第2領域に前記所定の電位差を印加するよう、読み出し回路(150)が構成されている。  (もっと読む)

(もっと読む)

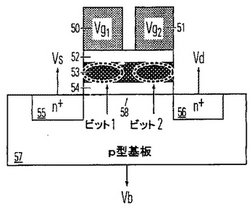

ゲート当たりトラップ位置を2つ有する電荷をトラップする不揮発性メモリおよびその動作方法

【課題】容易に製造され高密度の用途に対応する不揮発性メモリ用のメモリ技術を提供する。

【解決手段】マルチゲート型メモリセルは、半導体本体と、半導体本体上に直列に配列された複数のゲート50,51とを備える。半導体本体上の電荷蓄積構造体は、複数のゲート50,51におけるすべてまたはいくつかのゲートのそれぞれの下の2つの電荷トラップ位置を含む。ソース55およびドレイン56のバイアス電圧を、半導体本体の、直列における第1のゲート50および最後のゲート51の近くに伝える回路、ならびにゲートのバイアス電圧を複数のゲートに伝える回路が備えられる。マルチゲート型メモリセルは、直列における複数のゲート50,51の下の、連続したマルチゲートのチャネル領域58を含み、電荷蓄積位置がゲートのうちのいくつかまたはすべての間にある。

(もっと読む)

スタガ配置のメモリ・セル・アレイ

セルをアレイ中に配置する方法が開示されている。方法は、第1のアレイ中にセルを複数回(600、602、604)配置する工程を含む。セルは、また第2のアレイ中にも複数回(606、608、610)配置される。第2のアレイは、第1のアレイからオフセット距離(O2)だけ離して隣接して配置される。  (もっと読む)

(もっと読む)

電荷トラップ不揮発性メモリおよびこれを作動させるための方法

【課題】容易に製造され、高密度適用をサポートする不揮発性メモリに対するメモリ技術を提供すること。

【解決手段】マルチゲートメモリセルが、半導体本体と、この半導体本体に並列配置された複数ゲートとを備える。半導体本体の電荷保存構造が、複数ゲートのゲート下部に電荷トラップ場所を含む。列内の第1ゲートおよび最終ゲート近傍の半導体本体にソース・ドレーンバイアス電圧を導通するための回路と、複数ゲートにゲートバイアス電圧を導通するための回路とが含まれる。マルチゲートメモリセルは、ゲートの一部、または全ゲート間の電荷保存場所で、列内の複数ゲート下部に連続マルチゲートチャネル領域を含む。

(もっと読む)

電極を有するキャパシタを備えた集積回路およびキャパシタを製造するための方法

【課題】メモリセルに好適に使用できる電極を有するキャパシタを備えた集積回路およびキャパシタを製造するための方法を提供すること。

【解決手段】本発明は、電極を有する少なくとも1つのキャパシタを備えた集積回路(IC)に関しており、キャパシタの電極のうちの少なくともいずれか一方(10または30)は、少なくとも表面がケイ化物化された半球状結晶粒のシリコンまたはシリコン合金から形成されている。

また、本発明は、ケイ化物化電極を有するこのようなキャパシタを得るための製造方法に関している。

(もっと読む)

Al2O3誘電体を用いるメモリ・セルの絶縁構造

【構成】この発明は,一例示的実施形態では,基板上に形成され,基板をバイアスし,集積回路構造(たとえば,DRAMメモリ・セル)の隣接する動作領域間を絶縁する絶縁ゲートを提供する。ゲート誘電体として,従来のゲート酸化物層ではなく,酸化アルミニウム(Al2O3)を用いて,トレンチ(溝)絶縁領域の下および近くに正孔過剰な蓄積領域を形成する。この発明の別の例示的実施形態は,シャロー・トレンチ(溝)絶縁(STI)領域の効果を高めるために絶縁領域内のライナとして利用される酸化アルミニウム層を提供する。これらの実施形態は,絶縁領域において一緒に用いることも可能である。 (もっと読む)

半導体記憶装置およびその製造方法並びに携帯電子機器

【課題】微細化が容易な半導体記憶装置を提供する。

【解決手段】半導体基板211上には、ゲート絶縁膜214を介して単一のゲート電極217を形成している。ゲート電極217の両側には、第1,第2のメモリ機能体261,262を形成している。半導体基板211のゲート電極217側の表面部にはP型のチャネル領域472を形成し、チャネル領域472の両側にN型の第1,第2の拡散領域212,213を形成している。チャネル領域472は、第1,第2のメモリ機能体261,262下に位置するオフセット領域401と、ゲート電極217下に位置するゲート電極下領域402とで構成されている。オフセット領域401にP型の導電型を与える不純物の濃度は、ゲート電極下領域402にP型の導電型を与える不純物の濃度に比べて実効的に薄くなっている。

(もっと読む)

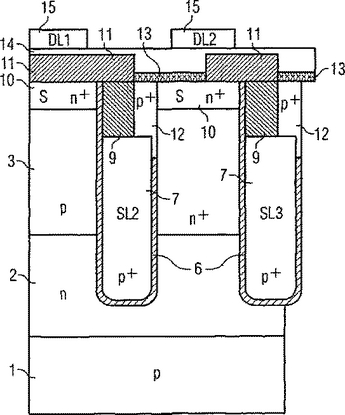

ビット線構造およびその製造方法

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

マルチビット磁気ランダムアクセスメモリ要素

【課題】 マルチビットを格納することが可能な磁気ランダムアクセスメモリ要素を提供する。

【解決手段】 磁気ランダムアクセスメモリ要素が第一磁気トンネル接合及び第二磁気トンネル接合から構成されている。これらの磁気トンネル接合は直列抵抗回路において互いに接続されている。接続された第一及び第二磁気トンネル接合はアクセストランジスタを介してビット線へ接続されている。書込ビット線及び書込データ線が第一及び第二磁気トンネル接合の各々と関連している。これらの線に対して適宜の電流を印加することにより、第一及び第二磁気トンネル接合の各々での磁気ベクトル配向を、少なくとも3個の論理状態のうちのいずれか1つで該要素内に情報を格納するために制御することが可能である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置およびその製造方法。

【解決手段】トンネル効果を利用するトランジスタ100Cを含む半導体記憶装置の製造方法であって、半導体層10に、トレンチ素子分離法により、トランジスタ100Cの形成領域10Cを画定する素子分離絶縁層20を形成する工程と、トランジスタ100Cの形成領域10Cにおいて、少なくとも素子分離絶縁層20に隣接した半導体層10の上部のコーナー部11に、酸化抑制物質を注入する工程と、トランジスタ100Cの形成領域10Cにおける半導体層10の上方に、熱酸化によりトンネル絶縁層31を形成する工程と、トンネル絶縁層31の上方にフローティングゲート電極32を形成する工程と、フローティングゲート電極32に印加する電圧を制御するコントロールゲート42を形成する工程と、少なくともトランジスタ100Cの形成領域10Cに、ソースおよびドレイン領域を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】 半導体装置において、セル面積の縮小化を図ることにある。

【解決手段】 半導体装置100は、半導体基板10と、半導体基板10の内部に形成され、コントロールゲートとして機能する不純物領域22と、半導体基板10の上方に形成されたゲート絶縁層16と、ゲート絶縁層16の上方に、不純物領域22とオーバーラップして形成されたフローティングゲート18と、フローティングゲート18の上方に形成された層間絶縁層50と、層間絶縁層50の上方に、フローティングゲート18とオーバーラップして形成された遮光層52と、を含む。遮光層52は、不純物領域22と電気的に接続している。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルサイズを縮小することができる不揮発性半導体記憶装置及びその製造方法を提供すること

【解決手段】不揮発性半導体記憶装置1は、トレンチ20を有する基板10と、そのトレンチ20内を埋め、且つ、基板10表面から突出するように形成された中心構造体60と、その中心構造体60に接するように基板10上に形成された第2ゲート絶縁膜70と、その第2ゲート絶縁膜70上に形成された浮遊ゲート80と、絶縁層81を介して浮遊ゲート80を覆うように形成された制御ゲート90とを備える。中心構造体60は、補助ゲート50と、その補助ゲート50の周囲を覆うように形成された第1ゲート絶縁膜40とを備える。浮遊ゲート80は、中心構造体60側面にサイドウォール状に形成される。

(もっと読む)

半導体装置の製造方法

【課題】 基板面積の増大なしにキャパシタを容量増大できるDRAM又はこれとロジック回路とを混載した半導体装置の製造方法の提供。

【解決手段】 半導体装置の製造方法は次の通りである。基板上面に第1の絶縁膜50で埋められたトレンチを形成。第1の絶縁膜の一部の上部を除去し、トレンチ内及び基板の上面上に第2の絶縁膜を形成し、その上に導体膜を形成。導体膜及び第2の絶縁膜をパターニングし、ゲート電極16a、プレート電極16b及び容量絶縁膜15を形成。ゲート電極及びプレート電極をマスクとし、イオン注入によりメモリトランジスタの低濃度ドレイン拡散層17b及びソース拡散層18を形成。ゲート電極、プレート電極の側面上に、各々第1、第2のサイドウォール25a、25bを形成。尚、プレート電極は基板の上面の一部とトレンチの露出している側面とに亘る領域上に形成され、ソース拡散層は第1、第2のサイドウォールによって覆われる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】半導体記憶装置の製造方法。

【解決手段】領域10Cを画定する素子分離溝を形成する工程と、半導体層10の上部コーナー部11を熱酸化によりラウンディング形状にする第1ラウンド酸化工程と、半導体層10の上方に、耐酸化膜50を形成する工程と、領域10A,10Bにおいて、素子分離溝に隣接した半導体層10の上部のコーナー部11を熱酸化によりラウンディングする第2ラウンド酸化工程と、素子分離溝に分離絶縁層20を形成する工程と、半導体層10の上方にトンネル絶縁層31を形成する工程と、トンネル絶縁層31の上方にフローティングゲート電極32を形成する工程と、フローティングゲート電極32に印加する電圧を制御するコントロールゲート42を形成する工程と、半導体層10にソースおよびドレイン領域を形成する工程とを含み、第1ラウンド酸化工程における熱酸化温度は、第2ラウンド酸化工程に熱酸化温度より高い。

(もっと読む)

不揮発性半導体メモリ装置及びその製造方法

【課題】 トンネル絶縁膜を欠陥が生成されにくい高品質な絶縁膜にすることができ、書き込み・消去電圧を低減して、素子特性や信頼性の向上をはかる。

【解決手段】 第1導電型の半導体基板11の主面上に第1のゲート絶縁膜13を介して選択的に形成されたフローティングゲート電極14と、フローティングゲート電極14上に第2のゲート絶縁膜15を介して形成されたコントロールゲート電極16と、各ゲート電極に対応して基板11の主面に形成された第2導電型のソース・ドレイン領域18とを具備してなる不揮発性半導体メモリ装置であって、第1のゲート絶縁膜13は、シリコン窒化膜13aをシリコン酸化膜13b,13cで挟んで形成された3層構造であり、且つシリコン窒化膜13aは三配位の窒素結合となっている。

(もっと読む)

半導体装置の製造方法

【課題】 マスクの枚数を増加することなく、かつ、汚染することなく膜厚の異なるゲート絶縁膜を備えた半導体装置の製造方法を提供する。

【解決手段】 メモリセル領域Mに複数のアシストゲート電極部21が互いに間隔を隔てて形成される。周辺回路領域Pでは平坦な半導体基板1の表面が露出する。次に、所定の条件のもとで、露出している半導体基板1の表面に酸化処理が施される。平坦な周辺回路領域Pに露出する半導体基板1の表面に供給される酸素ラジカルの量と比べると、メモリセル領域Mでは、アシストゲート電極部21によって挟まれていることで、露出している半導体基板1の表面にまで供給される酸素ラジカルの量は少なくなる。その結果、メモリセル領域Mに形成されるフローティングゲート酸化膜8aの膜厚は、周辺回路領域Pに形成されるゲート酸化膜10の膜厚よりも薄くなる。

(もっと読む)

分離領域上に消去ゲートを有する不揮発性メモリ

本発明は、不揮発性メモリ装置及びそのような装置の製造方法を提供する。この装置は、浮遊ゲート(16)と、制御ゲート(19)と、分離した消去ゲート(10)とを備える。消去ゲート(10)は、基板(1)内に設けられた分離領域(2)中に、又はその上に設けられる。そのため消去ゲート(10)は、セル・サイズを増加させない。消去ゲート(10)と浮遊ゲート(16)との間の容量は、制御ゲート(19)と浮遊ゲート(16)との間の容量に比べて小さく、消去ゲート(10)と浮遊ゲート(16)との間の酸化物層を介してファウラー・ノルドハイム・トンネルによって浮遊ゲート(16)の帯電が消去される。  (もっと読む)

(もっと読む)

データ記録システムおよびこれを使用する方法

記憶層(2)はマイクロチップ(5)の配列に向かい合って配置される。記憶層(2)は電荷を記憶するように設計され絶縁された複数の導電性ドット(3)を備える。各マイクロチップ(5)はソース(8)とドレイン(9)を接続するトランジスタ・チャネル(7)と一体になっている高誘電率素子(6)を備える。チャネル(7)は高誘電率素子(6)に向かい合って配置されたドット(3)の電荷によって発生された電界によって変更されることができるコンダクタンスを有する。本システムは、マイクロチップ(5)に対する記憶層(2)の相対変位のためのアクチュエータを備えることができる。本システムは、1つのドット(3)から他のドット(3)への電荷の変位を引き起こすことができる電極の配列を備えることができる。  (もっと読む)

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

デュアルポリを用いたビット線注入

本発明は、トランジスタベースメモリデバイス(600)の形成において、デュアルポリプロセス(500)を実装することに関する。このプロセスにより、従来のビット線よりも少ないエネルギーで埋め込みビット線(662)を、深さを浅くして形成することができ、リソースおよびスペースを節約し、Vtロールオフを改善する。埋め込みビット線(662)上には酸化物材料(670、674)も形成され、ビット線(662)とワード線(678)との間の破壊電圧を改善(例えば、増加する)し、これにより、プログラミング電荷と消去電荷との間の識別度を更に高めることができ、さらに、結果として、より確実にデータを記録することができる。このプロセス(500)はまた、埋め込みビット線幅(666)の縮小を促進し、それにより、ビット線(662)を互いに近接して形成することができる。その結果、より多くのデバイスが、同じ領域あるいはより小さな領域に”詰め込まれ”得る。  (もっと読む)

(もっと読む)

2,361 - 2,380 / 2,405

[ Back to top ]