Fターム[5F083GA09]の内容

Fターム[5F083GA09]の下位に属するFターム

三次元化 (1,175)

Fターム[5F083GA09]に分類される特許

221 - 240 / 2,405

半導体記憶装置およびその作製方法

【課題】電力の供給がない状況でもデータの保持が可能、かつ書き込み回数にも制限がない、新たな構造の半導体記憶装置を提供する。また、単位面積あたりの記憶容量を増加させる。

【解決手段】一対の電極と、一対の電極の側壁と接して設けられた絶縁膜と、該絶縁膜を介して一対の電極間に設けられ、一対の電極の上面の高さよりも上面の高さの低い第1のゲート電極と、第1のゲート電極上に設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜および一対の電極と接して設けられた酸化物半導体膜と、少なくとも酸化物半導体膜上に設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜上に設けられた第2のゲート電極と、を有する第1のトランジスタと、一対の電極の一方を介して第1のトランジスタと接続されるキャパシタと、を有し、該キャパシタに保持される電位に応じてデータが記憶されるメモリセルからなる半導体記憶装置である。

(もっと読む)

強誘電体キャパシタ

【課題】還元性雰囲気による特性劣化を抑制することができる構造の強誘電体キャパシタを提供する。

【解決手段】強誘電体キャパシタ積層構造8は、強誘電体膜3と、強誘電体膜の一方表面に接する下部電極2と、強誘電体膜3の他方表面に接する上部電極4とを含む。上部電極4および下部電極2のうちのうちの少なくともいずれか一方が、酸化物導電体層と金属層とを交互に積層した積層電極構造を有している。この積層電極構造は、酸化物導電体層および金属層のうちの少なくともいずれか一方を2層以上含む。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、を有し、駆動回路は、

データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

相変化メモリ及び相変化メモリの製造方法

【課題】信頼性の高い相変化メモリを低コストで提供する。

【解決手段】基板上に形成された絶縁膜と、前記絶縁膜内に設けられた一方の極の電極層及び他方の極の電極層と、前記絶縁膜の上部に設けられた底部が略正方形または略長方形の形状となる開口部と、前記開口部の底部の各々の辺に沿って前記基板面と略平行な面に形成された相変化部と、前記開口部の底部の4隅のうち、対向する2つの隅において前記相変化部と各々接続される一方の極の接続電極と、他の対向する2つの隅において前記相変化部と各々接続される他方の極の接続電極と、を有し、前記一方の極の接続電極は、前記一方の極の電極層と接続されているダイオード部と前記相変化部とを各々接続するものであって、前記他方の極の接続電極は、前記相変化部と前記他方の極の電極層とを各々接続するものであることを特徴とする相変化メモリを提供することにより上記課題を解決する。

(もっと読む)

記憶回路、電子機器

【課題】新たな構成の不揮発性の記憶回路を提供する。

【解決手段】第1の記憶回路と、第2の記憶回路と、第1のスイッチと、第2のスイッチと、位相反転回路と、を有し、第1の記憶回路は、酸化物半導体膜により形成された第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、を有する。酸化物半導体膜により形成された第1のトランジスタと、容量素子と、を用い不揮発性の記憶回路を構成する。また、記憶回路に接続する電源線、及び信号線を少なくし、当該記憶回路に用いるトランジスタ数を減少させることで、回路規模の小さい不揮発性の記憶回路を実現することができる。

(もっと読む)

半導体装置

【課題】半導体装置を小型化する。また、メモリセルを有する半導体装置の駆動回路の面積を縮小する。

【解決手段】少なくとも第1の半導体素子を有する素子形成層と、素子形成層上に設けられた第1の配線と、第1の配線上に設けられた層間膜と、層間膜を介して第1の配線と重畳する第2の配線と、を有し、第1の配線と、層間膜と、第2の配線と、は、第2の半導体素子を構成し、第1の配線と、第2の配線と、は、同電位が供給される配線である半導体装置である。

(もっと読む)

半導体素子、記憶回路、集積回路、及び集積回路の駆動方法

【課題】回路規模の拡大に資する新規の半導体素子を提供する。

【解決手段】独立した2つの電気的スイッチを単体の酸化物半導体層を用いて構成することを要旨とする。例えば、当該半導体素子は、当該酸化物半導体層の下面(第1の面)近傍におけるチャネル(電流経路)の形成と、上面(第2の面)近傍におけるチャネルの形成とを独立して制御する。これにより、2つの電気的スイッチを別個に設ける場合(例えば、2つのトランジスタを別個に設ける場合)と比較して、回路面積を縮小することが可能となる。すなわち、当該半導体素子を用いて回路を構成することで、回路規模の拡大に伴う回路面積の拡大を抑制することが可能になる。

(もっと読む)

半導体装置

【課題】連想メモリは一つのメモリセル内の素子数が多く、一つのメモリセルの面積が大きくなりやすい。そこで、一つのメモリセルの面積を小さくする。

【解決手段】読み出し用のトランジスタのチャネル容量(ゲート電極とチャネル形成領域との間の容量)を用いて電荷の保持を行う。つまり、読み出し用のトランジスタを電荷保持用のトランジスタとして兼用する。また、読み出し用且つ電荷保持用のトランジスタのゲートに電荷供給用のトランジスタのソース又はドレインの一方を電気的に接続する。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

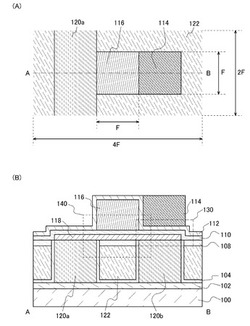

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、一対の電流端子を有し、一対の電流端子の一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される整流素子と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置、記憶装置および半導体装置の作製方法

【課題】書き込み回数に制限がなく、消費電力が低く、記憶内容(電荷)の保持特性が改善され、かつ小型化に適した構造の半導体装置および、当該半導体装置を備える、消費電力が低く、記憶内容(電荷)の保持特性が改善された記憶装置を提供する。

【解決手段】半導体装置の有するトランジスタの半導体層として酸化物半導体を用いることで、ソースとドレイン間のリーク電流を低減できるため、半導体装置および当該半導体装置を備える記憶装置の消費電力低減、保持特性の改善を達成できる。また、トランジスタのドレイン電極、半導体層およびドレイン電極と重なる第1の電極により容量素子を形成し、容量素子と重なる位置でゲート電極を上層へ取り出す構造とした。これにより、半導体装置および当該半導体装置を備える記憶装置を小型化できる。

(もっと読む)

221 - 240 / 2,405

[ Back to top ]