Fターム[5F083GA14]の内容

Fターム[5F083GA14]に分類される特許

1 - 20 / 38

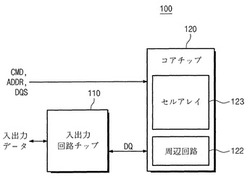

メモリ装置

【課題】大容量化が容易であり、高収率且つ高信頼性を有する半導体メモリ装置が提供される。

【解決手段】本発明に従うメモリ装置は、記憶素子と前記記憶素子にデータを書き込むか、又は読み出す周辺回路を含む第1半導体チップ、及び外部と前記第1半導体チップとの間で交換されるデータ又は信号の入出力機能を遂行する第2半導体チップを含み、本発明のその他の特徴に従うメモリ装置は、外部とデータ又は信号を交換するための入出力回路チップ、及び各々前記入出力回路チップから提供される信号に応答して前記データを格納するか、或いは内部に格納されたデータを読み出して前記入出力回路チップへ出力する、垂直方向に積層される複数のコアチップを含む。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体集積回路

【課題】不揮発性メモリを搭載した半導体集積回路において、外部端子を通して不揮発性メモリの特性テストを実施し、更に、その外部端子にサージ電圧が印加された場合であっても、そのサージ電圧が不揮発性メモリに伝わることを防止する。

【解決手段】半導体集積回路は、不揮発性メモリと、不揮発性メモリに対するデータ書き込み時、書き込み電圧が印加される書き込み制御線と、書き込み制御線に接続された第1ノードと、第1スイッチ回路を介して第1ノードに接続された外部端子と、スイッチ回路を介さずに外部端子に接続された第1ESD保護回路と、動作モードに応じて第1スイッチ回路をON/OFF制御する制御回路と、を備える。動作モードは、外部端子を用いて不揮発性メモリの特性テストを行うテストモードと、外部端子を使用しないユーザモードと、を含む。テストモードにおいて、制御回路は、第1スイッチ回路をONする。ユーザモードにおいて、制御回路は、第1スイッチ回路をOFFする。

(もっと読む)

記憶装置、集積回路装置及び電子機器

【課題】チップ面積や負荷容量の増加を抑止しながら、不揮発性メモリーセルのチャージトラップを低減することができる記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】記憶装置は、電気的にデータの書き込み及び消去が可能な不揮発性メモリーセルM11、M12・・・と、トランジスターTNとを含む。不揮発性メモリーセルM11、M12・・・のワード線WS1とトランジスターTNのゲート電極GTとは、共通の導電配線PLにより形成される。導電配線PLには、ワード線WS1及びゲート電極GTに電圧を供給するためのコンタクトCNAが形成される。平面視において、コンタクトCNAと不揮発性メモリーセルM11、M12・・・との間の導電配線PLの経路において、トランジスターTNのチャネル領域が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルアレイ領域と周辺回路領域との間に生じる層間絶縁膜の段差を解消し、歩留まりの向上を図ることができる半導体装置を提供すること。

【解決手段】半導体基板1上で素子分離用絶縁膜2a、2bによって素子分離された複数の第1の素子10が形成された第1の領域4と、半導体基板1上で第1の領域4に隣接して配されるとともに、素子分離用絶縁膜2b、2cによって素子分離された複数の第2の素子20が形成され、第2の素子20の高さが第1の素子10の高さよりも低い第2の領域5と、第2の領域5にある素子分離用絶縁膜2b、2cの少なくとも一部の領域上に配設されたダミー絶縁膜6c、6dと、第1の領域4及び第2の領域5にわたって形成された層間絶縁膜7と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】被保護素子部、保護素子部及び周辺トランジスタ部を備える半導体装置において、周辺トランジスタ部のゲート絶縁膜と該ゲート絶縁膜よりも膜厚が薄い保護素子部の界面絶縁膜とを同一の工程において形成できるようにする。

【解決手段】半導体基板1の上に、被保護素子用ゲート絶縁膜2を形成し、保護素子部に形成された被保護素子用ゲート絶縁膜2の一部を除去して、開口部14を形成し、半導体基板1の上部に開口部14を通して不純物を注入して、保護素子部にダイオードを形成し、ダイオードの上部に酸化抑制材を注入して、酸化抑制層9を形成し、半導体基板1における周辺トランジスタ部の少なくとも一部とを露出し、露出した半導体基板1の上にゲート絶縁膜11を形成すると共に、酸化抑制層9の上に界面絶縁膜12を形成し、被保護素子用ゲート絶縁膜2、ゲート絶縁膜11及び界面絶縁膜12の上にゲート電極13を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

半導体記憶装置

【課題】不良メモリセルの救済による歩留まり向上を図りつつ、チップサイズの縮小化を実現可能な半導体記憶装置を提供する。

【解決手段】本発明に係る半導体記憶装置50は、メモリセル6と、メモリセル6のうち、動作不良のメモリセル6を救済するための冗長セル25を具備し、不良のメモリセルを正常なメモリセルに置き換える冗長回路(リダンダンシセレクタ13)とを備え、冗長セル25を構成するトランジスタの少なくとも一部に、所定の機能を有する回路(センスアンプ回路15)に配置されたトランジスタの光近接効果の形状補正のために配置しているダミートランジスタを利用する。

(もっと読む)

半導体記憶装置及びその駆動方法

【課題】製造工程完了後にメモリ素子の駆動に必要な正負両極性の高電圧をメモリ素子に印加することを可能とした半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成された被保護素子と、第1の保護トランジスタ41と、第2の保護トランジスタ42とを備えている。第1の保護トランジスタ41は、第2導電型の深いウェル15の上部に形成された第1導電型の第1のウェル51に形成されている。第2の保護トランジスタ42は第2導電型の第2のウェル52に形成されている。第2のソース・ドレイン拡散層21Bは、第3のソース・ドレイン拡散層22Aと電気的に接続され且つ第1のウェル51と同電位である。第4のソース・ドレイン拡散層22Bは、第2の拡散層27と電気的に接続され且つ第2のウェル52及び第2の拡散層27と同電位である。

(もっと読む)

半導体装置及びその製造方法

【課題】FEOLレベルから正負とも低電圧の範囲で拡散工程中のチャージアップから被保護素子を保護し、且つ、拡散工程完了後は被保護素子の駆動に必要な正負両極性の高電圧を被保護素子に印加することが可能な半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成され、被保護素子電極22を有する被保護素子21と、半導体基板11と電気的に接続された基板接続電極42を有する基板接続部41と、被保護素子電極22と基板接続電極42との間に形成されたヒューズ素子電極32を有するヒューズ素子部31とを備えている。ヒューズ素子電極32は、所定の電流を流すことにより切断可能に形成され、ヒューズ素子電極32が切断されていない状態において、被保護素子電極22、基板接続電極42及びヒューズ素子電極32は、一体に形成された導電膜15からなる。

(もっと読む)

半導体装置、その製造方法及び駆動方法

【課題】FEOLプロセスにおける拡散工程中のチャージアップから正負とも低電圧の範囲からメモリ素子を保護し、且つ製造工程完了後は、メモリ素子の駆動に必要な正負両極性の高電圧をメモリ素子に印加することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11に形成された被保護素子と、第2導電型ウェル14に形成された第1の保護トランジスタ41と、第1導電型ウェル13に形成された第2の保護トランジスタ42とを備えている。第2の保護トランジスタ42の第4のソース・ドレイン拡散層22Bは第2の拡散層27と接し、第3のソース・ドレイン拡散層22Aは、第2導電型ウェル14において第1の保護トランジスタ41の第2のソース・ドレイン拡散層21Bと接している。第1の保護トランジスタ41の第1のソース・ドレイン拡散層21Aは、被保護素子電極32と接する第1の拡散層26と接している。

(もっと読む)

半導体装置の製造方法

【課題】不純物導入工程の回数を少なくすることにより、生産効率の向上を図った半導体装置の製造方法を提供する。

【解決手段】トンネル拡散層24を有する不揮発性メモリセルと、ドレイン領域のチャネル部側に前記ドレイン領域よりも低不純物濃度の低濃度層を有するMOSトランジスタと、静電破壊対策トランジスタとを、共通の半導体基板1上に備える半導体装置が製造される。この製造方法は、半導体基板1において不揮発性メモリセル用領域20Rおよび静電破壊対策トランジスタ用領域10Rに第1濃度で不純物を選択的に導入することによって、トンネル拡散層24を形成し、同時に静電破壊対策トランジスタのソース領域11およびドレイン領域12を形成する工程を含む。

(もっと読む)

半導体保護回路およびその製造方法、半導体保護回路の動作方法

【課題】動作時に、メモリセルのワード線に印加できる電圧の自由度を高めた半導体保護回路を提供する。

【解決手段】保護回路は、半導体基板上に設けられ、配線を有する半導体装置の製造工程中に、配線に流入する電荷から前記半導体装置を保護する。保護回路は、配線に接続された第1の金属配線12と、配線に互いに並列に接続された順方向ダイオード202および逆方向ダイオード203と、ドレインが順方向ダイオード202の出力部に、ソースが半導体基板1に、ゲートが上層の金属配線を介して接地にそれぞれ接続されたNMIS204と、ドレインが逆方向ダイオード203の入力部に、ソースが半導体基板1に接続されたPMIS205と、NMIS204のゲートに接続された第1のアンテナ206と、PMIS205のゲートに接続された第2のアンテナ207とを備える。

(もっと読む)

半導体装置及びその作製方法

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置およびその製造方法

【課題】製造時に電荷蓄積層に電荷が蓄積されてしまうことを抑制することが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10上に設けられた電荷蓄積層20と、電荷蓄積層20に電荷をプログラムする際に用いられるゲート電極22と、ゲート電極22と接続するヒューズ56と、を有し、ヒューズ56は、ゲート電極22に電圧が印加される際は電気的に切断されている半導体装置およびその製造方法である。

(もっと読む)

Fin型メモリセル

【課題】Fin−FETとの混載に適したFin型メモリセルを提案する。

【解決手段】本発明の例に関わるFin型メモリセルは、フィン形状のアクティブエリアAAと、アクティブエリアAAの側面に沿うフローティングゲート電極FGと、フローティングゲート電極FGに対してアクティブエリアAAの長手方向に配置され、フローティングゲート電極FGを挟み込む2つのコントロールゲート電極CGとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置のコスト低減を図ることができる技術を提供する。また、メモリセルと高耐圧MISFETのそれぞれの特性に合うウェルを形成することができる技術を提供する。

【解決手段】メモリセル形成領域M1〜M3および低耐圧MISFET形成領域Tを覆い、高耐圧MISFET形成領域Kを露出するレジストパターン25を形成する。そして、このレジストパターン25をマスクにして、高耐圧MISFET形成領域Kにp型ウェル26を形成する。続いて、レジストパターン25をマスクにしてチャネル形成領域27を形成する。その後、高耐圧MISFET形成領域Kおよび低耐圧MISFET形成領域Tを覆い、メモリセル形成領域M1〜M3を露出するレジストパターンを形成する。そして、このレジストパターンをマスクにして、メモリセル形成領域M1〜M3にp型ウェルおよびチャネル形成領域を形成する。

(もっと読む)

1 - 20 / 38

[ Back to top ]