Fターム[5F083JA13]の内容

半導体メモリ (164,393) | 材料 (39,186) | キャパシタ絶縁膜材料、ゲート絶縁膜材料 (10,102) | 酸化物系 (9,104) | 複酸化物 (3,106) | ABO3(ペロブスカイト)型 (1,886)

Fターム[5F083JA13]の下位に属するFターム

SrTi03,(Ba、Sr)Ti03 (538)

Pbを含むもの(PTO,PZT,PLT,PLZT系) (1,106)

Fターム[5F083JA13]に分類される特許

61 - 80 / 242

前駆体組成物および圧電素子の製造方法

【課題】絶縁性に優れた複合酸化物積層体およびその製造方法を提供する。

【解決手段】基板20と、前記基板20の上方に形成され、一般式ABO3で表される第1複合酸化物層24と、前記第1複合酸化物層24の上方に形成され、一般式AB1-xCxO3で表される第2複合酸化物層26と、を含み、A元素は、少なくともPbからなり、B元素は、Zr、Ti、V、WおよびHfの少なくとも一つからなり、C元素は、NbおよびTaの少なくとも一つからなる。

(もっと読む)

圧電材料および圧電素子

【課題】圧電特性が良好な圧電材料を提供する。

【解決手段】下記一般式(1)で表されるペロブスカイト型複合酸化物からなり、前記ペロブスカイト型複合酸化物の結晶系が少なくとも単斜晶構造を含んでいる圧電材料。前記ペロブスカイト型複合酸化物の結晶系が、単斜晶構造と菱面体晶構造を有する混在系、または単斜晶構造と正方晶構造を有する混在系であることが好ましい。

(式中、AはBi元素であり、MはFe、Al、Sc、Mn、Y、Ga、Ybのうちの少なくとも1種の元素である。xは0.4≦x≦0.6の数値を表す。yは0.17≦y≦0.60の数値を表す。)

(もっと読む)

半導体装置及びその製造方法

【課題】下部電極を構成する貴金属電極に変形が発生することを防止し、正常な形状の立体セルを形成する。

【解決手段】半導体装置は、半導体基板10の上に形成され、開口部180を有する層間絶縁膜160と、開口部180の少なくとも側壁上に形成された密着層240と、開口部180の底面上及び少なくとも密着層240の側面上に形成された第1の下部電極260と、第1の下部電極260の上に形成された強誘電体膜又は高誘電体膜360と、強誘電体膜又は高誘電体膜360の上に形成された上部電極340とを備えている。第1の下部電極260は、開口部180から突出する突出部260aを有し、強誘電体膜又は高誘電体膜360は、突出部260aを覆うように形成され、上部電極340は、強誘電体膜又は高誘電体膜360を覆うように形成されている。

(もっと読む)

キャパシタ用絶縁膜、キャパシタ及び半導体装置

【課題】高い誘電率を示すキャパシタ用絶縁膜は、キャパシタに用いられた際にリーク電流が増大する。

【解決手段】2つの電極の間に挟まれて用いられるキャパシタ用絶縁膜を、チタン酸ストロンチウム又はチタン酸バリウムストロンチウムのチタンサイトの一部がハフニウム元素で置換された結晶から形成する。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタを有する信頼性の高い半導体装置を高い歩留りで製造し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の絶縁膜26と、ソース/ドレイン拡散層22に達する第1のコンタクトホール28a内に埋め込まれた第1の導体プラグ32と、第1の絶縁膜上に形成されたキャパシタ44と、第1の絶縁膜上に、キャパシタを覆うように形成された第1の水素拡散防止膜48と、第1の水素拡散防止膜上に形成され、表面が平坦化された第2の絶縁膜50と、第2の絶縁膜上に形成された第2の水素拡散防止膜52と、キャパシタの下部電極38又は上部電極42に達する第2のコンタクトホール56内に埋め込まれた第2の導体プラグ62と、第1の導体プラグに達する第3のコンタクトホール内に埋め込まれた第3の導体プラグ62と、第2の導体プラグ又は第3の導体プラグに接続された配線64とを有している。

(もっと読む)

発光材料、圧電体、電歪体、強誘電体、電場発光体、応力発光体、及びこれらの製造方法

【課題】摩擦力、剪断力、衝撃力などの機械的な外力が加えられることによって生じる変形によって発光する新規な発光材料を提供する。

【解決手段】本発明の発光材料は、ウルツ鉱型構造の酸化亜鉛と、立方晶又はウルツ鉱型構造の硫化亜鉛と、立方晶の酸化マンガンとの結晶構造の中から少なくとも2種類以上の結晶構造を有するものや、一般式(Ca1−xA’x)yBa1−yTiO3、(Mg1−xA’x)yBa1−yTiO3、及び(Sr1−xA’x)yBa1−yTiO3(0.0001≦x≦0.05,0.005≦y≦0.995,A’はDy,La,Gd,Ce,Sm,Y,Nd,Tb,Pr,Erからなる群より選ばれる希土類元素)からなるもの等のような、複数の結晶構造が混在した混相を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

(もっと読む)

ペロブスカイト型酸化物、酸化物組成物、酸化物体、圧電素子、及び液体吐出装置

【課題】強誘電性能に優れた新規組成のペロブスカイト型酸化物を提供する。

【解決手段】ペロブスカイト型酸化物は、下記一般式で表されるものである。(Aa,Bb)(Cc,Dd,Xx)O3(A:Aサイト元素である。A=Bi、0<a。B:1種又は複数種のAサイト元素である。0≦b<1.0。C:Bサイト元素である。C=Fe、0<c<1.0。D:1種又は複数種のBサイト元素である。0≦d<1.0。0<b+d。X:1種又は複数種のBサイト元素である。CとDの化学式上の平均価数よりも化学式上の平均価数が大きい元素である。0<x<1.0。(Aサイトの化学式上の平均価数)+(Bサイトの化学式上の平均価数)>6.0。O:酸素。Aサイト元素とBサイト元素と酸素のモル比は1:1:3が標準であるが、これらのモル比はペロブスカイト構造を取り得る範囲内で基準モル比からずれてもよい。)

(もっと読む)

強誘電体記憶装置の初期化方法、強誘電体記憶装置および電子機器

【課題】過去の熱履歴等によるキャパシタのインプリント現象をリセットし、また、以降の処理によるインプリント現象の影響を低減することができる強誘電体記憶装置の初期化方法を提供する。

【解決手段】本発明に係る強誘電体記憶装置の初期化方法は、下部電極(9)と上部電極(13)との間に配置された強誘電体膜(11)を有するメモリセルがアレイ状に配置された強誘電体記憶装置をパッケージする工程と、前記下部電極および上部電極に電位を印加する検査工程と、前記検査工程の後において、前記上部電極に第1の電位[0V]を、前記下部電極に前記第1の電位より高い第2の電位[Vcc]を印加した後、動作保証温度より高い第1温度で熱処理する工程と、を有する。また、前記第1温度を、前記検査工程における検査温度およびパッケージ工程における処理温度より高くする。

(もっと読む)

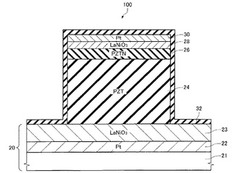

複合酸化物積層体、複合酸化物積層体の製造方法、デバイス

【課題】絶縁性に優れた複合酸化物積層体およびその製造方法を提供する。

【解決手段】基板20と、前記基板20の上方に形成され、一般式ABO3で表される第1複合酸化物層24と、前記第1複合酸化物層24の上方に形成され、一般式AB1-xCxO3で表される第2複合酸化物層26と、を含み、A元素は、少なくともPbからなり、B元素は、Zr、Ti、V、WおよびHfの少なくとも一つからなり、C元素は、NbおよびTaの少なくとも一つからなる。

(もっと読む)

酸化物体、圧電素子、及び液体吐出装置

【課題】バイポーラ分極−電界曲線が非対称ダブルヒステリシス性を示し、大きな変位が期待される、強誘電性材料又は反強誘電性材料からなる酸化物体を提供する。

【解決手段】酸化物体は、強誘電性材料又は反強誘電性材料からなり、最大印加電界Emaxと最小印加電界Eminの絶対値とを同一に設定して(Emax=|Emin|)測定されるバイポーラ分極−電界曲線が、少なくとも5個の変曲点を有し、かつ、最大分極値Pmaxと最小分極値Pminの絶対値とが異なる(Pmax≠|Pmin|)非対称ダブルヒステリシス性を有するものである。1種又は2種以上のペロブスカイト型酸化物からなり、不可避不純物を含んでいてもよい。

(もっと読む)

強誘電体膜、圧電素子、及び液体吐出装置

【課題】バイポーラ分極−電界曲線がダブルヒステリシス性を示し、大きな変位が期待される新規な強誘電体膜を提供する。

【解決手段】強誘電体膜は、最大印加電界Emaxと最小印加電界Eminの絶対値とを同一に設定して(Emax=|Emin|)測定されるバイポーラ分極−電界曲線が、少なくとも5個の変曲点を有し、かつ、最大分極値Pmaxと最小分極値Pminの絶対値とが略等しい(Pmax≒|Pmin|)ダブルヒステリシス性を有するものである。強誘電体膜は、1種又は2種以上のペロブスカイト型酸化物からなり、不可避不純物を含んでいてもよい。

(もっと読む)

金属酸化物、圧電材料および圧電素子

【課題】鉛やアルカリ金属を使用せず、広い温度領域で安定した結晶構造を有し、高い絶縁性及び圧電性を備えている圧電材料およびそれを用いた圧電素子を提供する。

【解決手段】正方晶の結晶構造を有する、Ba(SixGeyTiz)O3(ただし0≦x≦1、0≦y≦1、0≦z≦0.5、x+y+z=1)で表される酸化物からなる圧電材料。上記の圧電材料が一対の電極によって挟持された圧電素子において、前記一対の電極の少なくとも一つがSrRuO3またはNiである圧電素子。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリキャパシタなどのキャパシタとともに、大容量を有する平滑用キャパシタを備えた半導体装置において、チップサイズの増大及び製造コストの増加が抑制された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1の上方に形成され、第1の下部電極12Aと第1の容量絶縁膜13Aと第1の上部電極14Aとからなるメモリキャパシタと、半導体基板における論理回路領域上に形成された論理回路トランジスタ4と、論理回路トランジスタ4の上方に形成され、第2の下部電極12Bと第2の容量絶縁膜13Bと第2の上部電極14Bとからなる平滑用キャパシタとを備えている。第2の容量絶縁膜13Bは、第1の容量絶縁膜13Aと同一組成の材料から構成され、且つ、第1の容量絶縁膜13Aの膜厚よりも大きい膜厚を有する。

(もっと読む)

薄膜キャパシタ

【課題】キャパシタ誘電体膜を薄膜化しても容量を確保できる薄膜キャパシタを提供する。

【解決手段】薄膜キャパシタは、基板と、前記基板上に形成された単結晶金属膜よりなる下部電極と、前記下部電極上にエピタキシャルに形成された、膜厚が100nm以下のABO3ペロブスカイト構造を有するチタン酸バリウムストロンチウムの単結晶薄膜よりなるキャパシタ誘電体膜と、前記キャパシタ誘電体膜上に形成された上部電極とを含み、前記キャパシタ絶縁膜はスカンジウム(Sc)を含む。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】コンタクトプラグ上に直接形成される下地層の結晶配向性を良好にし、さらにこの下地層の平坦性をも良好にすることで、下部電極や強誘電体膜の結晶配向性の改善を図った強誘電体メモリ装置の製造方法を提供する。

【解決手段】基板の上方に導電性の下地層を形成する工程と、下地層の上方に第1電極と強誘電体膜と第2電極とを積層する工程と、を含む強誘電体メモリ装置の製造方法である。下地層の形成工程は、プラグ20を含む層間絶縁膜26上に、自己配向性を有する導電材料からなる導電層411を形成する工程と、導電層411を窒素雰囲気中で熱処理し、窒化導電層412とする工程と、窒化導電層412を、シリコン酸化膜研磨用のスラリーを用いたCMP法によって低研磨速度で平坦化処理し、プラグ20を含む層間絶縁膜26上を覆った状態の平坦化窒化チタン層41とする工程と、を含む。

(もっと読む)

強誘電体メモリ素子の製造方法

【課題】良好な強誘電体膜を形成する。

【解決手段】本発明の強誘電体メモリ素子の製造方法は、基板の上方に第1電極33aを形成する工程と、第1電極33a上に、チタン膜341を形成する工程と、第1有機金属ガス及び第1酸素ガスを反応させることにより生成された生成物をチタン膜341上に成膜するとともに、この生成物とチタン膜341とを固溶させて、第1電極33a上に第1強誘電体膜34aを形成する工程と、第1強誘電体膜34aの上方に第2電極35aを形成する工程と、を含む

(もっと読む)

強誘電体メモリ素子の製造方法

【課題】良好な強誘電体メモリ素子を製造する。

【解決手段】本発明の強誘電体メモリ素子の製造方法は、白金からなる表層332aを含んだ第1電極33aを形成する工程と、第1電極33aの上方において、鉛を含有する第1有機金属ガスと、これを化学反応させるのに必要な量よりも少ない酸素ガスと、を供給しかつ化学反応させて、第1有機金属ガスの有機基の少なくとも一部を残した鉛化合物を生成するとともに、これを第1電極33a上に成膜して不活性鉛層341aを形成する工程と、不活性鉛層341a上において、強誘電体膜の金属成分を含有する第2有機金属ガスと、これを化学反応させるのに必要な量よりも多い酸素ガスと、を供給しかつ化学反応させてその生成物を第1電極33aの上方に成膜するとともに、この膜と不活性鉛層341aとを固溶させて強誘電体膜を形成する工程と、を有する。

(もっと読む)

容量可変素子およびフィルタ回路

【課題】金属酸化物膜を使った容量可変素子において、効率的に容量を変化させる。

【解決手段】容量可変素子は、ペロブスカイト構造を有する金属酸化膜と、前記金属酸化膜を挟持し、外部電圧源に接続される第1および第2の電極膜と、前記金属酸化膜と前記第1および第2の電極膜とを含むキャパシタに対し電気的に直列に挿入されたバイアス電圧源と、を含み、前記バイアス電圧源は、前記キャパシタに、前記金属酸化膜の比誘電率の電圧依存性を最大化するバイアス電圧を印加する。

(もっと読む)

61 - 80 / 242

[ Back to top ]