Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

61 - 80 / 403

限られたチャージ拡散を有するチャージトラップメモリ

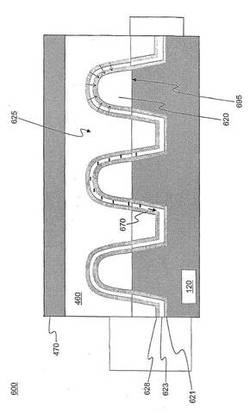

【課題】隣接メモリセルへの漏洩電流を減らすフラッシュメモリ、特にチャージトラップメモリおよびそれを形成するプロセスフローの提供。

【解決手段】セルチャンネル620を含む半導体線が、STI領域120上に形成される。セルチャンネルは、トンネル酸化物層621、トラッピング誘電体層623、およびブロッキング誘電体層628を含む活性誘電体スタックで覆われる。結果として得られるセルチャンネルを分離するトレンチ625は、伝導層460で少なくとも部分的に充填され得る。活性誘電体層および/または伝導層の部分は、セルチャンネルの下、たとえば、セルチャンネルおよびSTI領域の間の界面695の下に位置し得る。そのような構成は、活性誘電体スタックおよび/または半導体層がセルチャンネルの下に位置しない構成に比べて、あるセルチャンネルから隣接セルチャンネルに拡散する荷電粒子670に対して経路長の増大をもたらす。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

半導体集積回路装置

【課題】ゲート絶縁膜の厚さが異なる複数種類の電界効果トランジスタを有する半導体集積回路装置の信頼性を高める。

【解決手段】第1の電界効果トランジスタQ3及び第2の電界効果トランジスタQ4は埋込絶縁膜25によって分離され、ゲート絶縁膜31,32は各々熱酸化膜27、30と堆積膜27,28,29が積層され、第1の電界効果トランジスタの熱酸化膜は第2の電界効果トランジスタの熱酸化膜より厚く、各トランジスタの堆積膜は、各々各トランジスタの熱酸化膜よりも厚く構成され、第1の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ端部と埋込絶縁膜との間に第1の電界効果トランジスタの堆積膜が設けられ、第2の電界効果トランジスタのゲート電極は、ゲート幅方向における端部が埋込絶縁膜上に引き出され、かつ前記端部と埋込絶縁膜との間に第2の電界効果トランジスタの堆積膜が設けられる。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】デバイス特性の劣化を抑制した不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】第1ダミーセル領域121に設けられた素子分離絶縁層33と、第2ダミーセル領域122に設けられた素子分離絶縁層43と、第1ダミーセル領域121と第2ダミーセル領域122との間の境界に位置する素子分離絶縁層51とを備える。素子分離絶縁層33の上面は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層43の上面は、浮遊電極層42の上面と同じ高さに位置する。浮遊電極層32に隣接する素子分離絶縁層51の上面の端部は、浮遊電極層32の上面よりも低い高さに位置する。素子分離絶縁層51の上面は、浮遊電極層32の側面から浮遊電極層42の側面へ向かって上昇する傾斜TLを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

半導体装置及びその製作方法

【課題】半導体記憶装置に適するトランジスタ構造及びその製作方法の提供。

【解決手段】デュアルチャネルトランジスタ50は、少なくとも、第一方向に沿って伸展する第一STI(シャロートレンチアイソレーション)と第二方向に沿って伸展する第二STIにより分離され、第一STIと第二STIが交差する半導体アイランド22と、第二方向に沿って伸展し、半導体アイランドの表面から内側に向かって凹んだゲートトレンチ26と、第二方向に沿って伸展し、ゲートトレンチ内に設けられたゲート30と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第一ソース/ドレイン領域と、第一ソース/ドレイン領域の間に設けられた第一U字型チャネル領域60と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第二ソース/ドレイン領域と、第二ソース/ドレイン領域の間に設けられた第二U字型チャネル領域62とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】メモリセルアレイの耐ストレス性を向上できるようにする。

【解決手段】局所選択ゲート電極CSGが、部分的にメモリセルトランジスタMTを選択(例えばメモリセルトランジスタMT0〜MT7)することで、その他のメモリセルトランジスタMT(例えばメモリセルトランジスタMT8〜MT63)を非選択状態にすることができ、当該非選択状態とされたメモリセルトランジスタMTに高電圧を与える必要がない。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】閾値電圧の制御性を向上させて形成された複数種類のトランジスタを備える不揮発性記憶装置、および、それに適した製造方法を提供する。

【解決手段】1つの半導体基板2の表面に形成された複数種類のMOSトランジスタを有する不揮発性記憶装置であって、n形のソース領域14およびドレイン領域15と、その間の半導体基板2の表面上に設けられたゲート絶縁膜17と、ゲート電極18と、ゲート絶縁膜17の直下に位置し、n形不純物とp形不純物との両方を含むチャネル領域42と、を有するMOSトランジスタ10と、n形のソース領域24およびドレイン領域25と、その間の半導体基板2の表面上に設けられたゲート絶縁膜27と、ゲート電極28と、ゲート絶縁膜27の直下に位置し、n形不純物の濃度プロファイルがチャネル領域42と同じであるチャネル領域43と、を有するMOSトランジスタ20と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する

【解決手段】半導体基板1内に形成された一対の第1の不純物拡散領域1bと、一対の第1の不純物拡散領域1bに挟まれ、一対の第1の不純物拡散領域1bに隣接して形成され、第1の不純物拡散領域1bと同じ導電型且つ第1の不純物拡散領域1bよりも不純物濃度の低い一対の第2の不純物拡散領域1aと、一対の第2の不純物拡散領域1aに挟まれたチャネル領域と、第1の不純物拡散領域1b上に形成された周辺絶縁膜4と、第2の不純物拡散領域1a上およびチャネル領域上に形成され、周辺絶縁膜4よりも膜厚の厚いゲート絶縁膜3と、ゲート絶縁膜3上且つチャネル領域の略直上に形成されたゲート電極5とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】安定した容量を確保し配置面積低減が可能なキャパシタ素子を有する半導体記憶装置を提供する。

【解決手段】第1の上面12aを有するメモリセル領域1及び第1の上面12aより裏面に近い第2の上面12bを有する周辺回路領域3を有する半導体基板11、メモリセル領域1の第1の上面12a上のトンネル絶縁膜13a及びトンネル絶縁膜13a上の下層電極膜15aを有するメモリセルトランジスタ1a、トンネル絶縁膜13aより厚い周辺回路領域3の第2の上面12b上のゲート絶縁膜13b及び下層電極膜15aと同じ膜厚のゲート絶縁膜13b上の下層電極膜15bを有する高電圧トランジスタ3a、並びに周辺回路領域3にあり、第1及び第2の上面12a、12bをそれぞれ上端面及び底面とする凹凸面に沿ったキャパシタ誘電体膜13c及びキャパシタ誘電体膜13c上の下面に凹凸をなす下層電極膜15cを有するキャパシタ素子3bを備える。

(もっと読む)

半導体装置

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

フラッシュメモリの製造方法

【課題】フラッシュメモリの製造工程において、エッチングによるSTI膜の膜減りを抑制することができる製造方法と、それを可能にするスプリットゲートタイプのMONOS型フラシュメモリ構造を提供する。

【解決手段】ワードゲートとコントロールゲートを含むスプリットゲートタイプのMONOS型フラシュメモリの製造方法であって、STIによって分離された半導体基板の不純物拡散層上に、酸化膜を挟んだワードゲートを形成する工程と、該STIとワードゲートが形成された半導体基板の表面全体に酸化膜、窒化膜、酸化膜の順に成膜されるONO層を形成する工程と、該ONO層の上にコントロールゲート用導電膜(10)を形成する工程と、該コントロールゲート用導電膜の表面全体にマスク用絶縁膜(26)を形成する工程と、を含む。

(もっと読む)

埋立ビットラインを有する半導体装置及び半導体装置の製造方法

【課題】埋立ビットラインを有する半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】埋立ビットラインを備えて低抵抗を有する垂直ピラートランジスタを含む半導体装置及びその製造方法が開示される。垂直ピラートランジスタは、基板上に形成され、下部と上部を有する本体、本体の上部に配置されるソース/ドレインノード、そして、本体の下部に配置されるドレイン/ソースノードを含む。半導体装置は、少なくとも本体の下部の上部表面に形成され、金属シリサイドを含む前記埋立ビットライン及び前記本体の上部を部分的に包むワードラインを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】正確なデータの読み出しが可能な半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、基板と基板の表面に形成された周辺回路とを有する基体と、基体上にそれぞれ交互に積層された複数の導電層と複数の絶縁層とを有する積層体と、積層体の積層方向に形成されたメモリホールの内壁に設けられた電荷蓄積膜を含むメモリ膜と、メモリホール内におけるメモリ膜の内側に設けられたチャネルボディと、積層体を貫通して設けられたコンタクトプラグと、周辺回路と積層体との間に設けられコンタクトプラグの下端部に接続されたグローバルビット線と、積層体の上に設けられ、その延在方向に分断された複数のローカルビット線であって、チャネルボディに接続されると共にコンタクトプラグを介してグローバルビット線に対して共通に接続された複数のローカルビット線と、を備えた。

(もっと読む)

電極構造体を具備するキャパシタ、その製造方法及び電極構造体を含む半導体装置

【課題】電極構造体を具備するキャパシタ、その製造方法及び電極構造体を含む半導体装置を提供すること。

【解決手段】構造的安全性及び電気的特性が改善された電極構造体を有するキャパシタとそのような電極構造体が適用された半導体装置が開示される。電極構造体は絶縁層を有する基板、絶縁層を埋め立てる金属を含む第1導電パターン、第1導電パターンから延びて金属酸化物を含む第2導電パターン、そして第2導電パターン上に配置される第3導電パターンを含むことができる。写真エッチング工程を利用せずに簡単な工程で要求されるレベルの電気的な特性と集積度を確保することのできるキャパシタと半導体装置を実現することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリ混載ロジックデバイスのRAM領域の閾値電圧のばらつきを低減する。

【解決手段】本発明の半導体装置は、ロジック領域101と、RAM領域102とが設けられたシリコン基板1と、ロジック領域101に形成されたNMOSトランジスタ20と、RAM領域102に形成されたNMOSトランジスタ40と、を備える。NMOSトランジスタ20、40は、ゲート絶縁膜5とメタルゲート電極6との順でシリコン基板1上に積層された積層構造を有する。NMOSトランジスタ20は、シリコン基板1とメタルゲート電極6との間に、構成元素として、ランタン、イッテルビウム、マグネシウム、ストロンチウム及びエルビウムからなる群から選択される元素を含む、キャップメタル4を有する。NMOSトランジスタ40には、キャップメタル4が形成されていない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】DRAMと論理集積回路とを混載したシステムオンチップ構造の半導体集積回路装置において、DRAMと論理集積回路のそれぞれの性能を共に維持しながらワンチップ化を実現する。

【解決手段】DRAMと論理集積回路とを混載したシステムオンチップ構造の半導体集積回路装置において、DRAMの直接周辺回路を構成するMISFET(Qn1、Qp1)のソース、ドレインの表面と、間接周辺回路を構成するMISFETのソース、ドレインの表面と、論理集積回路を構成するMISFET(Qn2、Qp2)のソース、ドレインの表面にシリサイド層(20)を形成し、DRAMのメモリセルを構成するメモリセル選択用MISFET(Qs)のソース、ドレインの表面にはシリサイド層を形成しない。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルアレイ端部の耐圧を向上させる。

【解決手段】不揮発性半導体記憶装置10は、メモリセルトランジスタが配置される第1の領域と、メモリセルトランジスタに電気的に接続されたワード線を引き出す電極21が配置される第2の領域と、周辺トランジスタが配置される第3の領域とを有する。第1の領域には、第1の幅を有する複数の第1のアクティブ領域AA1が設けられ、第2及び第3の領域にはそれぞれ、第1の幅より広い第2の幅を有する複数の第2及び第3のアクティブ領域AA3,AA5が設けられる。第2の領域の素子分離層23Bの上面は、第1の領域の素子分離層23Aの上面より高く、第2の領域の電荷蓄積層32Bは、上部の角の曲率半径が、第3の領域の電荷蓄積層43よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域の配線容量を低減し、かつ、周辺回路領域の配線抵抗を低減した半導体装置とその製造方法の提供。

【解決手段】本発明の半導体装置の製造方法は、メモリセル領域に縦型MOSトランジスタを、周辺回路領域にプレーナ型MOSトランジスタを形成し、前記縦型MOSトランジスタ上に深孔型立体キャパシタ素子10を形成する第1工程と、キャパシタ素子10上にメモリセル領域全体を覆うようにキャパシタ上部電極層31を形成し、前記メモリセル領域の上面の位置を、前記周辺回路領域の上面の位置よりも高く設定する第2工程と、前記周辺回路領域に第2コンタクトプラグ35を形成する第3工程と、前記メモリセル領域のキャパシタ上部電極層31上にセル部上部配線38を形成し、前記周辺回路領域に第2コンタクトプラグ35と接続し、セル部上部配線38よりも鉛直方向の膜厚が厚い周辺部上部配線39を形成する第4工程とを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】小型化が容易な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】基板上に、不純物が導入された半導体膜と不純物が導入されていない半導体膜とを交互に積層させて積層体を形成し、第1領域において貫通ホール及びスリットを形成する。そして、貫通ホール又はスリットを介したエッチングにより、不純物が導入されていない半導体膜における第1領域に配置された部分を除去し、第2領域に配置された部分を残留させる。次に、不純物が導入されていない半導体膜を除去した空間に絶縁材料を埋め込む。次に、貫通ホールの内面上に電荷蓄積膜を形成し、貫通ホール内に半導体ピラーを形成する。次に、第2領域において、積層体を貫くコンタクトホールを形成し、その側面上にスペーサ絶縁膜を形成し、その内部にコンタクトを形成する。

(もっと読む)

61 - 80 / 403

[ Back to top ]