Fターム[5F083ZA07]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリセルと周辺回路の関係 (1,873) | MOSFETの構造が異なるもの (1,090) | ゲート絶縁膜が異なるもの (403)

Fターム[5F083ZA07]に分類される特許

121 - 140 / 403

半導体装置の製造方法および半導体装置

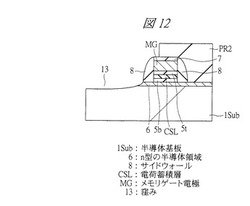

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】信頼性の高い不揮発性メモリと周辺回路を含む半導体装置を提供する。

【解決手段】不揮発性半導体記憶装置の製造方法は、周辺回路領域では、フローティングゲート電極層p1sは除去し、コントロール電極層p2はパターニングしない状態で、不揮発性メモリの積層ゲート電極を形成し、サイドウォ−ルSW1を形成し、周辺回路領域では、コントロール電極層PGの側壁上に第1冗長絶縁性サイドウォ−ルSNPを形成し、コントロールゲート電極層PGをパターニングして単層ゲート電極PGを形成すると共に、第1冗長絶縁性サイドウォ−ルSNPに隣接する部分を残す。

(もっと読む)

不揮発性半導体記憶装置

【課題】周辺回路の分離酸化膜上にエッチング残渣を発生させることなく、高いカップリング比を有するメモリセルを有する不揮発性半導体記憶装置を提供する。

【解決手段】本発明に係る不揮発性半導体記憶装置は、メモリセルと、該メモリセルに隣接する周辺回路とを有する不揮発性半導体記憶装置であって、基板の活性領域を分離する素子分離と、前記活性領域に形成された半導体素子とを備え、前記メモリセルにおける前記活性領域は、短手方向に複数並んで配置された短冊状の第1活性領域と、該第1活性領域の端部を相互に接続すると共に前記メモリセルを取り囲むように配置された第2活性領域とを有し、前記周辺回路における前記素子分離の上面が、前記基板の表面と同等の高さであるか若しくは該表面よりも高い。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留りを向上させる。

【解決手段】素子分離領域2を含む半導体基板1上に多結晶シリコン膜7と絶縁膜8を形成してパターニングし、多結晶シリコン膜7かならる下部電極11a,11bおよび下部電極11a,11b間のダミーパターン12を形成する。下部電極11a,11bおよびダミーパターン12とそられの上に形成された絶縁膜8を覆うように多結晶シリコン膜17を形成し、多結晶シリコン膜17上にキャップ保護膜を形成する。キャップ保護膜上に反射防止膜およびフォトレジストパターンを形成し、フォトレジストパターンをエッチングマスクとして用いて反射防止膜、キャップ保護膜および多結晶シリコン膜17を順次ドライエッチングすることで、下部電極11a,11b上に容量絶縁膜としての絶縁膜8を介して多結晶シリコン膜17からなる上部電極21a,21bを形成してキャパシタ36a,36bを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】同一基板内にEPROMとEPROM以外の機能デバイスを備えた半導体装置に関する技術を提供する。

【解決手段】半導体装置10では、EPROM領域Aにおいて、半導体基板20上に半導体基板20の側からゲート酸化膜41とフローティングゲート電極42と絶縁膜43とコントロールゲート電極44がこの順に積層されて構成されている。また、DRAM領域Bにおいて、半導体基板20上に半導体基板20の側から絶縁膜43と金属膜(ソース電極67、87とドレイン電極68、88を含む)がこの順に積層されて構成されている。本実施例の半導体装置10では、EPROM領域Aの絶縁膜43とDRAM領域Bの絶縁膜43が同一層で形成されており、EPROM領域Aのコントロールゲート電極44とDRAM領域Bの金属膜が同一層で形成されている。そのため、半導体装置10を形成する際に、その工程が増加することが抑制される。

(もっと読む)

半導体装置

【課題】フローティングゲート電極としての導電膜を素子分離絶縁膜を利用して自己整合的に形成すると同時に、半導体素子としての導電膜を形成することが可能な技術を提供する。

【解決手段】半導体装置では、複数の素子分離部分36の間の半導体基板1上に絶縁膜8を介してフローティングゲート電極としての導電膜9が形成されている。そして、フローティングゲート電極としての導電膜9と同一材料の、半導体素子としての導電膜9が素子分離部分6に埋め込まれている。

(もっと読む)

半導体装置およびその製造方法

【課題】接合リーク電流を低減可能なDRAM型半導体装置を提供する。

【解決手段】メモリセル部内におけるゲート絶縁膜8の厚みを周辺回路部内におけるゲート絶縁膜9の厚みよりも大きくする。また、メモリセル部におけるMOSトランジスタのソース/ドレインを二重拡散層構造5,6とし、周辺回路部におけるMOSトランジスタのソース/ドレインを三重拡散層構造5,6,7にする。このようにメモリセル部内におけるゲート絶縁膜8の厚みを周辺回路部内におけるゲート絶縁膜9の厚みよりも大きく設定することにより、メモリセル部内におけるp型不純物領域4aの濃度を低くすることが可能となり、接合リーク電流を低減することが可能となる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多値記録が可能なメモリセルを備えた半導体記憶装置の性能を向上させる。

【解決手段】シリコン基板100上に配置された複数のメモリセルを有する半導体集積回路装置であって、個々のメモリセルは、素子分離膜118で規定されたアクティブ領域において、ボトム酸化膜105、電荷蓄積窒化膜106、トップ酸化膜107を介して形成されたメモリゲート電極103を有する。素子分離膜118の一部上面は、アクティブ領域上面の高さよりも高くなるように突出して形成され、電荷蓄積窒化膜106はその素子分離膜118が突出した部分の側壁から、アクティブ領域表面に渡って形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル部でアスペクト比の高い下部電極の倒壊を防止するとともに、前記メモリセル部に隣接する周辺回路部への薬液の浸透を防止する半導体装置および半導体装置の製造方法を得るという課題があった。

【解決手段】メモリセル部と、前記メモリセル部を囲む周辺回路部と、を有する半導体装置であって、前記メモリセル部は、複数の筒状の下部電極13と、下部電極13の側面を覆う第1の絶縁膜と、前記第1の絶縁膜を覆う上部電極15と、を有するキャパシタ30を備えたメモリセル本体部55と、メモリセル本体部55を囲む溝部73を備えたメモリセル外周部56と、を有しており、下部電極13の筒内に充填された第1の支持膜61と、第1の支持膜61の開口側の面に接面されるとともに複数の下部電極13を結ぶように延在された第2の支持膜62と、を有する半導体装置を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置

【課題】ワード線引き出し部におけるワード線とシリコン基板との距離をセルアレイ領域内に比して長く確保でき、耐圧を向上させることができる半導体装置を提供する。

【解決手段】セルアレイ領域の半導体基板14上には、第1の膜厚を持つトンネル酸化膜18、及び第1ゲート電極を有するメモリセルトランジスタが形成されている。周辺回路領域の半導体基板14上には、第1の膜厚より厚い第2の膜厚を持つゲート酸化膜を有する高電圧トランジスタが形成される。ワード線3は、メモリセルトランジスタの第1ゲート電極に接続され、ワード線引き出し領域の半導体基板14上に延伸している。ワード線引き出し領域において、半導体基板14とワード線3との間には、第1の膜厚より厚く、第2の膜厚より薄い第3の膜厚を持つシリコン酸化膜15が形成されている。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

同一ウェハ上に様々なトランジスタを集積するための方法および装置

【課題】メモリセルや、高電圧トランジスタや、高性能トランジスタなどの、異なるタイプのトランジスタを、同一基板上に形成することが可能なフラッシュメモリ等の半導体装置を提供する。

【解決手段】高電圧トランジスタは、誘電膜20で覆われた第1のポリシリコン層22により形成される。誘電膜20上の第2のポリシリコン層24は、トランジスタのゲート22上に側壁スペーサ24を形成するためにエッチングされる。側壁スペーサ24は、ソースおよびドレイン32を形成し、そして、サブリソグラフィックな軽度にドープされたドレイン34を画定するために使用される。スペーサ24を取り除いた後、下地の誘電膜20は、軽度にドープされたドレイン34を保護することができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】ISSG酸化法によるメモリ特性の劣化が生じにくい不揮発性半導体記憶装置を実現できるようにする。

【解決手段】不揮発性半導体記憶装置の製造方法は、以下の工程を備えている。メモリ領域101及び周辺トランジスタ領域102の上に、第1のゲート絶縁膜106及び第1の導電膜107を順次形成する工程(a)。第1の導電膜107及び第1のゲート絶縁膜106における周辺トランジスタ領域102の上に形成された部分を除去する工程(b)。メモリ領域101の上に第1の導電膜107が残存した状態においてISSG(in-situ steam generation)酸化を行い、周辺トランジスタ領域102の上に第2のゲート絶縁膜109を形成する共にメモリ領域101の上に残存する第1の導電膜107の上部に導電膜上酸化膜110を形成する工程(c)。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】フラッシュメモリ素子の製造方法を提供する。

【解決手段】セル領域及び周辺領域を含む半導体基板10を用意するステップと、半導体基板10のセル領域に第1ウェルを形成した上でONO膜を形成するステップと、第1ウェルを含む半導体基板10の周辺領域に第2ウェルを形成した上で第1酸化膜21を形成するステップと、第1ポリシリコン膜51を形成した後にONO膜パターン及び第1ポリシリコンパターン61から形成されたメモリゲートを形成するステップと、メモリゲートの両側壁に第2酸化膜パターン26及び第2ポリシリコンパターン62(残留パターン)を形成した上でゲートを形成するステップと、メモリゲートの片方側壁のみに残留パターンを残してセレクトゲートを形成するステップと、互いに隣接したメモリゲートの間の半導体基板10に第3不純物領域15を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

半導体記憶装置

【課題】動作信頼性を向上出来る半導体記憶装置を提供すること。

【解決手段】第1ゲート電極を備えた選択トランジスタST1、ST2と、電荷蓄積層と制御ゲートとを含む第2ゲート電極を備えたメモリセルトランジスタMTと、前記選択トランジスタST1、ST2間に前記メモリセルトランジスタMTが直列接続されたメモリセルユニット5とを具備し、前記第1ゲート電極同士の間隔、及び前記第1ゲート電極と前記第2ゲート電極の間隔は、前記第2ゲート電極同士の間隔の2倍以上であり、前記第2ゲート電極間における前記半導体基板12表面は、前記第1ゲート電極と前記第2ゲート電極間における前記半導体基板12表面と同一面にあり、前記第1ゲート電極間における前記半導体基板12表面は、前記第1ゲート電極と前記第2ゲート電極間における前記半導体基板12表面よりも低く位置する。

(もっと読む)

半導体メモリ

【課題】メモリセルの微細化と信頼性の向上とを図る。

【解決手段】本発明の例に係る半導体メモリは、アクティブエリアAA1,AA2,・・・と素子分離エリアとが第1方向に交互に配置される周期構造を備える。第1方向の最端部からm(mは2以上の数)番目以降のアクティブエリア上には、第1ゲート絶縁膜が形成され、第1方向の最端部からm番目未満のアクティブエリア上には、第1ゲート絶縁膜よりも厚い第2ゲート絶縁膜が形成される。素子分離絶縁膜は、第1方向の最端部からm−1番目とm番目のアクティブエリアの間に段差を有する。第1方向において、m−1番目とm番目のアクティブエリアの間の素子分離絶縁膜の幅は、m番目とm+1番目のアクティブエリアの間の素子分離絶縁膜の幅よりも広い。

(もっと読む)

半導体装置の製造方法

【課題】素子の微細化を図りつつ、セルトランジスタと選択ゲートトランジスタとの間に浅い拡散層が形成できる製造方法を提供する。

【解決手段】第1及び第2の領域における半導体基板1上にゲート絶縁膜4、第1のゲート電極層6、第1の絶縁膜7を順に形成し、第2の領域における第1の絶縁膜7の一部を除去して開口部9を形成し、第1の絶縁膜7上及び開口部9内に第2のゲート電極層10を形成し、第1及び第2のゲート電極層6、10、第1の絶縁膜7をパターニングし、半導体基板1内に不純物12を導入し、第2の絶縁膜、マスク層を順に形成し、第1の領域、第1及び第2の領域の間を覆いかつ第2の領域における第1及び第2の選択ゲートトランジスタ間を開口するようにマスク層をパターニングし、第1及び第2の選択ゲートトランジスタ間の第2の絶縁膜及びゲート絶縁膜を除去するとともに、この半導体基板1内に導入された不純物12を除去する。

(もっと読む)

121 - 140 / 403

[ Back to top ]