Fターム[5F103BB52]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出装置 (1,132) | 計測・監視部 (74) | 温度計測・監視 (15)

Fターム[5F103BB52]に分類される特許

1 - 15 / 15

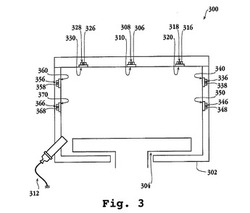

半導体用途での正確な温度測定

【課題】半導体製造プロセスの正確な温度測定技術を提供する。

【解決手段】温度検知要素により、正確なその場温度測定を可能にする。温度検知要素は、プロセスチャンバ302内に配置される。温度検知要素は、空洞306を有しており、空洞の開口部を覆うように透明カバー310が配置されている。材料308が、温度検知要素の空洞内に配置され、センサ312が、透明カバーを通して材料の相変化を検知するよう構成されている。

(もっと読む)

温度制御システム

【課題】従来に比べて精度よく処理対象物の温度を制御することができる温度制御システムを提供すること。

【解決手段】上面に処理対象物を載置可能とし、内部に温調媒体の流路が形成されたサセプタと、サセプタの上面に載置された処理対象物の温度を測定する温度測定手段と、流路を流れる温調媒体を温調する第1の温調手段と、サセプタと第1の温調手段との間に介在し、温度測定手段による測定結果に基づいて、温調媒体を温調する第2の温調手段と、を備える。

(もっと読む)

炭化珪素単結晶の製造装置および製造方法

【課題】SiC単結晶を成長させる際のドーパント濃度のバラツキを抑制する。

【解決手段】SiC原料粉末3とドーパント元素4の配置場所を異ならせると共に、SiC原料粉末3に対してドーパント元素4が種結晶2から離れた位置に配置されるようにする。そして、ドーパント元素4の配置場所をSiC原料粉末3の配置場所よりも低温にできる構成とする。これにより、SiC原料粉末3が昇華し始めるよりも前にドーパント元素4が気化し切ってしまうことを防止することができ、成長させたSiC単結晶のインゴットが成長初期にのみドーパントが偏析したものとなることを抑制できる。したがって、ドーパント濃度のバラツキを抑制できるSiC単結晶を製造することができる。

(もっと読む)

成膜装置及び成膜方法

【課題】 坩堝の側面に原料融液が這い上がった状態で成膜を行うと、形成された薄膜の厚さの均一性が低下してしまう。

【解決手段】 チャンバ内に基板ホルダが配置されている。坩堝の内部に蒸発源が収容される。坩堝の開口部が、基板ホルダに保持された基板に向けられている。第1の加熱装置が坩堝を加熱する。測定装置が、坩堝の深さの1/2の深さよりも浅い位置の、坩堝の温度に依存する物理量を測定する。回転機構が坩堝を回転させる。制御装置が、測定装置による測定結果に基づいて、回転機構を制御する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】薄膜トランジスタ用半導体層の材料として、高い正孔移動度を示すp形半導体多結晶薄膜を、かつ、低い成膜温度でのプラスチック基板上への成膜をも行うことのできるp形半導体多結晶薄膜を、提供する。

【解決手段】ガラスまたはプラスチックまたはステンレス基板のような非結晶質または多結晶基板1上に、該基板の温度を300℃以下とし、成長膜へのガリウム(Ga)、アンチモン(Sb)、及びヒ素(As)原子のそれぞれの供給量JGa,JSb,及びJAsを、JSb<JGa<JAs+JSbを満たすような値として、Ga,Sb,及びAs原子を同時供給して真空蒸着により成膜してなる、Sb組成yが0.5<y<1を満たすp形GaSbyAs1-y多結晶薄膜6を形成する製造方法による。

(もっと読む)

温度測定装置、薄膜形成装置、温度測定方法及び半導体装置

【課題】温度測定装置において、熱の影響を受けることなく、真空環境下において複雑に移動する被測定物の温度を正確に測定できるようにする。

【解決手段】装置本体31と、これを固定状態で収容する内装ケース33と、内面寸法が内装ケース33の外面寸法よりも大きく形成されて、内装ケース33との間に隙間が形成されるように内装ケース33を収容する外装ケース35と、外装ケース35の外側に配されると共に内装ケース33及び外装ケース35の挿通孔33c,35cを介して装置本体31に電気配線された温度計37と、外装ケース35内において内装ケース33を非接触状態で浮遊させる浮遊手段49とを備える温度測定装置5を提供する。

(もっと読む)

微細構造素子製造装置及び微細構造素子生産方法

【課題】領域選択成長技術を適用して、均一性のある微細構造を生産できる微細構造素子製造装置及び微細構造素子生産方法を提供すること。

【解決手段】基板が搭載される試料ホルダ40と、基板30に選択的に結晶を成長させるため基板の温度を所定の範囲に加熱する加熱器50と、基板30に選択的に結晶を成長させるための少なくとも1つ以上の第1の開口部と、当該1つ以上の第1の開口部の外側に複数の第2の開口部を有するマスク10と、マスク10が搭載されるマスクホルダ20と、を備える微細構造素子製造装置。

(もっと読む)

ZnO系薄膜及び半導体素子

【課題】意図しない不純物のドーピングが抑制されたZnO系薄膜及び半導体素子を提供する。

【解決手段】p型不純物を含むMgxZn1-xO(0≦x<1)からなり、原子間力顕微鏡による観測において、観測される六角形状のピットの密度が5×106個/cm2以下、又は底部に複数の微結晶の突起が形成された凹部が観測されない、の少なくともいずれかを満たす主面を備える。

(もっと読む)

基板温度計測装置及び基板温度計測方法

【課題】基板温度を高精度に計測可能な基板温度計測装置及び基板温度計測方法を提供する。

【解決手段】基板100を加熱する加熱源10と、基板100を透過できない波長領域の赤外線を透過させる透過窓30と、基板100を透過できない波長領域を感度範囲に含み、加熱源10により加熱された基板100から放射され、透過窓30を透過した赤外線を分析して基板100の基板温度を計測する温度計測器40とを備える。

(もっと読む)

熱処理装置及び熱処理方法

【課題】被処理物を急速昇温でき、熱効率及びスループットに優れるとともに、構成の簡素な熱処理装置を提供する。

【解決手段】高温真空炉は、被処理物を1,000℃以上2,400℃以下の温度に加熱する本加熱室21と、本加熱室21に隣接する予備加熱室22と、予備加熱室22と本加熱室21との間で被処理物を移動させるための移動機構27と、を備える。本加熱室21の内部には、被処理物を加熱するメッシュヒータ33と、メッシュヒータ33の熱を被処理物に向けて反射するように配置される第1多層熱反射金属板41と、が備えられる。移動機構27は、被処理物とともに移動可能な第2多層熱反射金属板42を備える。被処理物が予備加熱室22内にあるときには、第2多層熱反射金属板42が本加熱室21と予備加熱室22とを隔てて、メッシュヒータ33の一部が第2多層熱反射金属板42を介して予備加熱室22に供給される。

(もっと読む)

半導体基板温度測定装置およびこれを含む半導体デバイス製造装置、並びに、半導体基板の温度測定方法および半導体デバイスの製造方法

【課題】半導体基板の温度を高精度かつ高い再現性で測定する。

【解決手段】本発明に係る半導体基板温度測定装置を含む半導体デバイス製造装置であるMBE装置20は、半導体基板の温度を測定する半導体基板温度測定装置において、基板2において散乱された散乱光のスペクトルに基づき、基板2の温度を算出する基板温度演算装置11を備え、基板温度演算装置11は、散乱光のスペクトル基づき算出した基板2の温度を、基板2のドーパント濃度に基づいて補正する。

(もっと読む)

ZnO系薄膜

【課題】基板上にZnO系薄膜を形成する場合に、平坦な膜を成長させるためのZnO系薄膜を提供する。

【解決手段】 図1(a)では、ZnO系基板1上にZnO系薄膜2が形成されている。また、図1(b)では、ZnO系基板1上に、ZnO系薄膜の積層体であるZnO系積層体10が形成されている。ZnO系積層体10は、ZnO系半導体層3やZnO系半導体層4等の複数のZnO系半導体層が積層された積層体である。ZnO系薄膜2やZnO系積層体10を形成する場合には、成長温度750℃以上で成長させるか、又は、膜表面の粗さが所定の範囲になるように、膜表面のステップ構造が所定の構造となるように形成する。

(もっと読む)

分子線エピタキシャル装置の制御装置、分子線エピタキシャル装置、分子線エピタキシャル装置の制御方法、分子線エピタキシャル装置制御プログラム、およびコンピュータ読み取り可能な記録媒体

【課題】同一の分子線材料を有する分子線セルを複数有する分子線エピタキシャル装置の稼動率を向上させ、かつ、成膜において高い再現性を実現する、分子線エピタキシャル装置の制御装置を提供する。

【解決手段】分子線エピタキシャル装置100の制御装置118は、同一の分子線材料105を有する複数の分子線セル107について、各分子線セル107内の分子線材料105の残量を求める残量算出部405と、次回の成膜における各層での同一の分子線材料105の合計の消費量を等しくしたまま、上記各分子線セル107における設定を変更したものについて、次回の成膜後の当該各分子線セル107に残存する分子線材料105の予測消費時間を算出する予測消費時間算出部406と、上記予測消費時間の差が小さくなるように、次回の成膜での上記各分子線セル107における設定を決定するセル設定決定部407とを備えている。

(もっと読む)

立方晶III族窒化物自立バルク基板およびその製造方法

a)分子線エピタキシ法(molecular beam epitaxy:MBE)を用いて、立方晶III-V族基板上にエピタキシャルIII族窒化物材料を成長させるステップと、b)前記III族窒化物基板が立方晶III族窒化物自立基板として残るように、前記III-V族基板を除去するステップと、を含む立方晶III族窒化物自立バルク基板の製造方法。III族窒化物デバイスの製造のための立方晶III族窒化物自立バルク基板。 (もっと読む)

気相成長方法

FeドープInP等の半導体基板上にInAlAs等の化合物半導体からなるエピタキシャル層を再現性よく成長させることのできる気相成長方法を提供する。

半導体基板上にエピタキシャル層を成長させる気相成長方法において、予め室温における半導体基板の抵抗率を測定し、該半導体基板の抵抗率に関わらず実際の基板の表面温度が所望の温度となるように、前記室温における抵抗率に応じて基板の設定温度を制御し、エピタキシャル層を成長させるようにした。

(もっと読む)

1 - 15 / 15

[ Back to top ]