Fターム[5F110AA02]の内容

Fターム[5F110AA02]に分類される特許

121 - 140 / 412

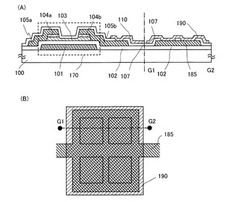

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

バルクFinFET中のSiフィンのフィン下部近くのSTI形状

【課題】半導体フィンとフィン型電界効果トランジスタの構造、及び、製造方法を提供する。

【解決手段】集積回路構造の形成方法は、頂面を有する半導体基板を提供するステップと、半導体基板中に、第1絶縁領域と第2絶縁領域を形成するステップと、第1絶縁領域と第2絶縁領域を陥凹するステップと、からなる。第1絶縁領域と第2絶縁領域の残り部分の頂面は平らな表面であるか、或いは、窪み表面である。第1絶縁領域と第2絶縁領域の除去部分間の半導体基板の部分、及び、隣接する部分は、フィンを形成する。

(もっと読む)

異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成

【課題】異なる誘電材料を用いたインター装置STI領域とイントラ装置STI領域の形成を提供する。

【解決手段】集積回路構造は、第1装置領域に第1部分、第2装置領域に第2部分を有する基板と、第1装置領域中で、且つ、基板上に位置する2つの絶縁領域と、からなる。2つの絶縁領域は、第1k値を有する第1誘電材料を含む。半導体ストリップは、2つの絶縁領域間に位置し、且つ、2つの絶縁領域に隣接し、2つの絶縁領域の頂面上に、半導体フィンを形成する半導体ストリップの上部分を有する。追加の絶縁領域が、第2装置領域中で、且つ、基板上に位置する。追加の絶縁領域は、第1k値より大きい第2k値を有する第2誘電材料を含む。

(もっと読む)

半導体デバイスおよび表示装置

【課題】オン抵抗を犠牲にしないで寄生容量とリーク電流のトレードオフを解消または緩和する。

【解決手段】TFT部10Bは、2つのソース・ドレイン電極18,19が、半導体膜15の平面視でチャネル形成領域を挟んで位置する一方と他方の半導体領域に接する。ソース・ドレイン電極18,19は、半導体膜15と接する領域(斜線部)の当該ソース・ドレイン電極の輪郭部分30において、その両端のエッジポイント31の各々が、平面視でゲート電極13の外側に位置している。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上させる。

【解決手段】同一基板上に第1の薄膜トランジスタを有する駆動回路及び第2の薄膜トランジスタを有する画素を有し、前記第1の薄膜トランジスタは、第1のゲート電極層と、ゲート絶縁層と、第1の酸化物半導体層と、第1の酸化物導電層及び第2の酸化物導電層と、前記第1の酸化物半導体層の一部に接し、且つ前記第1の酸化物導電層及び前記第2の酸化物導電層の周縁及び側面に接する酸化物絶縁層と、第1のソース電極層と、第1のドレイン電極層と、を有し、前記第2の薄膜トランジスタは、第2のゲート電極層と、第2の酸化物半導体層と、透光性を有する材料により構成された第2のソース電極層及び第2のドレイン電極層と、を有する。

(もっと読む)

発光装置およびその作製方法

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複数種の薄膜トランジスタを備えた発光装置を提供することを課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャネルストップ型を用い、画素用薄膜トランジスタと電気的に接続する発光素子と重なる位置にカラーフィルタ層を薄膜トランジスタと発光素子の間に設ける。

(もっと読む)

半導体装置およびその作製方法

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】酸化物半導体層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、該酸化物絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。また、チャネル保護層に重ならないようにソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層上の絶縁層が酸化物半導体層と接する構成とする。

(もっと読む)

半導体装置およびその作製方法

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層と、ゲート電極層上に設けられるゲート絶縁層と、ゲート絶縁層上に設けられる第1の酸化物半導体層と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】ボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部にチャネル保護層となる酸化物絶縁層を形成し、その酸化物絶縁層の形成時に酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。酸化物半導体層の周縁部(側面を含む)を覆う酸化物絶縁層は、ゲート電極層と、その上方または周辺に形成される配線層(ソース配線層や容量配線層など)との距離を大きくし、寄生容量の低減を図る。酸化物半導体層の周縁部を覆う酸化物絶縁層は、チャネル保護層と同一工程で形成されるため、工程数の増加なく、寄生容量を低減できる。

(もっと読む)

表示装置およびその製造方法

【課題】製造工数の増大をもたらすことなく、薄膜トランジスタのゲート絶縁膜と容量素子の誘電体膜を異なる層における絶縁膜を用いることによって、それらの特性に応じた膜厚に設定できる表示装置の提供。

【解決手段】基板上に薄膜トランジスタと容量素子が形成されている表示装置にであって、前記薄膜トランジスタは、

ゲート電極の形成領域を被って形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成され、平面的に観て、前記ゲート電極の形成領域内に開口を備える第2の絶縁膜と、

前記第2の絶縁膜上に前記開口を横切って形成され、両端に高濃度領域を備える島状の多結晶化された半導体層と、

前記半導体層の上面に前記半導体層の両端の高濃度領域のそれぞれの一部を露出させて形成された第3の絶縁膜と、

前記第3の絶縁膜から露出された前記半導体層の両端の高濃度領域のそれぞれに電気的接続がなされて形成された一対の電極と、を備えて構成され、

前記容量素子は、その誘電体膜が前記第3の絶縁膜と同層で同材料の絶縁膜によって構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 酸化物半導体においてはイオン注入法による拡散層形成が難しいため、バルクシリコンMOSトランジスタや多結晶シリコンTFTのようなイオン注入法を用いた自己整合プロセスを組むことができない。本願では、リフトオフを用いる場合のような不都合の生じない自己整合プロセスを酸化物半導体において実現することを課題とする。

【解決手段】 裏面露光により製造される薄膜トランジスタ(TFT)において、チャネル層として酸化物半導体を用い、基板上の電極をマスクとして、基板の裏面側から導電膜上のネガレジストを露光し、ネガレジストの露光部分を残し前記ネガレジストを除去し、露光部分をエッチングマスクとする導電膜のエッチングにより、電極を加工する。

(もっと読む)

半導体装置

【課題】SOI基板に形成されたMOSトランジスタの高耐圧化、低消費電流、かつ高速動作を実現する。

【解決手段】シリコン層1cに、埋め込み酸化膜1bに達する深さで、N型の低濃度ドレイン領域3、ソース領域5、ドレインオーミック領域7、及びP型のチャンネル領域9、オーミックチャンネル領域11が形成されている。低濃度ドレイン領域3は表面側に配置されているものほど濃いN型不純物濃度をもつ2層の低濃度ドレイン層3a,3bで形成されている。チャンネル領域9は表面側に配置されているものほど薄いP型不純物濃度をもつ2層のチャンネル層9a,9bで形成されている。ゲート電極15は、チャンネル領域9上と低濃度ドレイン領域3の一部分の上に、上方から見てオーミックドレイン領域7とは間隔をもって配置されている。

(もっと読む)

半導体装置

【課題】半導体装置において、半導体層(活性層)全域の電位を固定し、電位を安定させる。

【解決手段】半導体装置1は、SOI(Silicon On Insulator)基板2にLDMOSFET(Lateral DoubleDiffused MOSFET:横型2重拡散MOSFET)3aが形成されている。LDMOSFET3aは、SOI基板2の半導体層13に形成されたn型ドレイン領域21とp型ソース領域31とを含んでいる。n型ドレイン領域21は、半導体層13の中央部に配置されており、p型ソース領域31は、半導体層13の端縁部にまで配置(延設)されている。これにより、半導体層13の全ての領域が、LDMOSFET3aのソース電極42aとドレイン電極41aのいずれかと接続された構造となり、半導体層13の全ての領域で電位が固定されることになり、半導体層13の全ての領域で電位が安定する。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】素子破壊を低減し、高耐圧で信頼性の高い横型MOSFET法を提供する。

【解決手段】半導体基板と前記半導体基板上に絶縁層を介して形成された第1導電型の半導体層とを有するSOI基板に形成され、前記第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、前記ウェル内および前記第1導電型の前記活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、前記活性領域のうちチャネル領域となる表面にゲート絶縁膜を介して形成されるゲート電極が、厚い絶縁膜上に乗り上げるように形成されるとともに、前記ゲート電極が乗り上げた厚い絶縁膜下には、前記活性領域の濃度よりも高濃度の第1導電型の拡散領域が形成される。

(もっと読む)

121 - 140 / 412

[ Back to top ]