Fターム[5F110AA02]の内容

Fターム[5F110AA02]に分類される特許

81 - 100 / 412

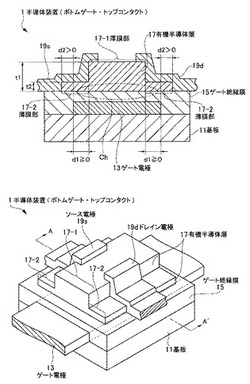

半導体装置、表示装置、および電子機器

【課題】トップコンタクト構造において、有機半導体層の膜質を確保しつつチャネル領域に対するコンタクト抵抗(注入抵抗)の低減を図る。

【解決手段】有機半導体層17は、ゲート電極13を幅方向に覆う状態で配置されており、ゲート電極13の幅方向の中央部に配置された厚膜部17−1と、この厚膜部17−1よりも薄い膜厚を有してゲート電極13の幅方向の両端に配置された薄膜部17−2とを有する。またソース電極19sおよびドレイン電極19dは、有機半導体層17の薄膜部17−2上に端部が積層される。有機半導体層17は、厚膜部17−1が前記ゲート電極13の幅の範囲内に設けられる一方、薄膜部17−2は、厚膜部17−1からゲート電極13の幅方向の外側に延設される。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

表示装置

【課題】画素部の薄膜トランジスタにおけるゲート・ソース間容量のばらつきを抑制することが可能な技術を提供する。

【解決手段】画素の領域毎に形成される画素電極PXと、画素電極を駆動する薄膜トランジスタとを備える表示装置において、薄膜トランジスタは、対角位置に形成される第1の角部B及び第2の角部Cと、前記第1の角部Bが形成される第1の辺と前記第2の角部Cが形成される第2の辺とを共有する第3の角部とを有し、ゲート絶縁膜を介して前記ゲート線GLに接続されるゲート電極と重畳して形成される半導体層ASと、前記ドレイン線DLからその一部が延在して形成され、前記第3の角部と重畳されるドレイン電極DTと、一端が前記第1の角部Bに重畳して形成され、他端が前記画素電極と接続される第1のソース電極ST1と、一端が前記第2の角部Cと重畳して形成され、他端が前記画素電極PXと接続される第2のソース電極ST2と、を有する。

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】層間絶縁膜に起因する不良を抑え、セルフアライン構造の薄膜トランジスタの信頼性を向上させることが可能な薄膜トランジスタおよびこれを備えた表示装置を提供する。

【解決手段】酸化物半導体膜20に接して、有機樹脂膜51を含む層間絶縁膜50を設ける。層間絶縁膜50の厚みを厚くして、ゲート絶縁膜30およびゲート電極40の段差を確実に被覆し、ソース電極60Sおよびドレイン電極60Dの断線あるいは短絡など、層間絶縁膜50に起因する不良を抑える。層間絶縁膜50は、有機樹脂膜51および第1無機絶縁膜52の積層構造を有していることが好ましい。酸素や水分などに対するバリア性の高い第1無機絶縁膜51により、酸化物半導体膜20への水分の混入や拡散を抑え、薄膜トランジスタ1の信頼性を向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減を通じて、出力容量Cossの低減に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、活性領域のうち、ドレイン領域にコンタクトするように形成されるドレインパッド形成領域9p下の少なくとも一部は、SOI基板の絶縁膜に到達するように形成された絶縁性領域11で構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 バーズビークの増大を抑制し、小型で信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】 そこで本発明の半導体装置の製造方法は、半導体基板と前記半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETの製造方法であって、活性領域のうち、素子領域を除く領域を不活性化し、不活性化領域(絶縁性領域14)を形成する工程を含み、不活性化領域を形成する工程が、活性領域に対し、所定間隔を隔てて所定幅の小トレンチを形成する工程と、小トレンチを囲む領域の活性領域3を酸化し、小トレンチTsが酸化膜で覆われるとともに、隣接する小トレンチまで酸化膜が到達するように酸化する工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

電気光学ディスプレイ

【課題】電気光学ディスプレイを提供する。

【解決手段】電気光学ディスプレイは、基板100と、該基板100の実質的に1つの面に配置された非線形デバイス102と、該非線形デバイス102と接続されている画素電極106と、電気光学媒体110と、該画素電極106に対して該電気光学媒体110の反対面上の共通電極112とを備える。該ディスプレイの様々なパーツの係数は、該ディスプレイが湾曲しているとき、中立軸または中立面が該非線形デバイス102の該平面に実質的に横たわっているように調製されている。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体構造体及びその製造方法

【課題】 埋め込み型DRAM構造のための半導体構造体及びその製造方法を提供する。

【解決手段】 ノード誘電体及び深いトレンチを充填する導電性トレンチ充填領域がセミコンダクター・オン・インシュレータ(SOI)層の上面とほぼ同一面となる深さにまで窪まされる。浅いトレンチ分離部が深いトレンチの上部の一方の側に形成され、一方深いトレンチの上部の他方の側は、導電性充填領域の半導体材料の露出された表面となる。選択的エピタキシャル成長プロセスが、レイズド・ソース領域及びレイズド・ストラップ領域を付着するために行われる。レイズド・ソース領域は、SOI層内のプレーナ・ソース領域上に直接形成され、そしてレイズド・ストラップ領域は、導電性充填領域上に直接形成される。レイズド・ストラップ領域は、プレーナ・ソース領域及び導電性充填領域の間の導電性通路を与えるためにレイズド・ソース領域に接触する。

(もっと読む)

半導体素子

【課題】垂直に形成されたナノワイヤを構成要素として備える半導体素子の寄生容量増加を抑制し、動作速度時定数が改善される半導体素子を提供する。

【解決手段】導電性基板101の主平面と電極109間の層間絶縁膜を膜厚調整層102と保護絶縁層103の2層化することにより、膜密着性の乏しい低誘電率膜102と電極109を保護絶縁層103で隔てることによってはがれを抑制しながら、主平面101と電極109間を電気的に接続するナノワイヤ107と、導電性基板101と電極109の間の寄生容量を低減する。

(もっと読む)

トランジスタ

【課題】ソース電極(ドレイン電極)と、ゲート電極との重畳部に生じる寄生容量値を低減させても、オン電流値をほぼ維持できる新たな電極構造のトランジスタを提供することを課題の一とする。

【解決手段】トランジスタのソース電極及びドレイン電極の電極形状を櫛歯形状にすることによって寄生容量値を低減させる。また、櫛歯状電極の先端部の幅や、電極歯部間の間隔を制御することによって、電極歯部の側面から流れる曲線電流を発生させることができる。この曲線電流が、電極形状を櫛歯形状にすることにより減少する直線電流を補うため、寄生容量値を低減させても、低減させる前とほぼ変わらないオン電流値を維持させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置

【課題】信号経路に挿入されたフローティングボディ型のトランジスタを用いて高速動作と低消費電力動作が可能な半導体装置を提供する。

【解決手段】本発明の半導体装置において、フローティングボディ型のトランジスタQ10は、センスアンプの出力ノードNS(第1の回路ノード)とローカル入出力線LIO(第2の回路ノード)との間に挿入されている。トランジスタQ10のゲートにカラム選択信号YS(第1の信号)が供給され、カラム選択信号YSがトランジスタQ10を非導通に保つ第1の論理レベルと導通方向に導く第2の論理レベルとの間で変化する。トランジスタQ10を利用しない回路状態時に、第2の論理レベルに近い第1及び第2の電圧レベルが出力ノードNS及びローカル入出力線LIOに供給される。これにより、フローティングボディ型のトランジスタQ10のCV特性を適切に制御し、ゲート容量を抑制することができる。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

アクティブマトリクス型駆動基板、その製造方法及び表示装置

【課題】電子ペーパー等の表示装置に適用した場合に、その消費電力を小さくでき、歩留まりを向上させることができるアクティブマトリクス型駆動基板及びその製造方法等を提供する。

【解決手段】第1絶縁膜2を表面に有する導電基材1上に設けられた薄膜トランジスタ10及び保持容量20と、薄膜トランジスタ10及び保持容量20を第2絶縁膜16,17を介して覆う画素電極30を有し、保持容量20が第1電極21と誘電体膜22と薄膜トランジスタ10のソース・ドレイン電極14,15に接続する第2電極23との積層体であるアクティブマトリクス型駆動基板50であって、導電基材1と第1電極21とが第1絶縁膜2の開口部4で接続されているように構成する。第2絶縁膜(16,17)が少なくとも層間絶縁膜17を有し、導電基材1が金属基材であり、第1絶縁膜2が金属基材1の表面粗さを低減する平坦化膜であることが好ましい。

(もっと読む)

半導体装置

【課題】回路ブロックを構成するMOS型トランジスタを同一構造にしたまま駆動電圧を下げ、消費電力を低くすることができる複数の回路ブロックから構成される半導体装置の提供。

【解決手段】本半導体装置の構造は、消費電力を低くしたい回路ブロック11が設けられている半導体基板14の厚さ19を薄くすることにより、MOS型トランジスタの閾値を小さくでき、駆動電圧を下げ、所望の回路ブロックの消費電力を下げることができる。

(もっと読む)

液晶表示装置

【課題】液晶表示装置が有する信号線の寄生容量を低減すること。

【解決手段】各画素に設けられるトランジスタとして、酸化物半導体層を具備するトランジスタを適用する。なお、当該酸化物半導体層は、電子供与体(ドナー)となる不純物(水素又は水など)を徹底的に除去することにより高純度化された酸化物半導体層である。これにより、トランジスタがオフ状態のときのリーク電流(オフ電流)を少なくすることができる。そのため、各画素において容量素子を設けずとも液晶素子に印加される電圧を保持することが可能になる。また、これに付随して、液晶表示装置の画素部に延在する容量配線を削除することが可能になる。そのため、信号線と容量配線が立体交差する領域における寄生容量を削除することが可能になる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた高性能な半導体装置を提供する。

【解決手段】基板上に酸化物半導体層を形成し、酸化物半導体層上に第1の導電層を形成し、第1の導電層上に第2の導電層を形成し、第2の導電層をエッチングすることで、第1のパターンを形成し、第1のパターンを酸化することにより膨張させ、膨張後の第1のパターンをマスクとして第1の導電層をエッチングすることで、ソース電極及びドレイン電極となる第2のパターンを形成し、膨張後の第1のパターン及び第2のパターン及び酸化物半導体層を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する。

(もっと読む)

81 - 100 / 412

[ Back to top ]