Fターム[5F110GG22]の内容

Fターム[5F110GG22]に分類される特許

201 - 220 / 1,535

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

フィンを含む半導体構造およびその形成方法

【課題】フィン高さの改良を図れるフィンの形成方法を提供すること。

【解決手段】実施形態のフィン形成の方法は、まず、半導体基板上に多層構造を形成する。前記半導体構造は、前記半導体基板上の第1の層、前記第1の層上の第2の層および前記第2の層上の第3の層を具備する。次に、前記半導体基板および前記半導体構造の複数の部分からなる複数のフィンを形成するために、前記半導体基板の複数の上部および前記半導体構造の複数の部分を除去する。次に、前記第2の層および前記第3の層の酸化速度を前記第1の層よりも酸化速度よりも小さくしながら、前記第1の層を選択的に酸化する。次に、前記選択的な酸化の後に前記複数のフィン間の空隙を絶縁材料で充填する。そして、フィンを露出させるために少なくとも前記絶縁材料の一部をリセスし、前記フィンの少なくとも一つの側面または前記フィンの上面をチャネル領域にする。

(もっと読む)

薄膜トランジスタ、表示装置および電子機器

【課題】動作速度を簡易に向上させることが可能な薄膜トランジスタ、ならびにそのような薄膜トランジスタを用いた表示装置および電子機器を提供する。

【解決手段】薄膜トランジスタ1は、ゲート電極141と、チャネルを構成するキャリア走行層121とこのキャリア走行層121へキャリアを供給するためのキャリア供給層122とを含む多層膜からなる酸化物半導体層12と、ゲート電極141と酸化物半導体層12との間に設けられたゲート絶縁膜131と、ソース・ドレイン電極16A,16Bとを備えている。酸化物半導体層12におけるソース・ドレイン領域12SDとゲート電極141の形成領域とは、互いに離隔している。従来のような複雑な構造を形成することなく、キャリアに対する走行散乱およびチャネルに対するアクセス抵抗を抑えてキャリアの移動度を向上させることができると共に、寄生容量の形成も回避することができる。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

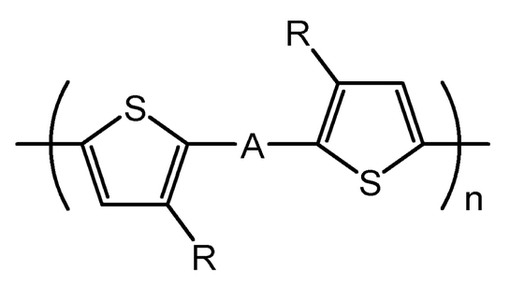

半導体組成物

【課題】高い移動度を示し、高い電流オン/オフ比を示す薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、下式のポリチオフェンとカーボンナノチューブとを含む半導体層を有する。

式中、Aは、二価の結合であり;各Rは、水素、アルキル、アルケニル等から選択され;nは、2〜約5,000である。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのスイッチング速度を高速化した半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁層の一部上に形成された半導体層10と、半導体層10の側面10aに形成され、第1のゲート絶縁膜21、第1のゲート電極22、並びにソース及びドレインとなる2つの第1の不純物層23,24を有する第1のトランジスタ20と、半導体層10の側面10bに形成され、第2のゲート絶縁膜31、第2のゲート電極32、並びにソース及びドレインとなる2つの第2の不純物層33,34を有する第2のトランジスタ30とを具備する。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

表示装置

【課題】光電変換素子を含む表示装置において、生産性および利便性に優れた表示装置を提供する。

【解決手段】複数の画素がマトリクス状に配列された表示部と、表示部に画像情報を伝送する駆動部と表示部に設けられ、且つレーザ光を検出する受光部と、受光部で検出するレーザ光の位置を解析し、位置に基づいて画像情報を操作し、操作に基づいた画像情報とは異なる画像情報を駆動部に伝送する情報処理部を有し、表示部の複数の画素はそれぞれ薄膜トランジスタを有し、受光部は複数の光電変換素子、走査回路、リセット回路および読み出し回路を有し、薄膜トランジスタおよび複数の光電変換素子は、同一の基板に設けられている表示装置である。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

表示素子の製造方法

【課題】安定した電流駆動能力を発揮させる。

【解決手段】アレイ基板20の製造方法は、基板上にゲート電極24aを形成するゲート電極形成工程と、ゲート電極24a上に不純物を含有するゲート絶縁膜24b、半導体膜SM、導電膜COの順で成膜する成膜工程と、導電膜CO上にレジストRSを塗布し、そのレジストRSに対してフォトマスクを介して露光を行った後に現像を行うことでレジストRSをパターニングするレジストパターニング工程と、パターニングされたレジストRSをマスクとして導電膜COをエッチングすることで開口領域OPを挟んで配されるソース電極24d及びドレイン電極24eを形成する導電膜パターニング工程と、開口領域OPから半導体膜SMを介してゲート絶縁膜24bに含有される不純物を脱離させる不純物脱離工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果による電気特性の変動が生じにくい、チャネル領域に酸化物半導体を含むトランジスタを用いた半導体装置を作製する。

【解決手段】窒素を含む一対の酸窒化物半導体領域、および該一対の酸窒化物半導体領域に挟まれる酸化物半導体領域を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体領域上に設けられるゲート電極とを有する半導体装置。ここで、一対の酸窒化物半導体領域はトランジスタのソース領域およびドレイン領域となり、酸化物半導体領域はトランジスタのチャネル領域となる。

(もっと読む)

薄膜トランジスタ

【課題】 結晶性に優れ、電気特性、特にリーク電流の少ない結晶性シリコン薄膜半導体装置を提供する。

【解決手段】 ソース電極およびドレイン電極上に非晶質シリコン層を形成し、その上に微結晶シリコン層、ゲート絶縁層、ゲート電極を形成する薄膜トランジスタであって、前記非晶質シリコン層と前記ソース電極とドレイン電極とが前記微結晶シリコン層を介して接続する領域と、前記非晶質シリコン層と前記ソース電極およびドレイン電極と直接接続する領域と、を有する。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体8をドライエッチングして形成した平坦表面に電極を形成してもオーミック接触させることができない。

【解決手段】p型III族窒化物半導体8の電極形成範囲をドライエッチングして溝8dを形成し、その溝8dに金属20を充填して電極を形成する。p型III族窒化物半導体8のドライエッチング面は、エッチングによって生じた欠陥によってn型化しているために、平坦平面にドライエッチングしておいて電極を形成するとオーミック接触しない。溝8dを設けておくと、欠陥が少ない溝8dの側面においてp型III族窒化物半導体8と電極がオーミック接触し、半導体と電極の接触抵抗が低減する。

(もっと読む)

半導体装置及び表示装置

【課題】高融点メタルバリア層を有していなくても、高温熱処理後の電気特性を良好にする技術を提供することを目的とする。

【解決手段】半導体装置は、透明絶縁性基板1上に形成されたゲート電極2と、ゲート電極2上にゲート絶縁膜6を介して順次に形成されたSi半導体能動膜7と、n型の導電型を有するオーミック低抵抗Si膜8とを含む半導体層51と、半導体層51と直接接合された、少なくともアルミニウム(Al)を含むソース・ドレイン電極9,10とを備える。半導体層51は、平面視においてゲート電極2の外周よりも内側に形成され、Si半導体能動膜7の側面とソース・ドレイン電極9,10との界面近傍である第1領域には、少なくとも窒素(N)が含まれる。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】高性能な電気特性を実現しうるpoly−Si膜の結晶性分布を有した薄膜トランジスタおよびその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタは、絶縁性の基板と、前記絶縁性基板の上に形成されたゲート電極と、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜の上に形成された結晶シリコン膜と、前記結晶シリコン膜の端部の上方に形成されたソース電極と、前記結晶シリコン膜における前記ソース電極が形成された端部と対向する端部の上方に形成され、前記ソース電極と離間しているドレイン電極とを具備する薄膜トランジスタにおいて、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されている前記結晶シリコン膜の端部から、前記結晶シリコン膜におけるソース電極又はドレイン電極が形成されていない前記結晶シリコン膜の中央部に向かって、前記結晶シリコン膜の結晶化率が小さくなっている。

(もっと読む)

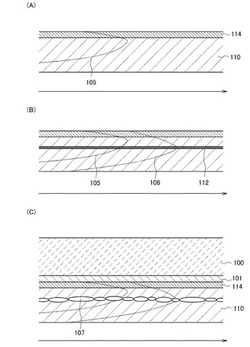

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】混相粒の粒径の均一性が高く、且つ結晶性の高い微結晶半導体膜を作製する。または、電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】粒径の均一性が高く、且つ高い結晶性を有する混相粒を低い粒密度で与える第1の条件により、非晶質シリコン領域と、単結晶とみなせる微小結晶である結晶子とを含む混相粒を有する種結晶を絶縁膜上にプラズマCVD法により形成した後、当該種結晶上に、混相粒を成長させて混相粒の隙間を埋める第2の条件で、種結晶上に微結晶半導体膜をプラズマCVD法により積層形成する。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

201 - 220 / 1,535

[ Back to top ]