Fターム[5F110GG36]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | チャネル領域の不純物 (5,796) | 不純物の分布 (414)

Fターム[5F110GG36]の下位に属するFターム

一導電型不純物のみ (175)

Fターム[5F110GG36]に分類される特許

221 - 239 / 239

非晶質酸化物、及び電界効果型トランジスタ

【課題】TFTの活性層等に適用できる新規な非晶質酸化物を提供する。

【解決手段】非晶質酸化物が微結晶を含む、又は層厚方向に組成が変化していること、又は所定の材料を含むことを特徴とする。

(もっと読む)

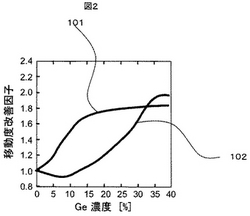

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程に新たな専用工程の追加を伴うことなく、オン抵抗と降伏電圧とのトレードオフの関係(相反関係)を打破して、オン抵抗を低く維持しながら降伏電圧(耐圧)を高めることのできる半導体装置およびその製造方法を提供する。

【解決手段】チャネルとなる不純物領域、すなわちチャネル領域P11についてはこれを、ゲート電極14の直下にあたる部分の不純物濃度が選択的に高められた濃度分布をもつものとし、ドレインとなる不純物領域、すなわちドレイン領域N12についてはこれを、配線とのコンタクト部分(ドレイン層N12b)を除く全域にわたって均一な濃度分布をもつものとする。さらに、チャネル領域P11の近傍にLOCOS酸化膜12を設け、チャネル領域P11に隣接してLOCOS酸化膜12のチャネル側端辺に電流経路を形成するようなドリフト層N12aを形成する。

(もっと読む)

液晶表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する液晶表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な液晶表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い液晶表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流を効果的に低減し、電気特性の向上を図ることである。

【解決手段】 半導体装置は、半導体層40と、半導体層40の上方に設けられたゲート絶縁層50と、ゲート絶縁層50の上方に設けられたゲート電極60と、半導体層40におけるゲート電極60から露出する領域に形成され、ソース領域又はドレイン領域を構成する第1の不純物領域70,72と、半導体層40におけるゲート電極60から露出する領域に形成され、第1の不純物領域70,72とは異なる導電型からなる第2の不純物領域80,82と、を含む。ゲート電極60の少なくとも一方の端部62は、半導体層40の第1及び第2の端面42,44を被覆している。半導体層40の第1の端面42の一方に隣接して第1の不純物領域70が配置され、半導体層40の第1の端面42の他方に隣接して第2の不純物領域80が配置されている。

(もっと読む)

結晶方向の異なるシリコン層を備えたシリコン−オン−インシュレータ半導体デバイスと、シリコン−オン−インシュレータの半導体デバイスを形成する方法

第1の結晶方位を有する基板12と、この基板12を覆う絶縁層40を含む半導体デバイスが提供される。この絶縁層を覆って、複数のシリコン層16、30が形成される。第1シリコン層16は、第1の結晶方位を有するシリコンを含み、第2シリコン層30は、第2の結晶方位を有するシリコンを含む。加えて、基板12と、この基板12を覆うシリコン層16と、基板12とシリコン層16と間に設けられた第1絶縁層14を含むシリコン−オン−インシュレータ構造を提供する半導体デバイスを形成する方法が提供されている。シリコン層16および第1絶縁層14の一部を取り除くことでシリコン−オン−インシュレータ構造の第1領域を形成し、基板層12の一部24をさらす。選択的エピタキシャルシリコン30は、開口部に成長される。開口部22で成長されたシリコン30に第2絶縁層40が形成され、開口部22で成長されたシリコン30と基板12との間に絶縁層40が提供される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 トランジスタの信頼性の劣化を抑制しつつ、高電圧駆動を可能とするとともに高速化を図る。

【解決手段】 酸化防止膜4をマスクとしてエピタキシャル成長を行うことにより、第1単結晶半導体層3上に第2単結晶半導体層5を形成し、酸化防止膜4をマスクとして第2単結晶半導体層5の熱処理を行うことにより、第2単結晶半導体層5の構成成分を第1単結晶半導体層3内に拡散させ、第1単結晶半導体層3の一部を第3単結晶半導体層7に変換した後、第1単結晶半導体層3上および第3単結晶半導体層7上に第4単結晶半導体層8を形成し、第3単結晶半導体層7上に配置された第4単結晶半導体層8上にゲート絶縁膜11を形成するとともに、オフセットゲート層15bおよびドレイン層15cを第1単結晶半導体層3および第4単結晶半導体層8に形成する。

(もっと読む)

直列接続されたトランジスタ列を組込んだプログラマブルメモリアレイ構造およびこの構造を製造して作動させるための方法

三次元フラッシュメモリアレイは、直列接続されたNAND列に電荷蓄積誘電体が配置された薄膜トランジスタを組込んで、4F2のメモリセルのレイアウトを達成する。各NAND列はそれぞれ、グローバルビット線にNAND列の一方端を結合し、共有されたバイアスノードに他方端を結合するための2つのブロック選択デバイスを含む。ブロック内のNAND列の対は、同じグローバルビット線を共有する。メモリセルは、ブロック選択デバイスと同様に、好ましくはデプリーションモードのSONOSデバイスである。メモリセルは、デプリーションしきい値電圧付近にプログラミングされ得、ブロック選択デバイスは、デプリーションモードのしきい値電圧付近の電圧を有するプログラム状態に維持される。2つ以上の層上のNAND列は、1つの層上のグローバルビット線に接続され得、好ましくは、垂直方向の積層型ビアにより、ともに接続され得る。  (もっと読む)

(もっと読む)

犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【課題】 犠牲スペーサを利用して歪みチャネル電界効果トランジスタを製造するための構造体及び方法

【解決手段】 ゲート積層体(29)と、ゲート積層体(29)の側壁上に配置される1対の第1のスペーサ(32)と、ゲート積層体(29)の両側に配置され、それから第1の間隔を置かれる1対の半導体合金領域(39)とを含む電界効果トランジスタ(FET)(10)が提供される。FET(10)のソース及びドレイン領域(24)は少なくとも部分的に半導体合金領域(39)内に配置され、1対の第1のスペーサ(32)の対応するスペーサによってゲート積層体(29)から、第1の間隔とは異なり得る第2の間隔を置かれる。FET(10)はまた、第1のスペーサ(32)の上に配置される第2のスペーサ(34)と、少なくとも部分的に半導体合金領域(39)の上に重なるシリサイド領域(40)とを含むことができるが、ここでシリサイド領域(40)は第1及び第2のスペーサ(32、34)によってゲート積層体(29)から間隔を置かれる。

(もっと読む)

半導体装置及びそれを用いた光半導体リレー装置

【課題】 信号遮断時の出力端子間容量Coffを低減し、且つオン抵抗Ronを低減化

したSOI構造の半導体装置及びそれを用いた光半導体リレー装置を実現する。

【解決手段】 パワーMISFET20は、第1のシリコン基板1の表面上にBOX層(

酸化膜層)2が形成され、このBOX層2の表面上にN+ソース層7、P層6、低不純物

濃度オフセット層5、N+ドレイン層8が設けられている。このP層6上には、ゲート絶

縁膜9を介して第1のゲート電極10が設けられている。そして、第1のシリコン基板1

の裏面には、P層6に対向してBOX層2をゲート絶縁膜とする第2のゲート電極15が

設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 データ保持時間が十分に長く、高い歩留まりが得られるFBCの形成を可能とする半導体装置およびその製造方法を提供する。

【解決手段】 半導体基板110、半導体基板上に絶縁膜120を介して形成され単結晶構造を有する第1導電型半導体層130、半導体層130に形成された第2導電型ソース領域132、ドレイン領域134、ソース・ドレイン領域の間に形成されフローティング状態にある第1導電型ボディ領域136、ボディ領域の表面中央部上に絶縁膜140を介して形成されたゲート電極を有する複数のトランジスタと、各トランジスタの隣接するもの同士のボディ領域を素子分離する素子分離絶縁膜211、ゲート電極を共通接続するワード線WL、ドレイン領域に電気的に接続されたビット線BL、ソース領域に電気的に接続されたソース線SLを備え、ボディ領域136が絶縁膜140と接触する面積は、ボディ領域136が絶縁膜120と接触する面積より小さいことを特徴とする。

(もっと読む)

セルフバイアストランジスタ構造およびSRAMセル

自己バイアス半導体スイッチを供給することで、個々のアクティブコンポーネント数を減らしたSRAMセル(450)を実現することができる。特定の実施形態では、自己バイアス半導体デバイスを、ダブルチャネル電界効果トランジスタ(400)の形式で与えることができる。このトランジスタは、トランジスタ数が6つ未満の、また、好ましい実施形態では、わずか2つの個々のトランジスタ素子を備えたSRAMセル(450)の形成を可能にする。  (もっと読む)

(もっと読む)

分子発光デバイス

【課題】分子スケールの発光デバイスを提供する。

【解決手段】本発明の発光デバイスは、ゲート電極(101)と、電気刺激によって発光する分子を含み、その分子がゲート電極(101)の有効範囲内に配置されているチャネル(103)と、チャネルの第1の端部に結合され、チャネルに電子を注入するソース(104)と、チャネルの第2の端部に結合され、チャネルにホールを注入するドレイン(105)とを備える。  (もっと読む)

(もっと読む)

横型絶縁ゲートバイポーラPMOS装置

横型絶縁ゲートバイポーラPMOS装置(20b)は、半導体基板(22)と、埋め込み絶縁層(24)と、埋め込み絶縁層上のSOI層内に、p導電型のソース領域を有する横型PMOSトランジスタ装置とを含む。n導電型の横方向ドリフト領域(32)が本体領域(30)近傍に設けられ、p導電型のドレイン領域がドリフト領域により本体領域から横方向に分離されて設けられている。n導電型ドレイン領域(34b)が、p反転バッファ内に挿入されたシャローn型コンタクト表面領域として形成される。動作中にチャネル領域が形成され、本体領域(30)近傍の横方向ドリフト領域(32)の一部分の上部に延在する本体領域(30)の一部分の上部にゲート電極(36)が設けられている。ゲート電極(36)は絶縁領域(38)により本体領域(30)とドリフト領域(32)とから絶縁されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、寄生トランジスタ動作、ゲート電極とソース領域及びドレイン領域との間のリーク電流及び容量の増大を防止することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 半導体基板上に第1の絶縁膜を介して形成された凸型形状の半導体層と、第1の絶縁膜上に形成され、半導体層の底部から所定の高さまで埋没する程度の膜厚を有する絶縁膜と、半導体層の側面のうち、チャネル領域を流れる電流の方向と略平行に形成されている各側面に、ゲート絶縁膜を介して形成されたゲート電極と、半導体層内において、ゲート電極が形成されていない領域に形成されたソース領域及びドレイン領域とを備えることを特徴とする。

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

使い捨てスペーサを隆起ソース/ドレイン処理に取り入れた半導体デバイスの製造方法

半導体形成プロセスでは、ゲート電極(10)を基板(108)の上に形成する。第1シリコン窒化膜スペーサ(122)をゲート電極の側壁に隣接するように形成し、そして次に、使い捨てシリコン窒化膜スペーサ(130)をオフセットスペーサに隣接するように形成する。次に、使い捨てスペーサ(130)の境界によって画定される隆起ソース/ドレイン構造(132)をエピタキシャル成長により形成する。次に、使い捨てスペーサ(130)を除去して、ゲート電極(110)の近位に位置する基板を露出させ、そしてハロイオン注入(140)及びエクステンションイオン注入(142)のようなシャロージャンクションイオン注入を、ゲート電極の近位に位置する露出基板に行なう。取り替えスペーサ(136)を、使い捨てスペーサ(130)が形成されていた領域とほぼ同じ領域に形成し、そしてソース/ドレインイオン注入(140)を行なって、ソース/ドレイン不純物分布を隆起ソース/ドレイン(132)に形成する。ゲート電極(110)は被覆窒化シリコンキャップ層(144)を含むことができ、そして第1シリコン窒化膜スペーサ(122)はキャップ層(144)とコンタクトしてポリシリコンゲート電極(110)を窒化シリコンで取り囲むことができる。  (もっと読む)

(もっと読む)

複合スペーサ絶縁領域幅を備えた集積回路

異なるスペーサ絶縁領域幅を有するPチャネルトランジスタ(823)とNチャネルトランジスタ(821)とを備えた集積回路が開示されている。一実施形態において、Nチャネルトランジスタのスペーサ絶縁領域幅がPチャネルトランジスタのスペーサ絶縁領域幅よりも小さくなるようにPチャネル領域(115)をマスクしている間に、Nチャネルトランジスタの外側壁スペーサ(321)は除去される。また、Pチャネルソース/ドレインシリサイド領域(809)がPチャネルトランジスタのゲート(119)に対して配置されるよりも、Nチャネルトランジスタのドレイン/ソースシリサイド領域(805)はNチャネルトランジスタのゲート(117)に対してより近い位置に配置される。Pチャネルトランジスタのスペーサ絶縁幅をより大きくし、ソース/ドレインシリサイド領域とゲートとの間の距離をより大きくすることにより、Nチャネルトランジスタのチャネル領域の応力に対しPチャネルトランジスタのチャネル領域の相対圧縮応力を増大させた結果、Pチャネルトランジスタの性能が向上する。  (もっと読む)

(もっと読む)

絶縁された金属領域を備えたフィールドプレートを有する横方向薄膜SOIデバイス

横方向薄膜シリコン−オン−インシュレータ(SOI)デバイスにおいて、フィールドプレートは、パッケージ及び表面電荷効果からデバイスを保護するために横方向ドリフト領域に亘って実質的に延在するように設けられている。特に、フィールドプレートは、シリコンドリフト領域にドーピング量勾配により形成される横方向電界分布を呈するように、スペーシングにより相互に横方向において絶縁される複数の金属領域からなる層を備えている。  (もっと読む)

(もっと読む)

221 - 239 / 239

[ Back to top ]