Fターム[5F110GG36]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | チャネル領域の不純物 (5,796) | 不純物の分布 (414)

Fターム[5F110GG36]の下位に属するFターム

一導電型不純物のみ (175)

Fターム[5F110GG36]に分類される特許

121 - 140 / 239

横型MOS半導体装置

【課題】ボイドのでき易い深いトレンチもしくは経済性の悪い幅広トレンチを形成せずに、高耐圧に必要なオフセットドレイン領域の幅を確保しつつ占有面積を小さくすることができる横型MOS半導体装置を提供すること。

【解決手段】半導体基板の一方側の表面層に、それぞれ一導電型の、ソース領域13とドレイン領域12と、該ドレイン領域12より低不純物濃度で互いに接するオフセットドレイン領域5とを備え、前記ソース領域13表面と前記オフセットドレイン領域5表面に挟まれる他導電型のチャネル領域4表面にゲート絶縁膜を介して設けられるゲート電極6を有する横型MOS半導体装置において、前記オフセットドレイン領域5に、相互に並列で蛇行状の平面パターンであって表面から垂直に形成されるトレンチ列8を備え、該トレンチ列8に電流阻害材料7が充填されている横型MOS半導体装置とする。

(もっと読む)

横型MOSFET

【課題】従来の横型MOSFET20は、オン抵抗低減のために配置された比較的高い不純物濃度を有するN型不純物領域44の近傍で空乏層aが延びにくく、ゲート電極39のドレイン側端部まで達せず、ドレイン側端部に集中する高電界でホットキャリアが発生し、Vtが変動するという不具合があった。

【解決手段】本発明の横型MOSFET1は、P+型ベース領域35とN++型ドレイン領域36の間のN−型半導体層33の表面層に、N−型半導体層33より高い不純物濃度を有するN+型高濃度領域5と、その表面層に、一端をP+型ベース領域35に接しつつN++型ドレイン領域36に向かって延在するN+型高濃度領域5よりも低い不純物濃度を有する複数のN−型低濃度領域6とを有する。

(もっと読む)

半導体装置の作製方法及び成膜方法及び成膜装置

【課題】チャンバー外からチャンバー内へのリーク量が低減された成膜装置を提供することを課題とする。

【解決手段】チャンバー外からチャンバー内へのリークが生じたとしても、チャンバー外壁を囲む雰囲気に含まれる酸素及び窒素を極力低減し、希ガスまたは水素で充填することにより、大気における酸素濃度及び窒素濃度の100分の一以下、好ましくは1000分の一以下とし、チャンバー内をさらにクリーンに保つ。チャンバーの外側に気密性の高い空間を隣接して設けるため、チャンバーを袋体で覆い、高純度のアルゴンガスを袋体内に供給する。

(もっと読む)

薄膜トランジスタ

【課題】特性のばらつきを抑制できる薄膜トランジスタを提供する。

【解決手段】ガラス基板2上に設けられエッチングにより形成された端部5を有する多結晶又は非晶質Siからなる半導体層4と、半導体層4の両側に設けられたソース領域8およびドレイン領域9と、ソース領域8およびドレイン領域9間に設けられたチャネル幅が1μm以下のチャネル領域10と、チャネル領域10上にゲート絶縁膜6を介して設けられたゲート電極7と、チャネル領域10のチャネル幅方向のゲート電極7で被覆された端部5に電流が流れないように絶縁化された絶縁膜11とを具備し、ゲート電極7で被覆された端部5がしきい値電圧に寄与しない構造にした。

(もっと読む)

SOI(Silicononinsulator)構造の半導体装置およびその製造方法

【課題】効果的にゲッタリングが行えるSOI構造の半導体装置を提供する。

【解決手段】SOI基板100を用いたSOI構造の半導体装置において、活性層3となるシリコン基板に対してArイオンを注入することにより格子歪み層4を形成する。これにより、格子歪み層4をゲッタリングサイトとして機能させることが可能となる。また、Arイオンのドーズ量を調整し、格子歪み層4の引張り応力が11MPa以上かつ27MPa以下となるようにする。これにより、ゲッタリングサイトとして機能させつつ、リーク電流の発生を抑制することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、FIN状の半導体部やゲート電極を精度良く形成すること、又は素子間の特性バラツキを改善することで、特性の優れたFIN型トランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明は、一方にソース領域、他方にドレイン領域が形成されたFIN状の半導体部10と、ソース領域とドレイン領域との間で、FIN状の半導体部10をゲート絶縁膜を介して囲むように形成されたゲート電極17とを備える半導体装置である。そして、本発明に係る1つ解決手段は、ゲート電極17が、ウェットエッチング可能なメタル材料又はシリサイド材料を用いている。

(もっと読む)

表示装置および表示装置の製造方法

【課題】簡単な構成で、且つ若干の工程数の増加のみで、オフ電流の低減を図ったポリシリコン薄膜トランジスタを備える表示装置を提供する。

【解決手段】絶縁基板と、前記絶縁基板上に形成された薄膜トランジスタとを有する表示装置であって、前記薄膜トランジスタの半導体層は、多結晶シリコン層と、前記多結晶シリコン層の上層に形成された第1の非晶質シリコン層と、前記第1の非晶質シリコン層の上層に形成された第2の非晶質シリコン層とを有する。

(もっと読む)

半導体層とこの半導体層を用いた半導体装置および表示装置

【課題】水素終端化された高品質な多結晶Si膜を含む半導体薄膜を低温、高速成膜することで、良好な特性のTFTを安定して実現し、高品質、高画質の半導体装置および表示装置を提供する。

【解決手段】絶縁性基板上に形成したSi、Ge、F、Hを含有する半導体層4を、良好な結晶性が得られる反応熱CVD法で形成した多結晶SiGe膜または多結晶Si膜を第一層4aとその上層の第二層4bとの複数層の連続成膜で積層構造に構成し、該半導体層4中のH濃度を絶縁性基板1側に対して表面側にある第二層4bで高くした。

(もっと読む)

半導体集積回路装置の製造方法

【課題】本発明が解決しようとする技術的な課題は、安定したエッチングが可能な半導体集積回路装置の製造方法を提供するものである。

【解決手段】半導体集積回路装置の製造方法が提供される。前記半導体集積回路装置の製造方法は、ゲート電極120と、前記ゲート電極の両側壁に形成された犠牲窒化膜スペーサ150と、前記犠牲窒化膜スペーサにセルフアラインされたソース/ドレーン領域160とを含む電界効果トランジスタを形成し、酸化膜に対する窒化膜の選択比が1を超えるフッ酸により前記犠牲窒化膜スペーサを選択的に除去し、前記ゲート電極の両側壁上に、前記電界効果トランジスタのチャネル領域内に引張あるいは圧縮ストレスを誘導するストレス膜を形成することを含む。

(もっと読む)

半導体装置

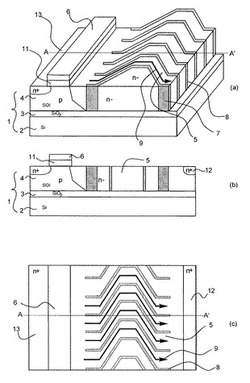

【課題】素子の耐圧を下げることなく、半導体層の層厚を小さくする。

【解決手段】BOX層4上に積層されたN−型のSOI層5に、環状のディープトレンチ6が形成されている。ディープトレンチ6は、SOI層5の表面からBOX層4に至る深さを有している。ディープトレンチ6に取り囲まれる素子形成領域9には、P型のボディ領域10と、このボディ領域10以外の残余の領域からなるN−型のドリフト領域11とが形成されている。ボディ領域10の表層部には、N+型のソース領域12が形成されている。ドリフト領域11の表層部には、N+型のドレイン領域14が形成されている。ドリフト領域11には、SOI層5のN型不純物濃度よりも高く、かつ、ドレイン領域のN型不純物濃度よりも低いN型不純物濃度を有するN型領域15が形成されている。N型領域15の最深部は、ドレイン領域14よりも深い位置に達している。

(もっと読む)

表示装置およびその製造方法

【課題】アモルファス半導体層を薄く形成することなくソース・ドレイン電流の増大を図った薄膜トランジスタを備える表示装置の提供。

【解決手段】表示装置の基板に形成される薄膜トランジスタであって、前記薄膜トランジスタは、前記基板上に形成されたゲート電極と、前記ゲート電極を被って形成されたゲート絶縁膜と、前記ゲート絶縁膜上に前記ゲート電極と交差する方向に少なくとも前記ゲート電極の中央部分で断続されて並設される一対の第1導電型の擬似単結晶層あるいは多結晶層と、前記一対の第1導電型の擬似単結晶層あるいは多結晶層と前記ゲート絶縁膜上に連続的に形成された第2導電型の擬似単結晶層あるいは多結晶層と、更に、その上に形成されたi型のアモルファス半導体層と、コンタクト層を介して、下層に位置づけて前記ゲート絶縁膜上にまで延在して形成されるドレイン電極とソース電極と、から構成される。

(もっと読む)

半導体装置

【目的】チップ面積の増大を伴うことなく、高いサージ耐量を確保でき、さらにバッテリー逆接続保護もできるサージ保護素子を有する半導体装置を提供する。

【解決手段】p型半導体層1の表面層にn型拡散領域32、33が形成され、その表面には絶縁膜3を介して横型MOSFETが形成される。この横型MOSFETの下に形成された絶縁膜3下にサージ保護素子である縦型ダイオード構成する拡散領域32、33の一部を形成することにより、チップ面積の増加を伴わずに動作面積を広げることができて高いサージ耐量を確保できる。

(もっと読む)

表示装置及び当該表示装置の作製方法

【課題】電気特性が高く信頼性のよい薄膜トランジスタを有する表示装置及びその作製方法を提案することを課題とする。

【解決手段】ゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ微結晶半導体を有する第1の半導体層と、第1の半導体層上に設けられ非晶質半導体を有する第2の半導体層と、第2の半導体層上に設けられたソース領域及びドレイン領域とを設け、第1の半導体層は第2の半導体層より結晶性が高く、第2の半導体層は、ソース領域とドレイン領域の間に、ソース領域及びドレイン領域と異なる導電型の不純物領域を設ける。

(もっと読む)

種類および膜厚の異なるゲート絶縁層を有するCMOSデバイス、ならびにその形成方法

high−k金属ゲート構造(310N,310B,310P)によって従来のゲート電極構造(310)を置換するためのプロセスシーケンスにおいて、例えば、選択性の高いエッチングステップ(322,325,327,331)を使用することによって、追加のマスク形成ステップの数を少なく保つことができ、これにより、従来のCMOS技術との高い互換性を保つことができる。更に、ここに開示の技術は、前工程(front-end)のプロセス技術および後工程(back-end)のプロセス技術との互換性を実現し、これにより、トランジスタレベルのほか、コンタクトレベルでも実績のある歪み発生機構を組み込むことが可能となる。  (もっと読む)

(もっと読む)

半導体装置

【課題】単結晶Si基板に水素イオン又はHeイオンを注入した後、単結晶Si基板を加熱することによってイオン注入層にて剥離することによって形成する単結晶Si薄膜トランジスタの特性劣化を防止する。

【解決手段】絶縁基板50上に薄膜デバイスを形成してなる半導体装置において、上記半導体装置内で、非単結晶Si薄膜からなる薄膜トランジスタと、単結晶Siからなる薄膜トランジスタとが混在しており、単結晶Siからなる薄膜トランジスタのゲート電極膜35が、シリコンより質量数の大きい金属またはその化合物を含む材料にて構成されている。

(もっと読む)

電界効果半導体装置

【課題】HEMTの漏れ電流を低減すること及び集積度を高めることが困難であった。

【解決手段】HEMT又はこれに類似の電界効果半導体装置は、第1の半導体層(3)と、第1の半導体層(3)に2次元電子ガス層を生じさせるために第1の半導体層(3)の一部上に配置された第2の半導体層(4)と、第1の半導体層(3)の主面(14)上に配置された第3の半導体層(5)と、第3の半導体層(5)の上に配置され且つ第3の半導体層(5)よりも低い抵抗率を有している第4の半導体層(6)と、第2の半導体層(4)の上に配置された第1の主電極(7)と、第4の半導体層(6)の上に配置された第2の主電極(8)と、第3の半導体層(5)の側面を被覆している絶縁膜(9)と、絶縁膜(9)を介して第3の半導体層(5)に対向配置されたゲート電極(10)とを備えている。

(もっと読む)

半導体装置およびその作製方法

【課題】SOI技術を用いて半導体装置を作製する上で、パンチスルー電流を抑えるだけでなく、貼り合わせに用いるシリコンウエハーの再利用を実現できる構造を有する半導体装置、およびその作製方法を提供する。

【解決手段】基板上にソース領域およびドレイン領域とは逆の導電型の不純物が注入された半導体膜109を形成し、その上にSOI技術を用いて単結晶半導体膜を接合して得られる積層の半導体膜204を用いてチャネル形成領域を形成することにより、半導体装置におけるパンチスルー電流を抑えることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

金属ゲート及び高K誘電体を有する回路構造体

【課題】 高k材料含有ゲート誘電体及び金属含有ゲートを有する回路構造体を提供する。

【解決手段】 高k誘電体のゲート絶縁体及び金属含有ゲートを有するPFETデバイス及びNFETデバイスを備えたFETデバイス構造体が、開示される。両方のNFETデバイス及びPFETデバイスにおけるゲート金属層が、単一の共通の金属層から製造された。単一の共通の金属であるために、デバイスの製造が簡単化され、必要とされるマスクの数が減少する。両方の型のデバイスのゲートのために単一の金属層を用いるさらなる結果として、PFET及びNFETの端子電極を、直接物理的に接触した状態で互いに付き合わせることができる。共通の金属材料を選択すること及び高k誘電体の酸素曝露によって、デバイスの閾値電圧が調整される。閾値は、低消費電力のデバイス動作を目的としている。

(もっと読む)

半導体装置製造用基板及びその作製方法

【課題】電気的特性の向上した半導体装置を製造することが可能な半導体装置製造用基板を提供する。

【解決手段】単結晶半導体基板の一表面上にシリコンと酸素とを組成に含む絶縁膜及びシリコンと窒素とを組成に含む絶縁膜を順に積層形成し、単結晶半導体基板に分離層を形成し、シリコンと酸素とを組成に含む絶縁膜にハロゲンイオンを照射して該シリコンと酸素とを組成に含む絶縁膜にハロゲンを含ませた後、シリコンと窒素とを組成に含む絶縁膜上に絶縁膜を形成する。半導体基板及び支持基板を、半導体基板側から順に積層されたシリコンと酸素とを組成に含む絶縁膜、シリコンと窒素とを組成に含む絶縁膜、及び絶縁膜を間に挟んで重ね合わせて接合し、分離層を境として半導体基板の一部を分離させる。

(もっと読む)

121 - 140 / 239

[ Back to top ]