Fターム[5F110GG36]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | チャネル領域の不純物 (5,796) | 不純物の分布 (414)

Fターム[5F110GG36]の下位に属するFターム

一導電型不純物のみ (175)

Fターム[5F110GG36]に分類される特許

21 - 40 / 239

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】素子面積の増大を抑制しつつ、駆動電流の高いON/OFF比と安定した特性を実現できる半導体装置及びその製造方法を提供する。

【解決手段】絶縁層と、絶縁層上に形成された半導体層と、半導体層に形成された部分空乏型のトランジスター10とを備え、トランジスター10は、半導体層上に絶縁膜を介して形成されたゲート電極14と、ゲート電極14両側下の半導体層に形成されたソース15又はドレイン16と、ボディーの下部に設けられた不純物層17,18とを有し、不純物層17,18は、ボディー領域の下部の両側端部に形成され、ソース15、ドレイン16とは接しない。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、ゲート電極を形成後、インライン装置にて、酸化アルミニウム膜と酸化シリコン膜と酸化物半導体膜を大気暴露することなく連続的に形成し、さらに同インライン装置にて加熱および酸素添加処理を行い、他の酸化アルミニウム膜でトランジスタを覆った後、熱処理を行うことで、水素原子を含む不純物が除去され、且つ、化学量論比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT)試験前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

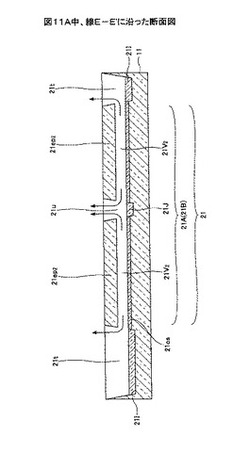

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体装置

【課題】縦型PN接合において確実にオン/オフの制御をすることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極とを備える。第1導電型の第1のチャネル領域が、ゲート絶縁膜の下にある半導体層の表面の一部に設けられている。第1導電型とは異なる導電型である第2導電型の拡散層が、第1のチャネル領域のさらに下の半導体層に設けられ、半導体層の表面に対してほぼ垂直方向に第1のチャネル領域の底部と接し、該第1のチャネル領域の底部とPN接合を形成する。第1導電型のドレインおよび第2導電型のソースが、第1のチャネル領域の両側にある半導体層内にそれぞれ設けられている。側壁絶縁膜は、第1のチャネル領域の拡散層側の側面を被覆する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層と該酸化物半導体層と接する絶縁膜との界面状態が良好なトランジスタ及びその作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層と該酸化物半導体層と接する絶縁膜(ゲート絶縁層)との界面状態を良好とするために、酸化物半導体層の界面近傍に窒素を添加する。具体的には酸化物半導体層に窒素の濃度勾配を作り、窒素を多く含む領域をゲート絶縁層との界面に設ける。この窒素の添加によって、酸化物半導体層の界面近傍に結晶性の高い領域を形成でき、安定した界面状態を得ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層と該酸化物半導体層と接する絶縁膜との界面状態が良好なトランジスタ及びその作製方法を提供する。

【解決手段】酸化物半導体層と該酸化物半導体層と接する絶縁膜(ゲート絶縁層)との界面状態を良好とするために、酸化物半導体層の界面近傍に窒素を添加する。具体的には酸化物半導体層に窒素の濃度勾配を作り、窒素を多く含む領域をゲート絶縁層との界面に設ける。この窒素の添加によって、酸化物半導体層の界面近傍に結晶性の高い領域を形成でき、安定した界面状態を得ることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】スパッタ法でトランジスタ、ダイオード等の半導体用途に好適な材料を提供する。具体的には結晶性の高い酸化物半導体膜を形成する作製プロセスを提供する。

【解決手段】意図的に窒素を酸化物半導体に対して添加することにより、六方晶であり、ウルツ鉱型結晶構造を有する酸化物半導体膜を形成する。酸化物半導体膜において、窒素を含む領域の結晶性は、窒素をあまり含まない領域、或いは窒素を意図的に添加していない領域に比べて高くなる。この結晶性の高いウルツ鉱型結晶構造を有する酸化物半導体膜をトランジスタのチャネル形成領域として用いる。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果による電気特性の変動が生じにくい、チャネル領域に酸化物半導体を含むトランジスタを用いた半導体装置を作製する。

【解決手段】窒素を含む一対の酸窒化物半導体領域、および該一対の酸窒化物半導体領域に挟まれる酸化物半導体領域を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体領域上に設けられるゲート電極とを有する半導体装置。ここで、一対の酸窒化物半導体領域はトランジスタのソース領域およびドレイン領域となり、酸化物半導体領域はトランジスタのチャネル領域となる。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

21 - 40 / 239

[ Back to top ]