Fターム[5F110HM14]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297) | ゲートに対する配置 (3,125) | オフセット (2,875)

Fターム[5F110HM14]の下位に属するFターム

LDD (2,472)

Fターム[5F110HM14]に分類される特許

121 - 140 / 403

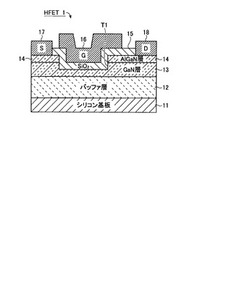

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置

【課題】ゲート構造を微細化してON抵抗を低減しても、アバランシェ耐量を高く維持できる半導体装置を提供する。

【解決手段】ドリフト領域2と、ベース領域3と、ベース領域3を挟んでドリフト領域2に対向して設けられたソース電極12と、ドリフト領域2とベース領域3とにゲート絶縁膜を介して接するトレンチ構造の複数のゲート電極6と、2つのゲート電極6の間において、ドリフト領域2とベース領域3との境界に沿って設けられ、ベース領域3に接する長さがゲート電極6よりも短いトレンチ構造のゲート電極7と、を備え、ソース電極12は2つのゲート電極6の間において、ソース電極12からゲート電極7に向かう方向に設けられたトレンチ9bの中に、ゲート電極7に近接した位置まで延在し、ゲート電極6のソース電極側の端とゲート電極7のソース電極側の端との間において、トレンチ9bの内壁面に露出したベース領域3に接していること。

(もっと読む)

電界効果トランジスタおよび半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOSトランジスタにおいて、オン抵抗とのトレードオフ関係で最適化されたオフ耐圧を低下させることなく、チャネル長を短くすることによって飽和電流を増加させる。

【解決手段】 チャネルとなる低濃度ボディ領域10と素子分離膜4の間かつゲート酸化膜8の直下に選択的に低濃度ボディ領域10と逆の極性で濃度が高いショートチャネル領域12を設け、ボディ領域10のゲート酸化膜8直下部分のみを高濃度ソース領域7側に後退させた形状を実現する。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

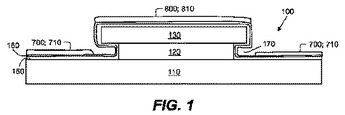

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTのESD耐性を高くしつつ、IGBTのバイポーラトランジスタを確実に動作させる。

【解決手段】シンカー層115は第1導電型ウェル102に接しており、かつ第1導電型コレクタ層108及び第2導電型ドリフト層104から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

フロント型プロジェクタ

【課題】高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつフロント型プロジェクタである。

【解決手段】チャネル形成領域、ソース領域、及びドレイン領域を有する半導体層と、島状のゲート電極とを備えた薄膜トランジスタを有し、ゲート電極が接続する第1配線と、ソース領域又はドレイン領域が接続する第2配線とは直交し、第2配線や容量配線と平行かつ重なるように配置されている。

(もっと読む)

表示装置及び電子機器

【課題】画素電極電位に起因したオフリーク電流が上昇しにくい低消費電力の表示装置を提供すること。

【解決手段】表示装置は、対向配置された第1の基板及び第2の基板と、第1の基板と第2の基板との間に配置された表示素子と、第1の基板の表示素子側に形成された薄膜トランジスター24と、薄膜トランジスター24の表示素子側に、平面視で薄膜トランジスター24と重なるように形成された画素電極21と、薄膜トランジスター24と画素電極21との間の層に形成されたシールド電極26と、を備える。シールド電極26は、平面視で少なくとも薄膜トランジスター24の低濃度不純物領域に重なる位置に配置される。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

表示装置

【課題】赤色、青色、緑色の発光輝度のバランスが良い、色鮮やかな画像を表

示することができるEL表示装置を提供する。

【解決手段】 複数のEL素子をそれぞれ含む複数の画素を有するEL表示装置

であって、前記EL表示装置は前記複数のEL素子の発光する時間を制御するこ

とで階調表示を行い、前記複数のEL素子に印加される電圧は、前記複数のEL

素子をそれぞれ含む複数の画素が表示する色によって異なることを特徴とするE

L表示装置。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】チャネル抵抗の増大を回避させた薄膜トランジスタの提供。

【解決手段】ボトムゲート型の薄膜トランジスタであって、ゲート絶縁膜上にゲート電極の形成領域に開口を有する層間絶縁膜が形勢され、半導体膜は前記開口を被って層間絶縁膜上に形成され、

前記層間絶縁膜は前記ゲート絶縁膜よりも窒化物を多く含み、前記半導体膜は、前記ゲート絶縁膜および前記層間絶縁膜面に形成された少なくともGeを含む半導体結晶核上に形成された微結晶半導体膜あるいは多結晶半導体膜によって構成されている。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置の作製方法

【課題】絶縁基板上に第1の単結晶半導体膜と、該第1の単結晶半導体膜上に第2の単結晶半導体膜を有する半導体装置の作製する方法を提供する。

【解決手段】第1の単結晶半導体基板に第1のイオンをドープして第1の脆化層を形成する工程と、第2の単結晶半導体基板に第2のイオンをドープして第2の脆化層を形成する工程と、第1の単結晶半導体基板と第2の単結晶半導体基板とを貼り合わせる工程と、第1の加熱処理により、第2の単結晶半導体基板上に第1の単結晶半導体膜を形成する工程と、第1の単結晶半導体膜上に絶縁基板を貼り合わせる工程と、第2の加熱処理により、絶縁基板上に、第1の単結晶半導体膜及び第2の単結晶半導体膜を形成する工程と、を有し、第1のイオンのドーズ量は第2のイオンのドーズ量よりも多く、第1の加熱処理の温度は第2の加熱処理を温度よりも低い。

(もっと読む)

半導体デバイスおよび表示装置

【課題】オン抵抗を犠牲にしないで寄生容量とリーク電流のトレードオフを解消または緩和する。

【解決手段】TFT部10Bは、2つのソース・ドレイン電極18,19が、半導体膜15の平面視でチャネル形成領域を挟んで位置する一方と他方の半導体領域に接する。ソース・ドレイン電極18,19は、半導体膜15と接する領域(斜線部)の当該ソース・ドレイン電極の輪郭部分30において、その両端のエッジポイント31の各々が、平面視でゲート電極13の外側に位置している。

(もっと読む)

有機EL表示装置

【課題】オフ特性、スウィング特性、飽和特性に優れた薄膜トランジスタを備える有機EL表示装置を提供する。

【解決手段】基板1上に薄膜トランジスタを備える有機EL表示装置であって、前記薄膜トランジスタは、ゲート電極2、前記ゲート電極2を覆うゲート絶縁膜3、前記ゲート絶縁膜3上に設けられた第1の半導体膜4、前記第1の半導体膜4上に設けられた第2の半導体膜5、前記第2の半導体膜5上に設けられたバックチャンネル保護絶縁膜7、オーミックコンタクト膜8、ソース・ドレイン電極9とを有し、前記第1の半導体膜4は前記第2の半導体膜5より高い結晶性を有し、前記バックチャンネル保護絶縁膜7は有機絶縁膜もしくは有機・無機ハイブリッド絶縁膜により形成される。

(もっと読む)

高耐圧半導体装置および駆動回路

【課題】スイッチング応答速度が速い高耐圧トランジスタ、および電力損失および誤動作を抑制した駆動回路を提供すること。

【解決手段】高耐圧半導体装置は、p-型シリコン基板100上に設けられ、かつp-ウエル領域102に囲まれたn-型領域101と、ドレイン電極120と接続されるドレインn+領域103と、ドレインn+領域103と離れて設けられ、かつドレインn+領域103を囲むpベース領域105と、pベース領域105内に形成されたソースn+領域114と、を備える。また、n-型領域101を貫通し、かつシリコン基板100に達するp-領域131が設けられている。n-型領域101は、p-領域131により、n-型領域101aとn-型領域101bに分離されている。n-型領域101aは、ドレインn+領域103を備えている。n-型領域101bは、フローティング電位を有する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

121 - 140 / 403

[ Back to top ]