Fターム[5F140AC14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 量子効果素子 (56) | トンネルトランジスタ (46) | 絶縁膜によるもの (17)

Fターム[5F140AC14]に分類される特許

1 - 17 / 17

トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のチャージアップによるMOSFETの閾値電圧Vtシフトの防止を図ることである。

【解決手段】キャパシタ下部電極3をゲート電極6aと結線し、またキャパシタ上部電極6bをP型接地層12と結線する事により、ゲート電極6aとゲート絶縁膜4から成るゲートに並列にキャパシタを形成する。この場合、キャパシタ絶縁膜5をゲート絶縁膜4に比べ薄く形成する事によりゲート電極6a上にチャージアップした電荷を、キャパシタを経由してP型接地層12に放電させる。

(もっと読む)

半導体装置、キャパシタ、および電界効果トランジスタ

【課題】半導体と金属との界面において、接合する金属の実効仕事関数を最適化した半導体装置を提供することを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aとを備え、酸化膜がHf酸化膜或いはZr酸化膜であって、酸化膜に、V、Cr、Mn、Nb、Mo、Tc、W、Reから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

スピンFET及び磁気抵抗効果素子

【課題】素子抵抗の低抵抗化とMR比の向上とを同時に実現する。

【解決手段】本発明の例に係るスピンFETは、ソース・ドレイン部に、少なくとも半導体基板11/トンネルバリア12/低仕事関数材料13/強磁性体14からなる積層構造を有し、低仕事関数材料13は、未酸化のMg,K,Ca,Scのうちの1つ、又は、その1つを原子数比で50%以上含む合金から構成される。

(もっと読む)

スピンFET、磁気抵抗効果素子及びスピンメモリ

【課題】スピンFET/スピンメモリの低消費電力と高信頼性を実現する。

【解決手段】本発明の例に係るスピンFETは、第1ソース/ドレイン領域11a-1上に配置され、磁化方向が膜面に対して垂直方向となる上方向又は下方向に固定される第1強磁性膜12と、第2ソース/ドレイン領域11a-2上に配置され、磁化方向が上方向又は下方向に変化する第2強磁性膜13と、第2強磁性膜13上に配置される反強磁性強誘電膜15と、第1ソース/ドレイン領域11a-1と第1強磁性膜12との間及び第2ソース/ドレイン領域11a-2と第2強磁性膜13との間の少なくとも1つに配置されるトンネルバリア膜20,21とを備える。反強磁性強誘電膜15の抵抗は、第1及び第2ソース/ドレイン領域11a-1, 11a-2がチャネル領域11cを介して導通したときのオン抵抗よりも大きい。

(もっと読む)

ヘテロ構造を有する細長い単結晶ナノ構造に基づくトンネル効果トランジスタ

【課題】トンネル電界効果トランジスタ(TFET)は、金属酸化物電界効果トランジスタ(MOSFET)の後継者と考えられるが、シリコンベースのTFETは一般に低いオン電圧、トンネルバリアの大きな抵抗による欠点が問題となる。より高いオン電流を得るために、異なった半導体材料(例えばゲルマニウム(Ge))からなるヘテロ構造を備えた細長い単結晶ナノ構造ベースのTFETが用いられる。

【解決手段】TFETのソース(又は代わりにドレイン)領域として機能する、異なった半導体材料からなる細長い単結晶ナノ構造を導入する。ヘテロ部分の導入は、シリコンとゲルマニウムの間の格子不整合が高い欠陥界面とならないように行われる。従来のMOSFETに匹敵する、静的電力の低減と同様に動的電力の低減が行われる。細長い単結晶ナノ構造のSi/GeTFETによる超高密度オンチップトランジスタを用いた、多層の論理が期待される。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型トランジスタのカットオフ時のリーク電流を低減する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板と前記半導体基板の内部に形成された第1の不純物拡散領域と前記第1の不純物拡散領域の上方に形成された柱状半導体層と前記柱状半導体層の側方に形成されたゲート絶縁膜と前記ゲート絶縁膜の側方に形成されたゲート電極と前記不純物拡散領域の上方で前記ゲート電極に接して形成された絶縁体からなる層間膜と前記柱状半導体層の上方で前記ゲート電極に接して形成された絶縁体からなるスペーサと前記柱状半導体層の上方に形成された第2の不純物拡散領域とを具備し前記柱状半導体層の略中央に絶縁膜を有する。

(もっと読む)

単一電荷トンネル素子

【課題】不揮発性メモリ素子としても使用可能な、単一電荷トンネル素子、特に単一電子トランジスタ、を提供する。

【解決手段】強磁性物質から成る単一電荷トンネル素子を従来のようにゲート電圧の印加により電気モードにおいて制御するのみならず、回転する配向磁場の印加により磁気モードにおいても制御する。即ち、該配向磁場の印加により該強磁性物質の化学ポテンシャルが変化し、クーロンブロッケード異方性磁気抵抗効果が生じる。その結果として得られる該素子の抵抗値とその変化を、論理的な1,0の書込み信号と、その切り替えに用いる。該磁気モードのヒステリシス性により、不揮発性メモリ効果が発現される。

(もっと読む)

電界効果トランジスタ、集積回路、及びメモリ

【課題】 微細化が進んだ場合でもゲート・リーク電流の低減を図ることのできる電界効果トランジスタを実現すること。

【解決手段】 半導体基板1と、磁化方向が第1方向に固定された第1強磁性体電極3と、磁化方向が前記第1方向と実質的に同じ方向に固定された第2強磁性体電極4と、第1強磁性体電極3と第2強磁性体電極4との間のチャネル2と、チャネル2上にゲート絶縁層5を介して設けられ磁化方向が前記第1方向と実質的に反対の方向に固定された強磁性体層6を備えたゲート電極とを具備することを特徴とする電界効果トランジスタ。ゲート電極の強磁性体層6の磁化方向が、第1強磁性体電極3及び第2強磁性体電極4のそれぞれの磁化方向と実質的に反対の方向に固定されているので、トンネル磁気抵抗効果によりゲート・リーク電流を低減化することができる。

(もっと読む)

電子装置、電子装置の製造方法、電子回路及び電子機器

【課題】 特性を安定にでき、製造コストが安価で、高集積化を行い易く、また、効果的に消費電力の低減を行うことができる電子装置とその製造方法を提供すること。

【解決手段】 電子装置は、絶縁体101の中に、金属で形成された第1領域102及び第2領域103と、この第1領域102と第2領域103で挟まれた第3領域104を備える。この第3領域は、第1及び第2領域102,103を形成する金属元素と同じ金属元素で形成されて、直径が20nm以下の微粒子を有する。第1領域102及び第2領域103は、第3領域104よりも、金属濃度が高くて電気抵抗が小さい。第1領域102と第2領域103とに電圧が印加されて、第3領域104を単一の電荷がトンネルする。第1領域102と、第2領域103と、第3領域104とは、互いに同じ金属元素を含むので、互いの境界に形成される障壁を安定にできる。

(もっと読む)

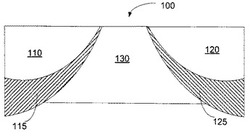

半導体装置、半導体装置の製造方法、セルアレイ及びセルアレイの製造方法

【課題】 スイッチ機能が十分に得られ、常温においても十分にスイッチ動作ができ、微細化を図ることができるスイッチング素子を提供すること。

【解決手段】 基板101上に形成されたゲート絶縁膜102上に、第2絶縁膜105で隔てられた第1電極103と第2電極104を形成する。第1電極103は、ゲート絶縁膜102の表面に接する側の部分が鋭角断面を有するように、側面が傾斜している。ゲート絶縁膜102中に、20nm以下の直径を有すると共に、第1電極3と第2絶縁膜105との境界が含まれる平面と略同一の平面上に配列された金属微粒子106を形成する。第1絶縁膜2中の金属微粒子6の数を、第1絶縁膜2の膜厚と、第1絶縁膜2への金属元素の注入及びアニール条件とで制御できるので、微細加工の最小加工寸法の制約を受けない。また、ゲート長を、ゲート絶縁膜102の厚みによって設定できるので、微細加工の最小加工寸法の制約を受けない。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】 ソース・ドレインの界面形状とショットキー障壁高さ、電極比抵抗を同時に制御可能なショットキートランジスタを提供する。

【解決手段】 チャネル領域を構成する半導体領域112と、半導体領域112上にゲート絶縁膜113を介して形成されたゲート電極114と、ゲート電極114に対応して半導体領域112の両側に形成されたソース・ドレイン電極とを備えたMIS型電界効果トランジスタにおいて、ソース・ドレイン電極は、半導体領域112を挟んで形成され、且つキャリアがトンネル可能な厚さに形成されたトンネル絶縁膜116と、トンネル絶縁膜に接して形成された第1の金属層117と、第1の金属層117に接して形成され、第1の金属層117よりも小さい比抵抗を持つ第2の金属層118と、をチャネル長方向に積層してなる。

(もっと読む)

半導体装置及びその製造方法

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 従来よりも高い温度でも動作できるクーロンブロケードを用いた量子効果素子

を提供すること。

【解決手段】 後方障壁閉じ込めポテンシャルを形成するための下部SiO2層43と上

部SiO2層45と、p−型層47と、これらSiO2層43、45、p−型層47各端

と交わる傾斜面51と、傾斜面51上にSiO2活性層61を介して設けられたゲート電

極31を有し、このゲート電極31のうち、SiO2層43、45の各端を覆うる部分は

狭くなっている。

(もっと読む)

MOS電界効果トランジスタ型量子ドット発光素子および受光素子、これらを利用した光電子集積チップおよびデータ処理装置

【課題】 MOS電界効果トランジスタ型量子ドット発光素子および受光素子の提供、MOS電界効果トランジスタ型量子ドット発光素子の製造方法の提供、かかる受発光素子を利用した光電子集積チップ、データ処理装置を提供することを目的とする。

【解決手段】 MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたトンネルSiO2層と、該トンネルSiO2層上に形成されたSi殻内にGe核を内包した量子ドットと、該量子ドット上及び前記トンネルSiO2層上に形成されたコントロールSiO2層と、該コントロールSiO2層上に形成されたゲート電極層と、を有する。MOS電界効果トランジスタ型量子ドット発光素子は、半導体基板と、該半導体基板上に形成されたゲートSiO2層と、該ゲートSiO2層上に形成されたドープSi層、Ge層及びドープSi層を順次積層してなる積層ゲート電極層と、を有する。

(もっと読む)

スピントランジスタ、プログラマブル論理回路および磁気メモリ

【課題】増幅機能を有するスピントランジスタを提供すること。

【解決手段】スピントランジスタ100は、半導体基板10と、半導体基板10上において第1方向に磁化された強磁性体で形成される第1導電層12と、半導体基板10上において第1方向とその第1方向に対して反平行の第2方向とのいずれか一方に磁化される強磁性体で形成された第2導電層14と、第1導電層12と第2導電層14の間に位置し、第1導電層12と第2導電層14との間で電子スピンを導くチャネル部と、チャネル部の上方に位置するゲート電極40と、第1導電層12および第2導電層14の少なくとも一方とチャネル部との間に位置するトンネルバリア膜11a,11bと、を備える。

(もっと読む)

1 - 17 / 17

[ Back to top ]