Fターム[5F140BA00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253)

Fターム[5F140BA00]の下位に属するFターム

Fターム[5F140BA00]に分類される特許

21 - 40 / 47

電界効果トランジスタ

【課題】ゲートの漏れ電流を低減させる。

【解決手段】電子トラップ及びゲート電流の漏れを減少させる窒化物系FETデバイス10である。該デバイスは、デバイスの加工に起因するトラップを減少させるため比較的厚い不動態化層20と、ゲート電流の漏れを減少させるためゲート端子38の下方の薄い不動態化層16、18とを含む。デバイスは、基板12上に堆積させた半導体デバイス層14を含む。複数の不動態化層が半導体デバイス層14上に堆積され、少なくとも2つの層はエッチストップを提供し得るよう異なる誘電性材料にて出来ている。層の間の境界面をエッチストップとして使用することにより1つ又はより多くの不動態化層18、20を除去し、ゲート端子38と半導体デバイス層14間の距離を正確に制御することができるようにし、この距離はデバイスの性能を向上させ且つゲート電流の漏れを減少させるよう極めて短くすることができる。

(もっと読む)

半導体装置

【課題】MIS型半導体装置やMS型半導体装置において、簡便な手法により半導体層の界面準位を所望のエネルギー準位に設定することが可能な半導体装置を提供する。

【解決手段】導電体と、ソース領域とドレイン領域とを有する半導体と、前記ソース領域と前記ドレイン領域との間において、前記導電体と前記半導体とにそれぞれ接して前記導電体と前記半導体との間に設けられた単分子層と、を備え、前記半導体と前記単分子層との界面において、前記単分子層を構成する分子の電子準位が前記半導体のバンドギャップ内に状態密度の極大を形成してなることを特徴とする半導体装置を提供する。

(もっと読む)

サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【課題】 サブリソグラフィック幅を有する応力誘起ライナによる異方性応力の生成。

【解決手段】 直線端部を有する突出構造体を基板(8)上に形成する。突出構造体は電界効果トランジスタのゲートラインとすることができる。応力誘起ライナを基板(8)上に堆積させる。少なくとも2つの不混和性のポリマブロック成分を含む非感光性自己組織化ブロックコポリマ層を応力誘起ライナ(50)の上に堆積させ、アニールして不混和性成分を相分離させる。ポリマレジストを現像して少なくとも2つのポリマブロック成分のうちの少なくとも1つを除去し、突出構造体の直線端部(41)により入れ子になったラインのパターンを形成する。直線型のナノスケール・ストライプが、自己配列及び自己組織化のポリマレジスト内に形成される。応力誘起層は、サブリソグラフィック幅を有する直線型応力誘起ストライプにパターン化される。直線型応力誘起ストライプ(50)は主にそれらの縦方向に沿った一軸性応力をもたらし、下層の半導体デバイスに異方性応力を加える。

(もっと読む)

高性能ヘテロ構造FETデバイス及び方法

【課題】

【解決手段】積層ヘテロ構造電界効果トランジスタ(HFET)は、基板と、基板上に成長する第1の酸化物半導体層と、第1の半導体層上に成長し、第1の半導体層とエネルギー・バンドギャップが異なる第2の酸化物半導体層と、を備え、また、前記第2の層は、ゲート領域と、ドレイン領域と、ソース領域と、を有し、ゲート領域、ドレイン領域、及びソース領域に対しては、HFETを形成するのに十分な電気的接触がもたらされる。基板は、単結晶材料を含む材料とすることができ、また、第1の半導体層がその上に成長するバッファ層材料を含有することができる。第1及び第2の半導体層の導電型ならびに各酸化物半導体層の組成は、HFETの所望の動作性能特性が改善されるように選択することができる。この積層構造は、半導体HFETデバイスの機能ならびに高周波及び高電力性能の改善に応用することができる。

(もっと読む)

半導体デバイス

【課題】半導体バルク基板や半導体・オン・絶縁体基板のような基板上に半導体デバイスを形成する良好な方法、及びその方法で形成した半導体デバイスを提供する。

【解決手段】基板をパターニングし、基板の第1主表面の平面に実質的に垂直な方向に、基板から延びた、少なくとも1つの構造を形成した後に、少なくとも1つの構造により覆われていない基板の位置に、部分的に変更された領域6を形成し、それらの領域6のエッチング抵抗を部分的に増加させる工程とを含む。部分的に変更された領域の形成工程は、半導体デバイス10の作製中の更なる処理工程中に、少なくとも1つの構造のアンダーエッチングを防止できる。部分的に変更された領域の形成工程は、少なくとも1つの構造により覆われていない基板の領域に、注入元素を注入する工程により行われても良い。

(もっと読む)

ナノシリコン半導体基板製造方法、半導体回路装置

【課題】 MOSトランジスタの閾値電圧を基板濃度に依ることなく制御でき、チャネル長が極微細化した場合のショートチャネル効果の抑制が容易となる基板構造を提供する。

【解決手段】 シリコン基板200の表面のシリコン酸化膜200Aの上に、同一粒径のナノシリコン粒よりなる第1のナノシリコン膜201を形成する。さらに、この上に窒化シリコン膜201Aを形成した後、平均粒径が第1のナノシリコン膜201とは異なる第2のナノシリコン膜202を形成する。このようにして作製したナノシリコン半導体基板上に半導体回路素子を形成する。

(もっと読む)

絶縁膜及びその製造方法、並びに絶縁膜を備えた電子デバイス

【課題】 他の部分にダメージを与えることなく優れた絶縁性が得られる絶縁膜及びその製造方法、並びに絶縁膜を備えた電子デバイスを提供する。

【解決手段】 基板1上に、蒸着法により、Al、Hf、Zr及びSiからなる群から選択された少なくとも1種の元素を含む酸化物又は窒化物からなる蒸着絶縁膜2を形成する。そして、この蒸着絶縁膜2に対して、基板1の温度を300乃至500℃にして、水素プラズマ処理及び酸素プラズマ処理からなる群から選択された少なくとも1種の処理を施す。

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体基板およびその製造方法

【課題】半導体基板表面の{110}面に対する傾斜角(オフ角)を最適化することにより、表面粗さ(ラフネス)の低減される半導体基板およびその製造方法を提供する。

【解決手段】表面が{110}面に対して、0度以上0.12度以下、または、5度以上11度以下の傾斜角(オフ角)、より望ましくは6度以上9度以下の傾斜角を有することを特徴とする半導体基板、および、半導体単結晶インゴットを{110}面に対して5度以上11度以下の傾斜角(オフ角)、より望ましくは6度以上9度以下の傾斜角でスライスする工程を有することを特徴とする半導体基板の製造方法。

(もっと読む)

電子素子構造

【課題】耐熱性、耐放射線性及び高周波応答性が優れ、高温用デバイス、大電力用デバイス及び高周波電子デバイスに適した電子素子において、オーミック電流を抑制し、高濃度にドープされた半導体からチャネルへのキャリア注入の障壁エネルギを低減して空間電荷制限電流の立ち上がり電界を小さくした高効率な電子素子構造を提供する。

【解決手段】絶縁体ダイヤモンド結晶基板1上にキャリア濃度を1015cm-3以下の高抵抗率な半導体ダイヤモンド薄膜5を設け、これを挟むようにキャリア濃度が1020cm-3以上の低抵抗率な半導体ダイヤモンド薄膜2a及び2bを設け、半導体ダイヤモンド薄膜5、2a及び2bの伝導型を同じにする。更に、半導体ダイヤモンド薄膜2a、2b及び5上に夫々ソース電極11a、ドレイン電極11b及びゲート電極9aを設ける。

(もっと読む)

逆行性炭素プロファイルを有する低欠陥Si:C層

【課題】 逆行性炭素プロファイルを有する低欠陥Si:C層を有する半導体構造体及びその形成方法を提供する。

【解決手段】 炭素置換型単結晶シリコン層の形成は、特に高炭素濃度において多くの欠陥を生じやすい。本発明は、シリコン内の高炭素濃度に対しても低欠陥の炭素置換型単結晶シリコン層を与えるための構造体及び方法を提供する。本発明によれば、炭素注入の積極的逆行性プロファイルが、固相エピタキシ後に得られる炭素置換型単結晶シリコン層内の欠陥密度を減少させる。これは、圧縮応力及び低欠陥密度を有する半導体構造体の形成を可能にする。半導体トランジスタに適用されるとき、本発明は、チャネル内に存在する引張応力により向上した電子移動度を有するN型電界効果トランジスタを可能にする。

(もっと読む)

簡単化されたデュアル応力ライナ構成を用いる向上した性能をもつ半導体構造体

【課題】 簡単化されたデュアル応力ライナ構成を用いる向上した性能をもつ半導体構造体を提供すること。

【解決手段】 ゲート誘電体の下にあるチャネル領域内の応力を強化するために、新しいデュアル応力ライナ構成が用いられる、完全にシリサイド化されたゲート電極を有するnFETを含む半導体構造体が提供される。新しいデュアル応力ライナ構成は、nFETの完全にシリサイド化されたゲート電極の上面と実質的に同一平面にある上面を有する第1の応力ライナを含む。本発明によると、第1の応力ライナは、完全にシリサイド化されたゲート電極を含むnFETの上には存在しない。代わりに、本発明の第1の応力ライナは、完全にシリサイド化されたゲート電極を有するnFETを部分的に包み込む、すなわちその両側を囲む。第1の応力ライナのものと反対の極性を有する(すなわち、反対の応力型の)第2の応力ライナが、第1の応力ライナの上面上及び完全にシリサイド化されたFETを含むnFETの上に配置される。本発明によると、第1の応力ライナは引張応力ライナであり、第2の応力ライナは圧縮応力ライナである。

(もっと読む)

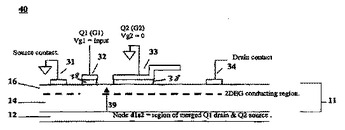

併合ゲートカスコードトランジスタ

この発明の実施例に従う併合ゲートトランジスタは、半導体要素と、半導体要素の上面に電気的に接続された供給電極と、半導体要素の上面に電気的に接続され、かつ、供給電極から横方向に間隔をあけたドレイン電極と、供給電極およびドレイン電極の間に位置決めされ、かつ、半導体要素に容量結合されて、トランジスタの第1の部分を形成する第1のゲートと、第1のゲートに隣接して供給電極およびドレイン電極の間に位置決めされて、トランジスタの第2の部分を形成する第2のゲートとを含み、第2のゲートも半導体要素に容量結合される。第1のゲートは、第1の部分の導通が入力電圧信号の値に基づくように入力電圧信号に接続され、第2のゲートは、所定の定電圧とソース電極における電圧との間の電圧差が所定のレベルに達するまでトランジスタの第2の部分が導通するように所定の定電圧に接続される。  (もっと読む)

(もっと読む)

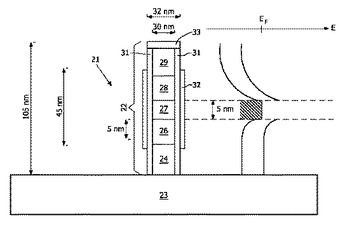

バリアを有するトンネルトランジスタ

本発明は、ソース(24)およびドレイン(29)、並びにこれらのソースとドレインの間に配置されたバリア領域(27)を備えたトランジスタ(21)を提案する。バリア領域は、半導体材料の真性または低濃度ドーピング領域(26,28)によってソースおよびドレインから分離されている。バリア領域と真性または低濃度ドーピング領域との界面にポテンシャルバリアが形成される。ゲート電極(32)はポテンシャルバリアの付近に設けられ、ゲート電極に適切な電圧を印加することによって、ポテンシャルバリアの実効的な高さおよび/または幅を調整することができる。  (もっと読む)

(もっと読む)

同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体

【課題】 同じ基板上に同じ導電型の低性能及び高性能デバイスを有する半導体デバイス構造体を提供すること。

【解決方法】 半導体デバイス構造体を製造する方法は、基板(10)を準備するステップと、第1スペーサ(SP)を備える第1ゲート(G1)、第2スペーサ(SP)を備える第2ゲート(G2)、第1ゲート及び第2ゲートに隣接する、同じ導電型のそれぞれのソース(S)/ドレイン(D)領域、第1ゲートと第2ゲートとの中間に配置された分離領域(STI)、及び第1ゲート、第2ゲート、並びにそれぞれのソース及びドレイン領域の上にあるシリサイドを基板上に形成するステップと、中間構造体を製造するために第1スペーサ上に付加的なスペーサ(RSPS)を形成し、次いで、中間構造体全体の上に応力層を配置するステップと、を含む。

(もっと読む)

半導体装置

【課題】 半導体チップを折り曲げることにより、Pチャネル電界効果型トランジスタとNチャネル電界効果型トランジスタの移動度を同時に向上させる。

【解決手段】 <110>方向に沿って凹状に折り曲げられた(100)基板11には、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたPチャネル電界効果型トランジスタが形成されるとともに、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたNチャネル電界効果型トランジスタが形成され、Nチャネル電界効果型トランジスタ上には、(100)基板11の折り曲げによる圧縮応力よりも大きな引っ張り応力F1´を印加するゲートキャップ膜15が形成されている。

(もっと読む)

半導体装置、電気光学装置及び電子機器

【課題】基板を湾曲(変形)しても、トランジスタの特性変化が少ない半導体装置、電気光学装置、電子機器を提供する。

【解決手段】 半導体層と、半導体層を使用して形成される第1及び第2のトランジスタ(100,200)と、を含み、半導体層の湾曲に対して第1及び第2のトランジスタの各コンダクタンスが相補的に変化する。基板を湾曲させても、当該湾曲による半導体装置の特性変化を抑制することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 セルフヒート効果を低減することができ、基板浮遊効果も解消できるようにした半導体装置及びその製造方法を提供する。

【解決手段】 Si基板1上のSi層10にゲート酸化膜21を介して形成されたゲート電極23と、ゲート電極23を挟んでSi層10に形成されたソース層27a及びドレイン層27bと、を含んで構成されるSDONトランジスタ100を有し、ソース層27aとSi基板1との間及び、ドレイン層27bとSi基板1との間にはそれぞれ空洞部15が存在し、且つゲート電極23下のSi層10とSi基板1との間には空洞部が存在していないことを特徴とするものである。ゲート電極23下のSi層10がSi基板1とつながっているので、SONトランジスタと比べて、セルフヒート効果を低減することが可能である。また、ボディ電位はSi基板1に固定されるので、基板浮遊効果を解消することができる。

(もっと読む)

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

少なくとも一対の空間的に隔てられた応力領域間に歪み超格子を含む半導体デバイス、及びその製造方法

半導体デバイスは、少なくとも一対の空間的に隔てられた応力領域(227、228)と、この少なくとも一対の空間的に隔てられた応力領域間の、積層された複数の層群を有する歪み超格子層(225)とを含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

21 - 40 / 47

[ Back to top ]