Fターム[5F140BA16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | エピタキシャル基板 (980)

Fターム[5F140BA16]の下位に属するFターム

Si基板上に化合物半導体成長 (318)

Fターム[5F140BA16]に分類される特許

21 - 40 / 662

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

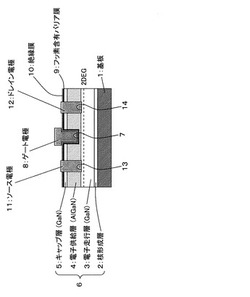

窒化物半導体装置

【課題】スイッチングノイズ発生を抑制できるノーマリオフ形の窒化物半導体装置の提供。

【解決手段】本発明の実施形態の窒化物半導体装置は、AlxGa1−xN(0≦x<1)からなる第1の半導体層4と、AlyGa1−yN(0<y≦1、x<y)からなる第2の半導体層5と、導電性基板2と、第1の電極6と、第2の電極8と、制御電極7と、を備える。第2の半導体層は第1の半導体層に直接接合する。第1の半導体層は、導電性基板に電気的に接続される。第1の電極及び第2の電極は、第2の半導体層の表面に電気的に接続される。制御電極は、第1の電極と第2の電極との間の第2の半導体層の前記表面上に設けられる。第1の電極は、Si−MOSFET102のドレイン電極8aに電気的に接続される。制御電極は、前記MOSFETのソース電極6aに電気的に接続される。導電性基板は、前記MOSFETのゲート電極7aに電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

炭化ケイ素半導体装置の製造方法

【課題】炭化ケイ素(000−1)面にウェット雰囲気で酸化されたゲート絶縁膜の上に、ポリシリコンを不活性ガスを使用した減圧CVD法で成膜しても、界面準位密度の増加を抑制し、MOS界面特性の劣化を防止して、炭化ケイ素半導体装置の品質を高める。

【解決手段】炭化ケイ素半導体の(000−1)面から0°ないし8°傾いた面からなる半導体領域上に接するようにゲート絶縁膜を形成し、減圧CVD法を用いて、ゲート絶縁膜上に接するようにポリシリコンのゲート導電膜を成膜する際、不活性ガスを供給しながら安定化させる目標炉内温度を450℃以上550℃以下にするとともに、原料ガスを注入しながらポリシリコンのゲート導電膜の生成を行う工程、さらには、このゲート導電膜の生成終了後、原料ガスを不活性ガスに置換する工程を含め、炉内温度を一貫してこの目標炉内温度に維持した。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置

【課題】素子面積を増加させることなく、高耐圧の半導体装置を実現させる。

【解決手段】第1方向に沿ったソース領域、ゲート電極を挟んでソース領域とは反対側に第1方向に沿ったドレイン領域、一部がゲート電極下面と対向しソース領域とドレイン領域との間に設けた絶縁体層、一部がゲート電極下面と対向し絶縁体層よりもソース領域側に設けたベース領域、一部が第2方向に第2長さを有してゲート電極下面と対向し、ベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子活性領域部、ゲート絶縁膜の上に設けたゲート電極、ソース領域、一部がゲート電極下面と対向して設けた絶縁体層、一部がゲート電極下面と対向して絶縁体層よりもソース領域側に設けたベース領域、一部が第1方向に第2長さよりも短い第1の長さを有してゲート電極下面と対向してベース領域よりも絶縁体層側に設けたドリフト領域、を有する素子終端領域部と、を備える。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

低マイクロパイプの100mm炭化ケイ素ウェハ

【課題】種結晶を用いた昇華システムにおいて形成された結晶の欠陥レベルが低く、より大きく、高品質のSiC単結晶ウェハを製造する方法を提供する。

【解決手段】少なくとも約100mmの直径と、約25cm−2未満のマイクロパイプ密度とを有し、また、3C、4H、6H、2Hおよび15Rポリタイプからなる群から選択されるポリタイプを有するSiC単結晶ウェハ。なお、マイクロパイプ密度は、表面上にある全マイクロパイプの総数を、ウェハの表面積で割ったものを表す。

(もっと読む)

半導体装置

【課題】ヘテロ接合を有する半導体装置において、リーク電流と電流コラプスのトレードオフ関係を打破し、リーク電流と電流コラプスの双方を抑制すること。

【解決手段】半導体装置1の電子走行層4は、炭素が導入されている高抵抗領域4aを含んでいる。電子走行層4と電子供給層5のヘテロ接合5aと平行な断面において、高抵抗領域4aの炭素の濃度分布が、ドレイン電極12とソース電極18の少なくともいずれか一方の下方で相対的に濃く、ドレイン電極12と絶縁ゲート部16の間で相対的に薄くなるような断面が存在している。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体装置およびその製造方法

【課題】リセスの下部に形成され不純物の注入量が異なる複数の領域を備える電界緩和層(リサーフ層)を備える半導体装置において、製造工程数の増加を抑えつつ、ディッシングの発生を防止する。

【解決手段】半導体装置は、半導体素子の外周領域であるPウェル2の外縁部に形成されたP型のリサーフ層10を備える。リサーフ層10は、P型不純物が第1面密度で注入された第1リサーフ領域11と、第1リサーフ領域11の外側に配設され、P型不純物が第1面密度よりも小さい第2面密度で注入された第2リサーフ領域12と、第2リサーフ領域12の外側に配設され、P型不純物が第2面密度よりも小さい第3面密度で注入された第3リサーフ領域13とを含む。このうち第1リサーフ領域11および第3リサーフ領域13は、半導体層の上面に形成されたリセス11r,13rの下に形成される。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

21 - 40 / 662

[ Back to top ]