Fターム[5F140BA16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | エピタキシャル基板 (980)

Fターム[5F140BA16]の下位に属するFターム

Si基板上に化合物半導体成長 (318)

Fターム[5F140BA16]に分類される特許

41 - 60 / 662

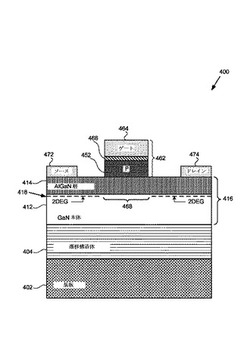

エンハンスメント型III−V族高電子移動度トランジスタ(HEMT)および製造方法

【課題】ノーマリオフ型、すなわちエンハンスメント型トランジスタであるIII族窒化物HEMTを提供する。

【解決手段】エンハンスメント型高電子移動度トランジスタ(HEMT)400はIII−V族半導体412上に位置するIII−V族バリア層414を含むヘテロ接合416、およびIII−V族バリア層414上に形成され、P型III−V族ゲート層452を含むゲート構造462を具える。P型III−V族ゲート層452によりゲート構造462下での2次元電子ガス(2DEG)の発生を防ぐ。エンハンスメント型HEMT400を製造する方法は、基板402を設け、基板402にIII−V族半導体412を形成し、III−V族半導体412上にIII−V族バリア層414を形成し、III−V族バリア層414上にP型III−V族ゲート層452を含むゲート構造462を形成する。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】界面準位密度およびフラットバンド電圧がともに良好な界面特性を有する半導体装置の製造方法を提供すること。

【解決手段】まず、炭化珪素基板1の表面を洗浄する(ステップS1)。つぎに、原料ガスをECRプラズマ化し、原料ガスに含まれる原子を炭化珪素基板1に照射することで、炭化珪素基板1の表面にシリコン窒化膜2を成長させる(ステップS2)。つぎに、ECRプラズマ化学気相成長法により、シリコン窒化膜2の表面にシリコン酸化膜3を堆積する(ステップS3)。つぎに、窒素雰囲気中で、シリコン窒化膜2およびシリコン酸化膜3が形成された炭化珪素基板1のアニール処理を行う(ステップS4)。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

ハイブリッドMOSFETデバイスの製造方法およびそれにより得られるハイブリッドMOSFET

【課題】第1および第2のチャネル材料をそれぞれ有する第1MOSFETと第2MOSFETを含むハイブリッドMOSFETデバイスの製造方法を提供する。

【解決手段】III−Vオン絶縁体スタックは、続いて第1基板に接続される第2基板の上に形成される。III−V層103および絶縁体層は第1領域から選択的に除去されて、これにより第1基板の半導体層が露出する。第1MOSFETの第1ゲートスタック109は第1領域の露出した半導体層上に形成される。第2MOSFETの第2ゲートスタック109’は第2領域のIII−V層の上に形成される。

(もっと読む)

電界効果型トランジスタ

【課題】実用上十分なプロセスマージンを備える状態で、リーク電流の増大およびキャリア濃度の低下を招くことなく、ゲート電極とチャネル層との距離が短縮できるようにする。

【解決手段】InPからなる基板101の上に形成された電子供給層102と、電子供給層102の上に形成されたスペーサ層103と、スペーサ層103の上に形成されたチャネル層104と、チャネル層104の上に形成された障壁層105とを備え、障壁層105は、GaおよびAlの少なくとも1つと、Inと、Pとを含んだアンドープの化合物半導体から構成し、InPよりショットキー障壁高さが高いものとされている。

(もっと読む)

半導体装置

【課題】信頼性が高い半導体装置を提供する。

【解決手段】例えば、ドレイン用の半導体層DF2(n),DF1(n+)およびコンタクト層CNTdと、ソース用の半導体領域DFAおよびコンタクト層と、ソース・ドレイン間に配置されるゲート層GTとを備える。ソース用のコンタクト層は、長辺側に対応する2個のコンタクト層CNTs1,CNTs2で構成され、短辺側に対応する部分には配置されない(C1−C1’間でY軸方向に延伸するコンタクト層は備えない)。また、ドレイン用のCNTdとDF1(n+)の短辺側の間隔X1は、長辺側の間隔Y1よりも例えば3倍以上広い。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置

【課題】低オン抵抗特性を有するパワーMOSトランジスタのスイッチング特性を、従来以上に改善した高効率パワーMOSトランジスタを実現する。

【解決手段】Finger形状電極からなるソース電極8とドレイン電極9の間をFinger形状電極の一方の端部GE1から他方の端部GE2まで延在するゲート電極6と、層間絶縁膜7に形成されたコンタクトホールを介してゲート電極6の端部GE1、GE2とそれぞれ接続されるゲート引き出し電極と、前記層間絶縁膜7上を被覆するパッシベーション膜12と、該パッシベーション膜12の開口に露出する前記ゲート引き出し電極の一部となるゲート接続電極G1、G2と、該ゲート接続電極G1、G2に形成された突起電極25を備える半導体チップ100を、該突起電極25を介して、BGA基板200の表面201に形成された低抵抗のゲート電極シャント用基板配線23に接続する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

高耐圧半導体装置

【課題】容量素子の直列接続を形成するフィールドプレートにおいて、導電性薄膜の間の層間絶縁膜の厚さを増加させても、容量素子による電圧の分圧を均一にできる高耐圧半導体装置を提供する。

【解決手段】本発明の高圧半導体装置は、第1導電型の第1半導体領域と、第1半導体領域と隣接して形成された第2導電型の第2半導体領域と、第2の半導体領域とで第1導電型の第1半導体領域を挟んで形成された、第1導電型の第3半導体領域と、第1半導体領域上に形成された第1絶縁膜上に所定の周期で配列された第1導電膜と、第1導電膜上に形成された第2絶縁膜に、平面視で第1導電膜の離間領域と重なり、かつ当該離間領域の両側に配置されている第1導電膜と一部が重なる位置に周期的に配置されている第2導電膜とを備え、第2導電膜は、第1導電膜の離間領域と対向する領域に第1凸部が設けられている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成し、ドレイン電極と該ソース電極との間にフローティングガードリングを設けることによって、ノーマリ−オフで動作する半導体素子を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間で窒化物半導体層30にショットキー接合されたフローティングガードリング75と、ドレイン電極50とソース電極60との間及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、誘電層40上に形成され、一部が、誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、Vthが高い半導体装置を提供する。

【解決手段】基板102の上方に、III−V族化合物半導体で形成されたバックバリア層106と、バックバリア層106上に、バックバリア層106よりバンドギャップエネルギーが小さいIII−V族化合物半導体で形成され、バックバリア層106の上方の少なくとも一部に設けられたリセス部122において、他の部分より膜厚が薄いチャネル層108と、チャネル層108にオーミック接合された第1の電極116,118と、少なくともリセス部においてチャネル層の上方に形成された第2の電極120と、を備える半導体装置を提供する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低減し、かつ高耐圧で駆動することが可能な半導体装置を提供する。

【解決手段】当該高耐圧トランジスタは、第1の不純物層PEPと、第1の不純物層PEPの内部に形成される第2の不純物層HVNWと、第2の不純物層HVNWを挟むように、第1の不純物層PEPの内部に形成される1対の第3の不純物層OFBおよび第4の不純物層PWと、第3の不純物層OFBから、第2の不純物層HVNWの配置される方向へ、主表面に沿って突出するように、第1の不純物層PEPの最上面から第1の不純物層PEPの内部に形成される第5の不純物層OFB2と、第2の不純物層HVNWの最上面の上方に形成される導電層GEとを備える。第4の不純物層PWにおける不純物濃度は、第3および第5の不純物層OFB,OFB2における不純物濃度よりも高く、第5の不純物層OFB2における不純物濃度は、第3の不純物層OFBにおける不純物濃度よりも高い。

(もっと読む)

半導体装置とその製造方法

【課題】 エッチングによるダメージを抑制しながら、ヘテロ接合面の近傍に負イオンを導入する技術を提供する。

【解決手段】 導入領域8上に保護膜30を形成する保護膜形成工程と、保護膜形成工程の後に、導入領域8を負イオンを含むプラズマに曝すプラズマ工程を備えている。保護膜30は、プラズマに対するエッチング速度が導入領域8よりも小さい。保護膜30には、負イオンを通過させることが可能な材料が用いられている。プラズマ中の負イオンは、保護膜30を通過し、導入領域8に導入される。

(もっと読む)

歪み、反り、及びTTVが少ない75ミリメートル炭化珪素ウェハ

【課題】薄切りしたSiCウェハの歪み、反り、全厚さ変動(TTV)を低減する。

【解決手段】直径が少なくとも約75ミリメートル(3インチ)のSiCブールを、SiCの種結晶使用昇華成長により成長させ、該SiCブールを薄切りにして少なくとも1つのウェハを得る。その後、内層面損傷がウェハの各側において同一となるように、ラッピング下方力を、前記ウェハを折り曲げる下方力未満の量に制限しつつ、SiCウェハをラッピングし、SiCウェハを研磨する。これにより、高品質のSiC単結晶ウェハ16が得られる。該ウェハ16上には複数の窒化物エピタキシャル層18等が形成される。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】3次元形の半導体素子において、オン抵抗をより効果的に低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、ドレイン層と、ドレイン層内に選択的に設けられたドリフト領域と、ドリフト領域内に選択的に設けられたベース領域と、ベース領域内に選択的に設けられたソース領域と、ソース領域又はドレイン層の少なくとも一方の内部に、ソース領域又はドレイン層の少なくとも一方に選択的に設けられた第1,第2の金属層と、ドレイン層の表面に対して略平行な方向に、ソース領域の一部から、ソース領域の少なくとも一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、第1の金属層に接続されたソース電極と、ドレイン層又は第2の金属層に接続されたドレイン電極と、を備える。

(もっと読む)

41 - 60 / 662

[ Back to top ]