Fターム[5F140BD04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782)

Fターム[5F140BD04]の下位に属するFターム

SiO (1,016)

SiN (784)

SiON(酸窒化膜、窒酸化膜を含む) (1,020)

SiN+SiO(多層の場合) (76)

金属酸化膜 (2,702)

少なくとも一部に空間を有するもの (12)

材料の不均一性、不純物分布の不均一性 (188)

複数種構成材料の分布 (62)

Fターム[5F140BD04]に分類される特許

201 - 220 / 922

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

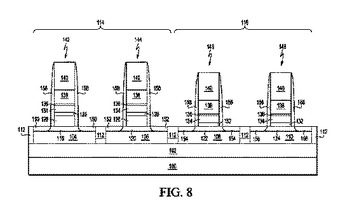

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

ハニカムヘテロエピタキシーを含む半導体装置

【課題】ハニカムヘテロエピタキシーを含む半導体装置を提供する。

【解決手段】ハニカムヘテロエピタキシーを含む半導体装置とその製造方法が開示される。一実施例は、貫通する複数のナノサイズの開口を有するマスクをシリコン基板上に定義するステップと、定義ステップ後、マスク開口を介して露出したシリコン基板表面の一部に、本質的に無欠陥の非シリコン半導体ナノアイランドを作成するステップと、作成ステップ後、ナノアイランド上に、高kゲート誘電体を蒸着するステップと、蒸着ステップ後、ナノアイランド上に、トランジスタを構成するステップとを備える方法である。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

成膜方法及び処理システム

【課題】スループットを高く維持しつつリーク電流を抑制してリーク特性も高く維持することが可能な成膜方法を提供する。

【解決手段】被処理体の表面とゲート電極との間に介在されるゲート絶縁層を形成する成膜方法において、シリコンを含む界面膜を所定の温度で形成する界面膜形成工程S1と、被処理体を冷却する冷却工程S2と、冷却された被処理体に対して界面膜形成工程の所定の温度より低い温度でゲート絶縁膜を形成するゲート絶縁膜形成工程S3とを有する。

(もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用い、PMOS、NMOSそれぞれに適した仕事関数を有するCMOSFETを有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板の主面に素子分離領域によって、絶縁分離されたP型及びN型領域を形成する工程と、前記第P型及びN型領域上にシリコン酸化膜或いはシリコン酸窒化膜からなる第一の絶縁膜を形成する工程と、前記P型領域上の前記第一の絶縁膜上にランタン酸化膜を形成する工程と、前記P型領域上の前記ランタン酸化膜及び前記N型領域上の前記第一の絶縁膜上にハフニウム或いはジルコニウムを含む第二の絶縁膜を形成する工程と、前記第二の絶縁膜上にTixNyとするとx/y<1を満たすチタンナイトライド膜を形成する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTを小さく保ちつつ、より高い実効仕事関数を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101のn型活性領域103の上に形成された第1のゲート絶縁膜107と、第1のゲート絶縁膜107の上に形成された第1のゲート電極111とを有している。第1のゲート絶縁膜107は、ハフニウム及びアルミニウムを含み、且つ中央部において上部及び下部よりもアルミニウムの濃度が高い。第1のゲート電極111はチタンを含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極として窒化チタン膜とシリコン膜の積層膜を用いたときに、窒化チタン膜が消失することを抑制する。

【解決手段】まず基板にゲート絶縁膜を形成する(ステップS10)。次いで、第1の基板温度で成膜処理を行うことにより、ゲート絶縁膜上に結晶化した窒化チタン膜を形成する(ステップS20)。次いで、第1の基板温度より低い第2の基板温度で成膜処理を行うことにより、窒化チタン膜上にシリコン膜を形成する(ステップS30)。次いで、窒化チタン膜及びシリコン膜を選択的に除去することにより、ゲート絶縁膜上に位置するゲート電極を形成する(ステップS40)。

(もっと読む)

高耐圧半導体装置及びその製造方法

【課題】チャネルの閾値調整が容易で、オン抵抗の小さい高耐圧半導体装置及びその製造方法を提供する。

【解決手段】第1導電型であるp型の半導体基板100上に形成された第2導電型であるn型のソース領域200と、半導体基板100の表面から所定の深さまで形成された第2導電型であるn型の電界緩和層300と、電界緩和層300の領域内においてソース領域200から遠い領域の上層領域に形成されたドレイン領域400と、ドレイン領域400とソース領域200の間で半導体基板100の表面の活性領域に形成されたゲート酸化膜500と、ゲート酸化膜500の下のチャネル部550の一部に形成される閾値調整用拡散部555と、ドレイン領域400とゲート酸化膜500の間の半導体層表面に形成されたLOCOS酸化膜600と、ゲート酸化膜500上からLOCOS酸化膜600上に張り出して形成されたゲート電極510と、を有して構成する。

(もっと読む)

高耐圧半導体装置及びその製造方法

【課題】高耐圧と低オン抵抗を両立する高耐圧半導体装置及びその製造方法を提供する。

【解決手段】第1導電型であるp型の半導体基板100上に形成された第2導電型であるn型のソース領域200と、半導体基板100の表面領域に高濃度の第2導電型であるn型で形成された高濃度拡散層310を有し、半導体基板100の表面から高深度領域まで形成された第2導電型であるn型の電界緩和層300と、電界緩和層300の領域内においてソース領域200から遠い領域の上層領域に形成されたドレイン領域400と、ドレイン領域400とソース領域200の間で半導体基板100の表面の活性領域に形成されたゲート酸化膜500と、ドレイン領域400とゲート酸化膜500の間の半導体層表面に形成されたLOCOS酸化膜600と、ゲート酸化膜500上からLOCOS酸化膜600上に張り出して形成されたゲート電極510と、を有して構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の半導体基板上に、高性能な低電圧MISFET、高信頼なMONOS型不揮発性メモリおよび高電圧MISFETを形成する。

【解決手段】ロジック回路などに使用される低電圧MISFETの形成領域において、キャップ酸化膜をマスクにすることによってダミーゲート電極上にシリサイドが形成されるのを防ぎ、ダマシンプロセスを用いて低電圧MISFETのゲートをhigh−k膜18およびメタルゲート電極20で形成する際の形成工程を簡略化する。また、ダミーゲート電極除去時のRIEによりダメージを受けたゲート絶縁膜を一旦除去し、新たにゲート酸化膜17を形成することで素子の信頼性を確保する。

(もっと読む)

III族窒化物系電界効果トランジスタおよびその製造方法

【課題】オン抵抗が低いIII族窒化物系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】本発明のIII族窒化物系電界効果トランジスタは、下地半導体層と、下地半導体層上に第1窒化物半導体層、第2窒化物半導体層、および第3窒化物半導体層が順次積層された窒化物半導体積層体と、ソース電極およびドレイン電極と、第2窒化物半導体層および第3窒化物半導体層が形成されていない領域であるリセス領域と、リセス領域の内面および窒化物半導体積層体の上面に形成された絶縁膜と、絶縁膜上に形成されたゲート電極とを含み、絶縁膜に接する第1窒化物半導体層の上面と、第2窒化物半導体層に接する第1窒化物半導体層の上面とに段差がないことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子の特性や信頼性を向上させることが可能な半導体装置およびその製造方法を提供する。

【解決手段】Hfを含む高誘電率ゲート絶縁膜3上にゲート電極13、14を有する相補型電界効果型トランジスタにおいて、ゲート電極13、14の少なくともゲート絶縁膜3に接する部分は、Ni組成が40%を超えない結晶化したNiシリサイドを主成分とし、pチャネル上のゲート電極14に含まれるNiシリサイドとゲート絶縁膜3との界面にB、Al、Ga、In、Tlの中の少なくともひとつの元素を含み、且つ、nチャネル上のゲート電極13に含まれるNiシリサイドとゲート絶縁膜3との界面にN、P、As、Sb、Biの中の少なくともひとつの元素を含む半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタのゲート絶縁膜の酸化膜換算膜厚の厚膜化を抑制しつつ、p型MISトランジスタの実効仕事関数を増加させて、低閾値電圧を有するn型,p型MISトランジスタを実現する。

【解決手段】半導体装置は、第1,第2のMISトランジスタnTr,pTrを備えている。第1のMISトランジスタnTrは、第1の活性領域10a上に形成され、第1の高誘電率膜14Xaを有する第1のゲート絶縁膜14Aと、第1のゲート電極18Aとを備えている。第2のMISトランジスタpTrは、第2の活性領域10b上に形成され、第2の高誘電率膜14xを有する第2のゲート絶縁膜14Bと、第2のゲート電極18Bとを備えている。第2の高誘電率膜14xは、第1の調整用金属を含む。第1の高誘電率膜14Xaは、第2の高誘電率膜14xよりも窒素濃度が高く、且つ、第1の調整用金属を含まない。

(もっと読む)

半導体装置の製造方法

【課題】金属ゲート電極/高誘電体ゲート絶縁膜構造のMISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1上に、順に、ハフニウムおよび酸素を主体とする高誘電体膜hk1と、第1金属および酸素を主体とし、化学量論的組成よりも多くの第1金属を含むpMIS用キャップ膜Cp1を形成する。その後、シリコン基板1に、第1熱処理と第2熱処理とを順に施す。続いて、pMIS用キャップ膜Cp1上にゲート電極用金属膜EM1を形成し、これらを加工することでpMIS用金属ゲート電極pG1とpMIS用高誘電率ゲート絶縁膜pI1とを形成する。特に、第1熱処理では高誘電体膜hk1中の余剰酸素を除去し、第2熱処理では高誘電体膜hk1中にpMIS用キャップ膜Cp1中の第1金属を拡散させる。第1熱処理は、第2熱処理よりも低い温度で施す。

(もっと読む)

201 - 220 / 922

[ Back to top ]